├── rtl

├── roms

│ ├── boot.rom

│ ├── boot.hex

│ └── boot2.hex

├── sd_debug.qip

├── pll

│ ├── pll_0002.qip

│ ├── pll_0002_q13.qip

│ └── pll_0002.v

├── T80

│ ├── T80.qip

│ ├── README

│ ├── T80_Reg.vhd

│ ├── T80sed.vhd

│ ├── T80s.vhd

│ ├── T80se.vhd

│ ├── GBse.vhd

│ └── T8080se.vhd

├── dpram.sv

├── ce_generator.sv

├── bootrom.txt

├── bleeper.sv

├── edge_det.sv

├── pcw_starter.sv

├── mouse.sv

├── z80_regset.sv

├── amx_mouse.sv

├── kempston_mouse.sv

├── fake_daisy.sv

└── z80_debugger.sv

├── docs

├── images

│ ├── worm.jpg

│ ├── gnome.jpg

│ └── change_disk.jpg

└── Keymatrix.md

├── palette

├── CGA_0_high.GBP

├── CGA_0_low.GBP

├── CGA_1_high.GBP

├── CGA_1_low.GBP

├── BlackRedBlueCyan.GBP

├── BlackGreenBlyeCyan.GBP

├── DBlueBlueOrangeWhite.GBP

├── DBlueBlueWhiteOrange.GBP

├── MagentaBlackBlueYellow.GBP

└── MagentaBlueBlackYellow.GBP

├── releases

├── Amstrad-PCW_20200815.rbf

├── Amstrad-PCW_20200830.rbf

└── Amstrad-PCW_20250621.rbf

├── PCW.sdc

├── sys

├── pll_hdmi

│ ├── pll_hdmi_0002.qip

│ └── pll_hdmi_0002.v

├── pll_q17.qip

├── pll_q13.qip

├── pll_audio

│ ├── pll_audio_0002.qip

│ └── pll_audio_0002.v

├── pll_cfg.qip

├── i2s.v

├── sigma_delta_dac.v

├── pll.13.qip

├── pll_hdmi.13.qip

├── pll_audio.13.qip

├── scanlines.v

├── vga_out.sv

├── mcp23009.sv

├── video_cleaner.sv

├── build_id.tcl

├── math.sv

├── sys_dual_sdram.tcl

├── i2c.v

├── ddr_svc.sv

├── sys.qip

├── sys_analog.tcl

├── video_freezer.sv

├── gamma_corr.sv

├── sys_top.sdc

├── shadowmask.sv

├── ltc2308.sv

├── alsa.sv

├── pll_cfg

│ └── pll_cfg.v

├── scandoubler.v

├── video_mixer.sv

├── audio_out.v

├── iir_filter.v

└── mt32pi.sv

├── .gitignore

├── clean.bat

├── files.qip

├── TODO.md

├── PCW.qpf

├── PCW.srf

└── README.md

/rtl/roms/boot.rom:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/rtl/roms/boot.rom

--------------------------------------------------------------------------------

/docs/images/worm.jpg:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/docs/images/worm.jpg

--------------------------------------------------------------------------------

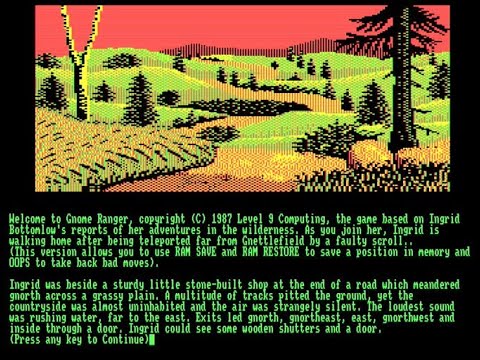

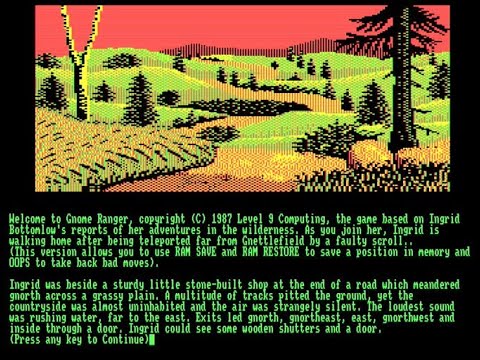

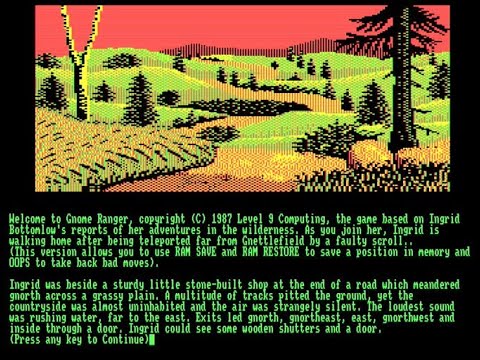

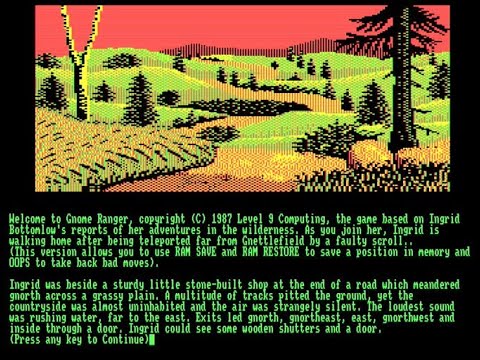

/docs/images/gnome.jpg:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/docs/images/gnome.jpg

--------------------------------------------------------------------------------

/palette/CGA_0_high.GBP:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/palette/CGA_0_high.GBP

--------------------------------------------------------------------------------

/palette/CGA_0_low.GBP:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/palette/CGA_0_low.GBP

--------------------------------------------------------------------------------

/palette/CGA_1_high.GBP:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/palette/CGA_1_high.GBP

--------------------------------------------------------------------------------

/palette/CGA_1_low.GBP:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/palette/CGA_1_low.GBP

--------------------------------------------------------------------------------

/docs/images/change_disk.jpg:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/docs/images/change_disk.jpg

--------------------------------------------------------------------------------

/palette/BlackRedBlueCyan.GBP:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/palette/BlackRedBlueCyan.GBP

--------------------------------------------------------------------------------

/palette/BlackGreenBlyeCyan.GBP:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/palette/BlackGreenBlyeCyan.GBP

--------------------------------------------------------------------------------

/palette/DBlueBlueOrangeWhite.GBP:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/palette/DBlueBlueOrangeWhite.GBP

--------------------------------------------------------------------------------

/palette/DBlueBlueWhiteOrange.GBP:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/palette/DBlueBlueWhiteOrange.GBP

--------------------------------------------------------------------------------

/releases/Amstrad-PCW_20200815.rbf:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/releases/Amstrad-PCW_20200815.rbf

--------------------------------------------------------------------------------

/releases/Amstrad-PCW_20200830.rbf:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/releases/Amstrad-PCW_20200830.rbf

--------------------------------------------------------------------------------

/releases/Amstrad-PCW_20250621.rbf:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/releases/Amstrad-PCW_20250621.rbf

--------------------------------------------------------------------------------

/palette/MagentaBlackBlueYellow.GBP:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/palette/MagentaBlackBlueYellow.GBP

--------------------------------------------------------------------------------

/palette/MagentaBlueBlackYellow.GBP:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/MiSTer-devel/Amstrad-PCW_MiSTer/HEAD/palette/MagentaBlueBlackYellow.GBP

--------------------------------------------------------------------------------

/PCW.sdc:

--------------------------------------------------------------------------------

1 | create_clock -name "CLOCK_50" -period 20.000 [get_ports {CLOCK_50}]

2 | create_clock -name {SPI_SCK} -period 41.666 -waveform { 20.8 41.666 } [get_ports {SPI_SCK}]

3 |

4 | derive_pll_clocks

5 | derive_clock_uncertainty;

6 |

7 |

--------------------------------------------------------------------------------

/sys/pll_hdmi/pll_hdmi_0002.qip:

--------------------------------------------------------------------------------

1 | set_instance_assignment -name PLL_COMPENSATION_MODE DIRECT -to "*pll_hdmi_0002*|altera_pll:altera_pll_i*|*"

2 | set_instance_assignment -name UNFORCE_MERGE_PLL_OUTPUT_COUNTER ON -to "*pll_hdmi_0002*|altera_pll:altera_pll_i*|*"

3 |

--------------------------------------------------------------------------------

/rtl/sd_debug.qip:

--------------------------------------------------------------------------------

1 | set_global_assignment -name IP_TOOL_NAME "RAM: 1-PORT"

2 | set_global_assignment -name IP_TOOL_VERSION "17.0"

3 | set_global_assignment -name IP_GENERATED_DEVICE_FAMILY "{Cyclone V}"

4 | set_global_assignment -name VERILOG_FILE [file join $::quartus(qip_path) "sd_debug.v"]

5 |

--------------------------------------------------------------------------------

/sys/pll_q17.qip:

--------------------------------------------------------------------------------

1 | set_global_assignment -name QIP_FILE rtl/pll.qip

2 | set_global_assignment -name QIP_FILE [file join $::quartus(qip_path) pll_hdmi.qip ]

3 | set_global_assignment -name QIP_FILE [file join $::quartus(qip_path) pll_audio.qip ]

4 | set_global_assignment -name QIP_FILE [file join $::quartus(qip_path) pll_cfg.qip ]

5 |

--------------------------------------------------------------------------------

/sys/pll_q13.qip:

--------------------------------------------------------------------------------

1 | set_global_assignment -name QIP_FILE [file join $::quartus(qip_path) pll.13.qip ]

2 | set_global_assignment -name QIP_FILE [file join $::quartus(qip_path) pll_hdmi.13.qip ]

3 | set_global_assignment -name QIP_FILE [file join $::quartus(qip_path) pll_audio.13.qip ]

4 | set_global_assignment -name QIP_FILE [file join $::quartus(qip_path) pll_cfg.qip ]

5 |

--------------------------------------------------------------------------------

/rtl/pll/pll_0002.qip:

--------------------------------------------------------------------------------

1 | set_instance_assignment -name PLL_COMPENSATION_MODE DIRECT -to "*pll_0002*|altera_pll:altera_pll_i*|*"

2 | set_instance_assignment -name PLL_CHANNEL_SPACING "0.0 KHz" -to "*pll_0002*|altera_pll:altera_pll_i*|*"

3 | set_instance_assignment -name PLL_AUTO_RESET OFF -to "*pll_0002*|altera_pll:altera_pll_i*|*"

4 | set_instance_assignment -name PLL_BANDWIDTH_PRESET AUTO -to "*pll_0002*|altera_pll:altera_pll_i*|*"

5 |

--------------------------------------------------------------------------------

/rtl/pll/pll_0002_q13.qip:

--------------------------------------------------------------------------------

1 | set_instance_assignment -name PLL_COMPENSATION_MODE DIRECT -to "*pll_0002*|altera_pll:altera_pll_i*|*"

2 | set_instance_assignment -name PLL_CHANNEL_SPACING "0.0 KHz" -to "*pll_0002*|altera_pll:altera_pll_i*|*"

3 | set_instance_assignment -name PLL_AUTO_RESET ON -to "*pll_0002*|altera_pll:altera_pll_i*|*"

4 | set_instance_assignment -name PLL_BANDWIDTH_PRESET AUTO -to "*pll_0002*|altera_pll:altera_pll_i*|*"

5 |

--------------------------------------------------------------------------------

/sys/pll_audio/pll_audio_0002.qip:

--------------------------------------------------------------------------------

1 | set_instance_assignment -name PLL_COMPENSATION_MODE DIRECT -to "*pll_audio_0002*|altera_pll:altera_pll_i*|*"

2 | set_instance_assignment -name PLL_CHANNEL_SPACING "0.0 KHz" -to "*pll_audio_0002*|altera_pll:altera_pll_i*|*"

3 | set_instance_assignment -name PLL_AUTO_RESET ON -to "*pll_audio_0002*|altera_pll:altera_pll_i*|*"

4 | set_instance_assignment -name PLL_BANDWIDTH_PRESET AUTO -to "*pll_audio_0002*|altera_pll:altera_pll_i*|*"

5 |

--------------------------------------------------------------------------------

/sys/pll_cfg.qip:

--------------------------------------------------------------------------------

1 | set_global_assignment -name SYNTHESIS_ONLY_QIP ON

2 | set_global_assignment -library "pll_cfg" -name VERILOG_FILE [file join $::quartus(qip_path) "pll_cfg/pll_cfg.v"]

3 | set_global_assignment -library "pll_cfg" -name VERILOG_FILE [file join $::quartus(qip_path) "pll_cfg/pll_cfg_hdmi.v"]

4 | set_global_assignment -library "pll_cfg" -name VERILOG_FILE [file join $::quartus(qip_path) "pll_cfg/altera_pll_reconfig_top.v"]

5 | set_global_assignment -library "pll_cfg" -name VERILOG_FILE [file join $::quartus(qip_path) "pll_cfg/altera_pll_reconfig_core.v"]

6 |

--------------------------------------------------------------------------------

/.gitignore:

--------------------------------------------------------------------------------

1 | db

2 | greybox_tmp

3 | incremental_db

4 | output_files

5 | simulation

6 | hc_output

7 | scaler

8 | hps_isw_handoff

9 | vip

10 | traces

11 | tests

12 | *_sim

13 | .qsys_edit

14 | PLLJ_PLLSPE_INFO.txt

15 | *.bak

16 | *.orig

17 | *.rej

18 | *.qdf

19 | *.rpt

20 | *.smsg

21 | *.summary

22 | *.done

23 | *.jdi

24 | *.pin

25 | *.sof

26 | *.qws

27 | *.ppf

28 | *.ddb

29 | build_id.v

30 | c5_pin_model_dump.txt

31 | *.sopcinfo

32 | *.csv

33 | *.f

34 | *.cmp

35 | *.sip

36 | *.spd

37 | *.bsf

38 | *~

39 | *.xml

40 | *.cdf

41 | *.qarlog

42 | qar_info.json

43 | *.swp

44 |

--------------------------------------------------------------------------------

/rtl/roms/boot.hex:

--------------------------------------------------------------------------------

1 | :20000000C30201F383ED410D78058720F831F0FF3E09D3F811320706C8DCB100CD84001D08

2 | :20002000F217003E80D3F70E090C79D3F80621CDB100CB5120F11520F021F5FF77CB7E28D4

3 | :20004000FC3CD3F81D1D3E06D3F8CDE40009660000000102012AFF2100F0DB008730FB87E2

4 | :20006000F26B00EDA220F37C1F38EF3E05D3F8CDC700E6CBC0472110F0248625862C10F9BA

5 | :200080003C20A0E90E80CDDB0005030FFF0700CDA50006C8381BCD4400CD44000E00CDDBBD

6 | :2000A00000030F0014CDBD0030FB1738F817D806143EB3E3E3E3E33D20F910F5C9DBF8E6BB

7 | :2000C00020C8CDE9000108210201DB008730FB3A0201F0EDA2E3E3E3E318EFDBF8E6402858

8 | :2000E000FA79D3F7CDBD0038FBE34623E30E01E3DB008730FBFAFB007EED7923E3E3E310A3

9 | :13010000EEC9AFD3F00100003ED302033EF802AFC3000002

10 | :00000001FF

11 |

--------------------------------------------------------------------------------

/rtl/roms/boot2.hex:

--------------------------------------------------------------------------------

1 | :020000040000FA

2 | :20000000C30201F383ED410D78058720F831F0FF3E09D3F811320706C8DCB100CD84001D08

3 | :20002000F217003E80D3F70E090C79D3F80621CDB100CB5120F11520F021F5FF77CB7E28D4

4 | :20004000FC3CD3F81D1D3E06D3F8CDE40009660000000102012AFF2100F0DB008730FB87E2

5 | :20006000F26B00EDA220F37C1F38EF3E05D3F8CDC700E6CBC0472110F0248625862C10F9BA

6 | :200080003C20A0E90E80CDDB0005030FFF0700CDA50006C8381BCD4400CD44000E00CDDBBD

7 | :2000A00000030F0014CDBD0030FB1738F817D806143EB3E3E3E3E33D20F910F5C9DBF8E6BB

8 | :2000C00020C8CDE9000108210201DB008730FB3A0201F0EDA2E3E3E3E318EFDBF8E6402858

9 | :2000E000FA79D3F7CDBD0038FBE34623E30E01E3DB008730FBFAFB007EED7923E3E3E310A3

10 | :13010000EEC9AFD3F00100003ED302033EF802AFC3000002

11 | :00000001FF

12 |

--------------------------------------------------------------------------------

/clean.bat:

--------------------------------------------------------------------------------

1 | @echo off

2 | del /s *.bak

3 | del /s *.orig

4 | del /s *.rej

5 | del /s *~

6 | rmdir /s /q db

7 | rmdir /s /q incremental_db

8 | rmdir /s /q output_files

9 | rmdir /s /q simulation

10 | rmdir /s /q greybox_tmp

11 | rmdir /s /q hc_output

12 | rmdir /s /q .qsys_edit

13 | rmdir /s /q hps_isw_handoff

14 | rmdir /s /q sys\.qsys_edit

15 | rmdir /s /q sys\vip

16 | cd sys

17 | for /d %%i in (*_sim) do rmdir /s /q "%%~nxi"

18 | cd ..

19 | for /d %%i in (*_sim) do rmdir /s /q "%%~nxi"

20 | del build_id.v

21 | del c5_pin_model_dump.txt

22 | del PLLJ_PLLSPE_INFO.txt

23 | del /s *.qws

24 | del /s *.ppf

25 | del /s *.ddb

26 | del /s *.csv

27 | del /s *.cmp

28 | del /s *.sip

29 | del /s *.spd

30 | del /s *.bsf

31 | del /s *.f

32 | del /s *.sopcinfo

33 | del /s *.xml

34 | del *.cdf

35 | del /s new_rtl_netlist

36 | del /s old_rtl_netlist

37 | pause

38 |

--------------------------------------------------------------------------------

/sys/i2s.v:

--------------------------------------------------------------------------------

1 |

2 | module i2s

3 | #(

4 | parameter AUDIO_DW = 16

5 | )

6 | (

7 | input reset,

8 | input clk,

9 | input ce,

10 |

11 | output reg sclk,

12 | output reg lrclk,

13 | output reg sdata,

14 |

15 | input [AUDIO_DW-1:0] left_chan,

16 | input [AUDIO_DW-1:0] right_chan

17 | );

18 |

19 | always @(posedge clk) begin

20 | reg [7:0] bit_cnt;

21 | reg msclk;

22 |

23 | reg [AUDIO_DW-1:0] left;

24 | reg [AUDIO_DW-1:0] right;

25 |

26 | if (reset) begin

27 | bit_cnt <= 1;

28 | lrclk <= 1;

29 | sclk <= 1;

30 | msclk <= 1;

31 | end

32 | else begin

33 | sclk <= msclk;

34 | if(ce) begin

35 | msclk <= ~msclk;

36 | if(msclk) begin

37 | if(bit_cnt >= AUDIO_DW) begin

38 | bit_cnt <= 1;

39 | lrclk <= ~lrclk;

40 | if(lrclk) begin

41 | left <= left_chan;

42 | right <= right_chan;

43 | end

44 | end

45 | else begin

46 | bit_cnt <= bit_cnt + 1'd1;

47 | end

48 | sdata <= lrclk ? right[AUDIO_DW - bit_cnt] : left[AUDIO_DW - bit_cnt];

49 | end

50 | end

51 | end

52 | end

53 |

54 | endmodule

55 |

--------------------------------------------------------------------------------

/sys/sigma_delta_dac.v:

--------------------------------------------------------------------------------

1 | //

2 | // PWM DAC

3 | //

4 | // MSBI is the highest bit number. NOT amount of bits!

5 | //

6 | module sigma_delta_dac #(parameter MSBI=7, parameter INV=1'b1)

7 | (

8 | output reg DACout, //Average Output feeding analog lowpass

9 | input [MSBI:0] DACin, //DAC input (excess 2**MSBI)

10 | input CLK,

11 | input RESET

12 | );

13 |

14 | reg [MSBI+2:0] DeltaAdder; //Output of Delta Adder

15 | reg [MSBI+2:0] SigmaAdder; //Output of Sigma Adder

16 | reg [MSBI+2:0] SigmaLatch; //Latches output of Sigma Adder

17 | reg [MSBI+2:0] DeltaB; //B input of Delta Adder

18 |

19 | always @(*) DeltaB = {SigmaLatch[MSBI+2], SigmaLatch[MSBI+2]} << (MSBI+1);

20 | always @(*) DeltaAdder = DACin + DeltaB;

21 | always @(*) SigmaAdder = DeltaAdder + SigmaLatch;

22 |

23 | always @(posedge CLK or posedge RESET) begin

24 | if(RESET) begin

25 | SigmaLatch <= 1'b1 << (MSBI+1);

26 | DACout <= INV;

27 | end else begin

28 | SigmaLatch <= SigmaAdder;

29 | DACout <= SigmaLatch[MSBI+2] ^ INV;

30 | end

31 | end

32 |

33 | endmodule

34 |

--------------------------------------------------------------------------------

/rtl/T80/T80.qip:

--------------------------------------------------------------------------------

1 | set_global_assignment -name VHDL_FILE [file join $::quartus(qip_path) GBse.vhd ]

2 | set_global_assignment -name VHDL_FILE [file join $::quartus(qip_path) T80pa.vhd ]

3 | set_global_assignment -name VHDL_FILE [file join $::quartus(qip_path) T80s.vhd ]

4 | set_global_assignment -name VHDL_FILE [file join $::quartus(qip_path) T80se.vhd ]

5 | set_global_assignment -name VHDL_FILE [file join $::quartus(qip_path) T80a.vhd ]

6 | set_global_assignment -name VHDL_FILE [file join $::quartus(qip_path) T80as.vhd ]

7 | set_global_assignment -name VHDL_FILE [file join $::quartus(qip_path) T80sed.vhd ]

8 | set_global_assignment -name VHDL_FILE [file join $::quartus(qip_path) T8080se.vhd ]

9 | set_global_assignment -name VHDL_FILE [file join $::quartus(qip_path) T80_Reg.vhd ]

10 | set_global_assignment -name VHDL_FILE [file join $::quartus(qip_path) T80_MCode.vhd ]

11 | set_global_assignment -name VHDL_FILE [file join $::quartus(qip_path) T80_ALU.vhd ]

12 | set_global_assignment -name VHDL_FILE [file join $::quartus(qip_path) T80.vhd ]

13 | set_global_assignment -name VHDL_FILE [file join $::quartus(qip_path) T80_Pack.vhd ]

--------------------------------------------------------------------------------

/sys/pll.13.qip:

--------------------------------------------------------------------------------

1 | set_global_assignment -entity "pll" -library "pll" -name IP_TOOL_NAME "altera_pll"

2 | set_global_assignment -entity "pll" -library "pll" -name IP_TOOL_VERSION "13.1"

3 | set_global_assignment -entity "pll" -library "pll" -name IP_TOOL_ENV "mwpim"

4 | set_global_assignment -library "pll" -name MISC_FILE [file join $::quartus(qip_path) "pll.cmp"]

5 | set_global_assignment -name SYNTHESIS_ONLY_QIP ON

6 |

7 | set_global_assignment -library "pll" -name VERILOG_FILE rtl/pll.v

8 | set_global_assignment -library "pll" -name VERILOG_FILE rtl/pll/pll_0002.v

9 |

10 | set_instance_assignment -name PLL_COMPENSATION_MODE DIRECT -to "*pll_0002*|altera_pll:altera_pll_i*|*"

11 | set_instance_assignment -name PLL_CHANNEL_SPACING "0.0 KHz" -to "*pll_0002*|altera_pll:altera_pll_i*|*"

12 | set_instance_assignment -name PLL_AUTO_RESET ON -to "*pll_0002*|altera_pll:altera_pll_i*|*"

13 | set_instance_assignment -name PLL_BANDWIDTH_PRESET AUTO -to "*pll_0002*|altera_pll:altera_pll_i*|*"

14 |

15 | set_global_assignment -entity "pll_0002" -library "pll" -name IP_TOOL_NAME "altera_pll"

16 | set_global_assignment -entity "pll_0002" -library "pll" -name IP_TOOL_VERSION "13.1"

17 | set_global_assignment -entity "pll_0002" -library "pll" -name IP_TOOL_ENV "mwpim"

18 |

--------------------------------------------------------------------------------

/files.qip:

--------------------------------------------------------------------------------

1 | set_global_assignment -name QIP_FILE rtl/T80/T80.qip

2 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/key_joystick.sv

3 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/mouse.sv

4 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/amx_mouse.sv

5 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/kempston_mouse.sv

6 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/dpram.sv

7 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/ym2149.sv

8 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/u765.sv

9 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/boot_loader.sv

10 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/fake_daisy.sv

11 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/z80_regset.sv

12 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/video_controller.sv

13 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/video_sync.sv

14 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/bleeper.sv

15 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/pcw_core.sv

16 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/sdram.sv

17 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/z80_debugger.sv

18 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/sd_debug.v

19 | set_global_assignment -name SYSTEMVERILOG_FILE rtl/edge_det.sv

20 | set_global_assignment -name SYSTEMVERILOG_FILE PCW.sv

21 |

--------------------------------------------------------------------------------

/TODO.md:

--------------------------------------------------------------------------------

1 | # PCW_MiSTer - To Do's:

2 |

3 | * Fixes and features to implement

4 | * Fix top line showing bottom line issue - Done

5 | * Check why resolution is now reporting 1440 x 256 - Fixed

6 | * Create boot from bios on startup - Done

7 | * Fix disk boot issue with fast CPU (ST0=40,ST1=04 in RW_DATA_EXEC3) - Done

8 | * Fix corruption writing at 16x and higher - Done

9 | * Fix Beeper sound - Done

10 | * Add DKTronics joystick and sound support - Done

11 | * Get Mouse support working - AMS Done, Kempston Done, Keymouse Done

12 | * Create fake daisywheel module to boot 3.5" disks - Done

13 | * RAMtest has corrupt screen at start - done

14 | * Find issue with intermittent disk corruption

15 | * Find screen corruption issue with HoE at boot

16 | * Fix Blagger stuck key

17 |

18 |

19 |

20 | * CF2DD support

21 | * Disk 40 - Drive 40 = 1 : 1 Track

22 | * Disk 40 - Drive 80 = 1 : 2 Track

23 | * Disk 80 - Drive 40 = 1 : 1 Track - will error

24 | * Disk 80 - Drive 80 = 1 : 1 Tract

25 | * SENSE_INT_STATE - returns modified cylinder number

26 | * SEEK needs cylinder halving

27 |

28 | * Future features

29 | * Add memory above 128K as SDRAM and options for different memory sizes

30 | * Get multiple drives working

31 |

32 | * Notes

33 | * System timing is 64Mhz clock

34 | * Video clock is 16 Mhz

35 |

36 |

--------------------------------------------------------------------------------

/PCW.qpf:

--------------------------------------------------------------------------------

1 | # -------------------------------------------------------------------------- #

2 | #

3 | # Copyright (C) 2017 Intel Corporation. All rights reserved.

4 | # Your use of Intel Corporation's design tools, logic functions

5 | # and other software and tools, and its AMPP partner logic

6 | # functions, and any output files from any of the foregoing

7 | # (including device programming or simulation files), and any

8 | # associated documentation or information are expressly subject

9 | # to the terms and conditions of the Intel Program License

10 | # Subscription Agreement, the Intel Quartus Prime License Agreement,

11 | # the Intel MegaCore Function License Agreement, or other

12 | # applicable license agreement, including, without limitation,

13 | # that your use is for the sole purpose of programming logic

14 | # devices manufactured by Intel and sold by Intel or its

15 | # authorized distributors. Please refer to the applicable

16 | # agreement for further details.

17 | #

18 | # -------------------------------------------------------------------------- #

19 | #

20 | # Quartus Prime

21 | # Version 17.0.2 Build 602 07/19/2017 SJ Lite Edition

22 | # Date created = 17:03:58 February 06, 2025

23 | #

24 | # -------------------------------------------------------------------------- #

25 |

26 | QUARTUS_VERSION = "17.0"

27 | DATE = "17:03:58 February 06, 2025"

28 |

29 | # Revisions

30 |

31 | PROJECT_REVISION = "PCW"

32 |

--------------------------------------------------------------------------------

/sys/pll_hdmi.13.qip:

--------------------------------------------------------------------------------

1 | set_global_assignment -entity "pll_hdmi" -library "pll_hdmi" -name IP_TOOL_NAME "altera_pll"

2 | set_global_assignment -entity "pll_hdmi" -library "pll_hdmi" -name IP_TOOL_VERSION "13.1"

3 | set_global_assignment -entity "pll_hdmi" -library "pll_hdmi" -name IP_TOOL_ENV "mwpim"

4 | set_global_assignment -library "pll_hdmi" -name MISC_FILE [file join $::quartus(qip_path) "pll_hdmi.cmp"]

5 | set_global_assignment -name SYNTHESIS_ONLY_QIP ON

6 |

7 | set_global_assignment -library "pll_hdmi" -name VERILOG_FILE [file join $::quartus(qip_path) "pll_hdmi.v"]

8 | set_global_assignment -library "pll_hdmi" -name VERILOG_FILE [file join $::quartus(qip_path) "pll_hdmi/pll_hdmi_0002.v"]

9 |

10 | set_instance_assignment -name PLL_COMPENSATION_MODE DIRECT -to "*pll_hdmi_0002*|altera_pll:altera_pll_i*|*"

11 | set_instance_assignment -name PLL_CHANNEL_SPACING "0.0 KHz" -to "*pll_hdmi_0002*|altera_pll:altera_pll_i*|*"

12 | set_instance_assignment -name PLL_AUTO_RESET ON -to "*pll_hdmi_0002*|altera_pll:altera_pll_i*|*"

13 | set_instance_assignment -name PLL_BANDWIDTH_PRESET AUTO -to "*pll_hdmi_0002*|altera_pll:altera_pll_i*|*"

14 |

15 | set_global_assignment -entity "pll_hdmi_0002" -library "pll_hdmi" -name IP_TOOL_NAME "altera_pll"

16 | set_global_assignment -entity "pll_hdmi_0002" -library "pll_hdmi" -name IP_TOOL_VERSION "13.1"

17 | set_global_assignment -entity "pll_hdmi_0002" -library "pll_hdmi" -name IP_TOOL_ENV "mwpim"

18 |

--------------------------------------------------------------------------------

/sys/pll_audio.13.qip:

--------------------------------------------------------------------------------

1 | set_global_assignment -entity "pll_audio" -library "pll_audio" -name IP_TOOL_NAME "altera_pll"

2 | set_global_assignment -entity "pll_audio" -library "pll_audio" -name IP_TOOL_VERSION "13.1"

3 | set_global_assignment -entity "pll_audio" -library "pll_audio" -name IP_TOOL_ENV "mwpim"

4 | set_global_assignment -library "pll_audio" -name MISC_FILE [file join $::quartus(qip_path) "pll_audio.cmp"]

5 | set_global_assignment -name SYNTHESIS_ONLY_QIP ON

6 |

7 | set_global_assignment -library "pll_audio" -name VERILOG_FILE [file join $::quartus(qip_path) "pll_audio.v"]

8 | set_global_assignment -library "pll_audio" -name VERILOG_FILE [file join $::quartus(qip_path) "pll_audio/pll_audio_0002.v"]

9 |

10 | set_instance_assignment -name PLL_COMPENSATION_MODE DIRECT -to "*pll_audio_0002*|altera_pll:altera_pll_i*|*"

11 | set_instance_assignment -name PLL_CHANNEL_SPACING "0.0 KHz" -to "*pll_audio_0002*|altera_pll:altera_pll_i*|*"

12 | set_instance_assignment -name PLL_AUTO_RESET ON -to "*pll_audio_0002*|altera_pll:altera_pll_i*|*"

13 | set_instance_assignment -name PLL_BANDWIDTH_PRESET AUTO -to "*pll_audio_0002*|altera_pll:altera_pll_i*|*"

14 |

15 | set_global_assignment -entity "pll_audio_0002" -library "pll_audio" -name IP_TOOL_NAME "altera_pll"

16 | set_global_assignment -entity "pll_audio_0002" -library "pll_audio" -name IP_TOOL_VERSION "13.1"

17 | set_global_assignment -entity "pll_audio_0002" -library "pll_audio" -name IP_TOOL_ENV "mwpim"

18 |

--------------------------------------------------------------------------------

/sys/scanlines.v:

--------------------------------------------------------------------------------

1 | module scanlines #(parameter v2=0)

2 | (

3 | input clk,

4 |

5 | input [1:0] scanlines,

6 | input [23:0] din,

7 | input hs_in,vs_in,

8 | input de_in,ce_in,

9 |

10 | output reg [23:0] dout,

11 | output reg hs_out,vs_out,

12 | output reg de_out,ce_out

13 | );

14 |

15 | reg [1:0] scanline;

16 | always @(posedge clk) begin

17 | reg old_hs, old_vs;

18 |

19 | old_hs <= hs_in;

20 | old_vs <= vs_in;

21 |

22 | if(old_hs && ~hs_in) begin

23 | if(v2) begin

24 | scanline <= scanline + 1'd1;

25 | if (scanline == scanlines) scanline <= 0;

26 | end

27 | else scanline <= scanline ^ scanlines;

28 | end

29 | if(old_vs && ~vs_in) scanline <= 0;

30 | end

31 |

32 | wire [7:0] r,g,b;

33 | assign {r,g,b} = din;

34 |

35 | reg [23:0] d;

36 | always @(*) begin

37 | case(scanline)

38 | 1: // reduce 25% = 1/2 + 1/4

39 | d = {{1'b0, r[7:1]} + {2'b00, r[7:2]},

40 | {1'b0, g[7:1]} + {2'b00, g[7:2]},

41 | {1'b0, b[7:1]} + {2'b00, b[7:2]}};

42 |

43 | 2: // reduce 50% = 1/2

44 | d = {{1'b0, r[7:1]},

45 | {1'b0, g[7:1]},

46 | {1'b0, b[7:1]}};

47 |

48 | 3: // reduce 75% = 1/4

49 | d = {{2'b00, r[7:2]},

50 | {2'b00, g[7:2]},

51 | {2'b00, b[7:2]}};

52 |

53 | default: d = {r,g,b};

54 | endcase

55 | end

56 |

57 | always @(posedge clk) begin

58 | reg [23:0] dout1, dout2;

59 | reg de1,de2,vs1,vs2,hs1,hs2,ce1,ce2;

60 |

61 | dout <= dout2; dout2 <= dout1; dout1 <= d;

62 | vs_out <= vs2; vs2 <= vs1; vs1 <= vs_in;

63 | hs_out <= hs2; hs2 <= hs1; hs1 <= hs_in;

64 | de_out <= de2; de2 <= de1; de1 <= de_in;

65 | ce_out <= ce2; ce2 <= ce1; ce1 <= ce_in;

66 | end

67 |

68 | endmodule

69 |

--------------------------------------------------------------------------------

/rtl/dpram.sv:

--------------------------------------------------------------------------------

1 | //

2 | // dpram.sv

3 | //

4 | // sdram controller implementation for the MiSTer board by

5 | //

6 | // Copyright (c) 2020 Frank Bruno

7 | //

8 | // This source file is free software: you can redistribute it and/or modify

9 | // it under the terms of the GNU General Public License as published

10 | // by the Free Software Foundation, either version 3 of the License, or

11 | // (at your option) any later version.

12 | //

13 | // This source file is distributed in the hope that it will be useful,

14 | // but WITHOUT ANY WARRANTY; without even the implied warranty of

15 | // MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

16 | // GNU General Public License for more details.

17 | //

18 | // You should have received a copy of the GNU General Public License

19 | // along with this program. If not, see .

20 | //

21 |

22 | module dpram #(

23 | parameter DATA = 72,

24 | parameter ADDR = 10

25 | ) (

26 | // Port A

27 | input wire a_clk,

28 | input wire a_wr,

29 | input wire [ADDR-1:0] a_addr,

30 | input wire [DATA-1:0] a_din,

31 | output logic [DATA-1:0] a_dout,

32 |

33 | // Port B

34 | input wire b_clk,

35 | input wire b_wr,

36 | input wire [ADDR-1:0] b_addr,

37 | input wire [DATA-1:0] b_din,

38 | output logic [DATA-1:0] b_dout

39 | );

40 |

41 | // Shared memory

42 | logic [DATA-1:0] mem [(2**ADDR)-1:0];

43 |

44 | /* initial begin

45 | mem = '{default:'0};

46 | end */

47 |

48 | // Port A

49 | always @(posedge a_clk) begin

50 | a_dout <= mem[a_addr];

51 | if(a_wr) begin

52 | a_dout <= a_din;

53 | mem[a_addr] <= a_din;

54 | end

55 | end

56 |

57 | // Port B

58 | always @(posedge b_clk) begin

59 | b_dout <= mem[b_addr];

60 | if(b_wr) begin

61 | b_dout <= b_din;

62 | mem[b_addr] <= b_din;

63 | end

64 | end

65 |

66 | endmodule

67 |

--------------------------------------------------------------------------------

/rtl/ce_generator.sv:

--------------------------------------------------------------------------------

1 | module ce_generator(

2 | input wire clk,

3 | input wire reset,

4 | input wire [1:0] overclock,

5 | output logic cpu_ce_p,

6 | output logic cpu_ce_n,

7 | output logic sdram_clk_ref,

8 | output logic ce_16mhz,

9 | output logic ce_4mhz,

10 | output logic ce_1mhz,

11 | output logic clk_2mhz

12 | );

13 | reg [5:0] counter;

14 | reg [2:0] div_factor;

15 |

16 | always @(posedge clk or posedge reset) begin

17 | if (reset) counter <= 'b0;

18 | else counter <= counter + 1'b1;

19 | end

20 |

21 | always @(*) begin

22 | case (overclock)

23 | 2'b00: div_factor = 3'd3; // 4 MHz

24 | 2'b01: div_factor = 3'd2; // 8 MHz

25 | 2'b10: div_factor = 3'd1; // 16 MHz

26 | 2'b11: div_factor = 3'd0; // 32 MHz

27 | default: div_factor = 3'd3; // Default to 4 MHz

28 | endcase

29 | end

30 | reg cpu_4mhz_n;

31 | // Generar las señales de habilitación del reloj

32 | assign ce_4mhz = ~counter[3] & ~counter[2] & ~counter[1] & ~counter[0]; // 4MHz positive CE

33 | assign cpu_4mhz_n = counter[3] & ~counter[2] & ~counter[1] & ~counter[0]; // 4MHz negative CE

34 | assign cpu_ce_p = counter[div_factor] == 1'b0; // CE positivo

35 | assign cpu_ce_n = counter[div_factor] == 1'b1; // CE negativo

36 | assign ce_1mhz = ~|counter; // 1MHz

37 | assign ce_16mhz = ~counter[1] & ~counter[0]; // 16MHz

38 |

39 |

40 | assign sdram_clk_ref = cpu_ce_p;

41 |

42 | // Generate 2MHz clock - toggle on every other 4MHz enable pulse

43 | reg clk_2mhz_reg; // Renamed from clk_4mhz_reg

44 | reg toggle_control; // Divider control

45 |

46 | // Create 2 MHz signal (half of 4 MHz)

47 | always @(posedge clk or posedge reset) begin

48 | if (reset) begin

49 | toggle_control <= 1'b0;

50 | clk_2mhz_reg <= 1'b0;

51 | end

52 | else if (ce_4mhz || cpu_4mhz_n) begin

53 | toggle_control <= ~toggle_control;

54 | if (toggle_control) // Only toggle clk_2mhz on every other cpu_ce

55 | clk_2mhz_reg <= ~clk_2mhz_reg;

56 | end

57 | end

58 |

59 | assign clk_2mhz = clk_2mhz_reg;

60 | endmodule

--------------------------------------------------------------------------------

/sys/vga_out.sv:

--------------------------------------------------------------------------------

1 |

2 | module vga_out

3 | (

4 | input clk,

5 | input ypbpr_en,

6 |

7 | input hsync,

8 | input vsync,

9 | input csync,

10 | input de,

11 |

12 | input [23:0] din,

13 | output [23:0] dout,

14 |

15 | output reg hsync_o,

16 | output reg vsync_o,

17 | output reg csync_o,

18 | output reg de_o

19 | );

20 |

21 | wire [7:0] red = din[23:16];

22 | wire [7:0] green = din[15:8];

23 | wire [7:0] blue = din[7:0];

24 |

25 | // http://marsee101.blog19.fc2.com/blog-entry-2311.html

26 |

27 |

28 | // Y = 0.301*R + 0.586*G + 0.113*B (Y = 0.299*R + 0.587*G + 0.114*B)

29 | // Pb = 128 - 0.168*R - 0.332*G + 0.500*B (Pb = -0.169*R - 0.331*G + 0.500*B)

30 | // Pr = 128 + 0.500*R - 0.418*G - 0.082*B (Pr = 0.500*R - 0.419*G - 0.081*B)

31 |

32 | reg [7:0] y, pb, pr;

33 | reg [23:0] rgb;

34 | always @(posedge clk) begin

35 | reg [18:0] y_1r, pb_1r, pr_1r;

36 | reg [18:0] y_1g, pb_1g, pr_1g;

37 | reg [18:0] y_1b, pb_1b, pr_1b;

38 | reg [18:0] y_2, pb_2, pr_2;

39 | reg [23:0] din1, din2;

40 | reg hsync2, vsync2, csync2, de2;

41 | reg hsync1, vsync1, csync1, de1;

42 |

43 | y_1r <= {red, 6'd0} + {red, 3'd0} + {red, 2'd0} + red;

44 | pb_1r <= 19'd32768 - ({red, 5'd0} + {red, 3'd0} + {red, 1'd0});

45 | pr_1r <= 19'd32768 + {red, 7'd0};

46 |

47 | y_1g <= {green, 7'd0} + {green, 4'd0} + {green, 2'd0} + {green, 1'd0};

48 | pb_1g <= {green, 6'd0} + {green, 4'd0} + {green, 2'd0} + green;

49 | pr_1g <= {green, 6'd0} + {green, 5'd0} + {green, 3'd0} + {green, 1'd0};

50 |

51 | y_1b <= {blue, 4'd0} + {blue, 3'd0} + {blue, 2'd0} + blue;

52 | pb_1b <= {blue, 7'd0};

53 | pr_1b <= {blue, 4'd0} + {blue, 2'd0} + blue;

54 |

55 | y_2 <= y_1r + y_1g + y_1b;

56 | pb_2 <= pb_1r - pb_1g + pb_1b;

57 | pr_2 <= pr_1r - pr_1g - pr_1b;

58 |

59 | y <= y_2[18] ? 8'd0 : y_2[16] ? 8'd255 : y_2[15:8];

60 | pb <= pb_2[18] ? 8'd0 : pb_2[16] ? 8'd255 : pb_2[15:8];

61 | pr <= pr_2[18] ? 8'd0 : pr_2[16] ? 8'd255 : pr_2[15:8];

62 |

63 | hsync_o <= hsync2; hsync2 <= hsync1; hsync1 <= hsync;

64 | vsync_o <= vsync2; vsync2 <= vsync1; vsync1 <= vsync;

65 | csync_o <= csync2; csync2 <= csync1; csync1 <= csync;

66 | de_o <= de2; de2 <= de1; de1 <= de;

67 |

68 | rgb <= din2; din2 <= din1; din1 <= din;

69 | end

70 |

71 | assign dout = ypbpr_en ? {pr, y, pb} : rgb;

72 |

73 | endmodule

74 |

--------------------------------------------------------------------------------

/docs/Keymatrix.md:

--------------------------------------------------------------------------------

1 | # Amstrad PCW Keyboard Matrix

2 |

3 | | **Row** | **0** | **1** | **2** | **3** | **4** | **5** | **6** | **7** |

4 | |---------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

5 | | **0** | Keypad 2 | Keypad 3 | Keypad 6 | Keypad 9 | Paste | F1/F2 | Keypad 0 | F3/F4 |

6 | | **1** | Keypad 1 | Keypad 5 | Keypad 4 | Keypad 8 | Copy | Cut | PTR | Exit |

7 | | **2** | [+] | ½ | Shift | Keypad 7 | > | Return | ] | Del-> |

8 | | **3** | . | ? | ; | < | P | [ | - | = |

9 | | **4** | , | M | K | L | I | O | 9 | 0 |

10 | | **5** | Space | N | J | H | Y | U | 7 | 8 |

11 | | **6** | V | B | F | G | T | R | S | 6 |

12 | | **7** | X | C | D | S | W | E | 3 | 4 |

13 | | **8** | Z | Shift Lock | A | Tab | Q | Stop | 2 | 1 |

14 | | **9** | <-Del | | J1 Fire 1 | J1 Fire 2 | J1 Right | J1 Left | J1 Down | J1 Up |

15 | | **A** | Alt | Keypad . | Keypad Enter| F7/F8 | [-] | Cancel | Extra | F5/F6 |

16 | | **B** | | | J2 Fire 1 | J2 Fire 2 | J2 Right | J2 Left | J2 Down | J2 Up |

17 | | **C** | | (KP Enter) | (Space) | (KP 0) | (Exit) | (F1/F2) | (F3/F4) | |

18 | | **C (LK2)** | | (Shift) | (S) | (D) | (A) | (X) | (W) | |

19 | | **D** | ~LK2 | Shift Lock LED | (Space) | (KP 2) | (KP 3) | (KP 1) | (KP .) | (KP 5) |

20 | | **E** | LK3 | LK1 (never set) | (Shift) | (Space) | (W R P ] ; > . ½) | (Q E O [ L < , /) | (Z X C V B N M) | (A S D F G H J) |

21 | | **F** | Update flag | Ticker | (Shift) | (Space) | (W R P ] S F X V) | (Q E O [ A D Z C) | (B N M , . / ½) | (H J K L ; < >) |

22 |

--------------------------------------------------------------------------------

/sys/mcp23009.sv:

--------------------------------------------------------------------------------

1 | //

2 | // MCP23009

3 | // (C) 2019 Alexey Melnikov

4 | //

5 | module mcp23009

6 | (

7 | input clk,

8 |

9 | output reg [2:0] btn,

10 | input [2:0] led,

11 | output reg flg_sd_cd,

12 | output reg flg_present,

13 | output reg flg_mode,

14 |

15 | output scl,

16 | inout sda

17 | );

18 |

19 |

20 | reg start = 0;

21 | wire ready;

22 | wire error;

23 | reg rw;

24 | wire [7:0] dout;

25 | reg [15:0] din;

26 |

27 | i2c #(50_000_000, 500_000) i2c

28 | (

29 | .CLK(clk),

30 | .START(start),

31 | .READ(rw),

32 | .I2C_ADDR('h20),

33 | .I2C_WLEN(1),

34 | .I2C_WDATA1(din[15:8]),

35 | .I2C_WDATA2(din[7:0]),

36 | .I2C_RDATA(dout),

37 | .END(ready),

38 | .ACK(error),

39 | .I2C_SCL(scl),

40 | .I2C_SDA(sda)

41 | );

42 |

43 | always@(posedge clk) begin

44 | reg [3:0] idx = 0;

45 | reg [1:0] state = 0;

46 | reg [15:0] timeout = 0;

47 |

48 | if(~&timeout) begin

49 | timeout <= timeout + 1'd1;

50 | start <= 0;

51 | state <= 0;

52 | idx <= 0;

53 | btn <= 0;

54 | rw <= 0;

55 | flg_sd_cd <= 1;

56 | flg_present <= 0;

57 | flg_mode <= 1;

58 | end

59 | else begin

60 | if(~&init_data[idx]) begin

61 | case(state)

62 | 0: begin

63 | start <= 1;

64 | state <= 1;

65 | din <= init_data[idx];

66 | end

67 | 1: if(~ready) state <= 2;

68 | 2: begin

69 | start <= 0;

70 | if(ready) begin

71 | state <= 0;

72 | if(!error) idx <= idx + 1'd1;

73 | end

74 | end

75 | endcase

76 | end

77 | else begin

78 | case(state)

79 | 0: begin

80 | start <= 1;

81 | state <= 1;

82 | din <= {8'h09,5'b00000,led};

83 | end

84 | 1: if(~ready) state <= 2;

85 | 2: begin

86 | start <= 0;

87 | if(ready) begin

88 | state <= 0;

89 | rw <= 0;

90 | if(!error) begin

91 | if(rw) begin

92 | {flg_sd_cd, flg_mode, btn} <= {dout[7:3]};

93 | flg_present <= 1;

94 | end

95 | rw <= ~rw;

96 | end

97 | end

98 | end

99 | endcase

100 | end

101 | end

102 | end

103 |

104 | wire [15:0] init_data[12] =

105 | '{

106 | 16'h00F8,

107 | 16'h0138,

108 | 16'h0200,

109 | 16'h0300,

110 | 16'h0400,

111 | 16'h0524,

112 | 16'h06FF,

113 | 16'h0700,

114 | 16'h0800,

115 | 16'h0900,

116 | 16'h0A00,

117 | 16'hFFFF

118 | };

119 |

120 | endmodule

121 |

--------------------------------------------------------------------------------

/sys/video_cleaner.sv:

--------------------------------------------------------------------------------

1 | //

2 | //

3 | // Copyright (c) 2018 Sorgelig

4 | //

5 | // This program is GPL Licensed. See COPYING for the full license.

6 | //

7 | //

8 | ////////////////////////////////////////////////////////////////////////////////////////////////////////

9 |

10 | `timescale 1ns / 1ps

11 |

12 | module video_cleaner

13 | (

14 | input clk_vid,

15 | input ce_pix,

16 |

17 | input [7:0] R,

18 | input [7:0] G,

19 | input [7:0] B,

20 |

21 | input HSync,

22 | input VSync,

23 | input HBlank,

24 | input VBlank,

25 |

26 | //optional de

27 | input DE_in,

28 |

29 | //optional interlace support

30 | input interlace,

31 | input f1,

32 |

33 | // video output signals

34 | output reg [7:0] VGA_R,

35 | output reg [7:0] VGA_G,

36 | output reg [7:0] VGA_B,

37 | output reg VGA_VS,

38 | output reg VGA_HS,

39 | output VGA_DE,

40 |

41 | // optional aligned blank

42 | output reg HBlank_out,

43 | output reg VBlank_out,

44 |

45 | // optional aligned de

46 | output reg DE_out

47 | );

48 |

49 | wire hs, vs;

50 | s_fix sync_v(clk_vid, HSync, hs);

51 | s_fix sync_h(clk_vid, VSync, vs);

52 |

53 | wire hbl = hs | HBlank;

54 | wire vbl = vs | VBlank;

55 |

56 | assign VGA_DE = ~(HBlank_out | VBlank_out);

57 |

58 | always @(posedge clk_vid) begin

59 | if(ce_pix) begin

60 | HBlank_out <= hbl;

61 |

62 | VGA_HS <= hs;

63 |

64 | VGA_R <= R;

65 | VGA_G <= G;

66 | VGA_B <= B;

67 | DE_out <= DE_in;

68 |

69 | if (interlace & f1) begin

70 | VGA_VS <= vs;

71 | VBlank_out <= vbl;

72 | end else begin

73 | if(~VGA_HS & hs) VGA_VS <= vs;

74 | if(HBlank_out & ~hbl) VBlank_out <= vbl;

75 | end

76 | end

77 | end

78 |

79 | endmodule

80 |

81 | module s_fix

82 | (

83 | input clk,

84 |

85 | input sync_in,

86 | output sync_out

87 | );

88 |

89 | assign sync_out = sync_in ^ pol;

90 |

91 | reg pol;

92 | always @(posedge clk) begin

93 | integer pos = 0, neg = 0, cnt = 0;

94 | reg s1,s2;

95 |

96 | s1 <= sync_in;

97 | s2 <= s1;

98 |

99 | if(~s2 & s1) neg <= cnt;

100 | if(s2 & ~s1) pos <= cnt;

101 |

102 | cnt <= cnt + 1;

103 | if(s2 != s1) cnt <= 0;

104 |

105 | pol <= pos > neg;

106 | end

107 |

108 | endmodule

109 |

--------------------------------------------------------------------------------

/sys/build_id.tcl:

--------------------------------------------------------------------------------

1 |

2 | # Build TimeStamp Verilog Module

3 | # Jeff Wiencrot - 8/1/2011

4 | # Sorgelig - 02/11/2019

5 | proc generateBuildID_Verilog {} {

6 |

7 | # Get the timestamp (see: http://www.altera.com/support/examples/tcl/tcl-date-time-stamp.html)

8 | set buildDate "`define BUILD_DATE \"[clock format [ clock seconds ] -format %y%m%d]\""

9 |

10 | # Create a Verilog file for output

11 | set outputFileName "build_id.v"

12 |

13 | set fileData ""

14 | if { [file exists $outputFileName]} {

15 | set outputFile [open $outputFileName "r"]

16 | set fileData [read $outputFile]

17 | close $outputFile

18 | }

19 |

20 | if {$buildDate ne $fileData} {

21 | set outputFile [open $outputFileName "w"]

22 | puts -nonewline $outputFile $buildDate

23 | close $outputFile

24 | # Send confirmation message to the Messages window

25 | post_message "Generated: [pwd]/$outputFileName: $buildDate"

26 | }

27 | }

28 |

29 | # Build CDF file

30 | # Sorgelig - 17/2/2018

31 | proc generateCDF {revision device outpath} {

32 |

33 | set outputFileName "jtag.cdf"

34 | set outputFile [open $outputFileName "w"]

35 |

36 | puts $outputFile "JedecChain;"

37 | puts $outputFile " FileRevision(JESD32A);"

38 | puts $outputFile " DefaultMfr(6E);"

39 | puts $outputFile ""

40 | puts $outputFile " P ActionCode(Ign)"

41 | puts $outputFile " Device PartName(SOCVHPS) MfrSpec(OpMask(0));"

42 | puts $outputFile " P ActionCode(Cfg)"

43 | puts $outputFile " Device PartName($device) Path(\"$outpath/\") File(\"$revision.sof\") MfrSpec(OpMask(1));"

44 | puts $outputFile "ChainEnd;"

45 | puts $outputFile ""

46 | puts $outputFile "AlteraBegin;"

47 | puts $outputFile " ChainType(JTAG);"

48 | puts $outputFile "AlteraEnd;"

49 | }

50 |

51 | set project_name [lindex $quartus(args) 1]

52 | set revision [lindex $quartus(args) 2]

53 |

54 | if {[project_exists $project_name]} {

55 | if {[string equal "" $revision]} {

56 | project_open $project_name -revision [get_current_revision $project_name]

57 | } else {

58 | project_open $project_name -revision $revision

59 | }

60 | } else {

61 | post_message -type error "Project $project_name does not exist"

62 | exit

63 | }

64 |

65 | set device [get_global_assignment -name DEVICE]

66 | set outpath [get_global_assignment -name PROJECT_OUTPUT_DIRECTORY]

67 |

68 | if [is_project_open] {

69 | project_close

70 | }

71 |

72 | generateBuildID_Verilog

73 | generateCDF $revision $device $outpath

74 |

--------------------------------------------------------------------------------

/rtl/bootrom.txt:

--------------------------------------------------------------------------------

1 | AF

2 | D3

3 | 01

4 | F3

5 | 83

6 | ED

7 | 41

8 | 0D

9 | 78

10 | 05

11 | 87

12 | 20

13 | F8

14 | 31

15 | F0

16 | FF

17 | 3E

18 | 09

19 | D3

20 | F8

21 | 11

22 | 32

23 | 07

24 | 06

25 | C8

26 | DC

27 | B1

28 | 00

29 | CD

30 | 84

31 | 00

32 | 1D

33 | F2

34 | 17

35 | 00

36 | 3E

37 | 80

38 | D3

39 | F7

40 | 0E

41 | 09

42 | 0C

43 | 79

44 | D3

45 | F8

46 | 06

47 | 21

48 | CD

49 | B1

50 | 00

51 | CB

52 | 51

53 | 20

54 | F1

55 | 15

56 | 20

57 | F0

58 | 21

59 | F5

60 | FF

61 | 77

62 | CB

63 | 7E

64 | 28

65 | FC

66 | 3C

67 | D3

68 | F8

69 | 1D

70 | 1D

71 | 3E

72 | 06

73 | D3

74 | F8

75 | CD

76 | E4

77 | 00

78 | 09

79 | 66

80 | 00

81 | 00

82 | 00

83 | 01

84 | 02

85 | 01

86 | 2A

87 | FF

88 | 21

89 | 00

90 | F0

91 | DB

92 | 00

93 | 87

94 | 30

95 | FB

96 | 87

97 | F2

98 | 6B

99 | 00

100 | ED

101 | A2

102 | 20

103 | F3

104 | 7C

105 | 1F

106 | 38

107 | EF

108 | 3E

109 | 05

110 | D3

111 | F8

112 | CD

113 | C7

114 | 00

115 | E6

116 | CB

117 | C0

118 | 47

119 | 21

120 | 10

121 | F0

122 | 24

123 | 86

124 | 25

125 | 86

126 | 2C

127 | 10

128 | F9

129 | 3C

130 | 20

131 | A0

132 | E9

133 | 0E

134 | 80

135 | CD

136 | DB

137 | 00

138 | 05

139 | 03

140 | 0F

141 | FF

142 | 07

143 | 00

144 | CD

145 | A5

146 | 00

147 | 06

148 | C8

149 | 38

150 | 1B

151 | CD

152 | 44

153 | 00

154 | CD

155 | 44

156 | 00

157 | 0E

158 | 00

159 | CD

160 | DB

161 | 00

162 | 03

163 | 0F

164 | 00

165 | 14

166 | CD

167 | BD

168 | 00

169 | 30

170 | FB

171 | 17

172 | 38

173 | F8

174 | 17

175 | D8

176 | 06

177 | 14

178 | 3E

179 | B3

180 | E3

181 | E3

182 | E3

183 | E3

184 | 3D

185 | 20

186 | F9

187 | 10

188 | F5

189 | C9

190 | DB

191 | F8

192 | E6

193 | 20

194 | C8

195 | CD

196 | E9

197 | 00

198 | 01

199 | 08

200 | 21

201 | 02

202 | 01

203 | DB

204 | 00

205 | 87

206 | 30

207 | FB

208 | 3A

209 | 02

210 | 01

211 | F0

212 | ED

213 | A2

214 | E3

215 | E3

216 | E3

217 | E3

218 | 18

219 | EF

220 | DB

221 | F8

222 | E6

223 | 40

224 | 28

225 | FA

226 | 79

227 | D3

228 | F7

229 | CD

230 | BD

231 | 00

232 | 38

233 | FB

234 | E3

235 | 46

236 | 23

237 | E3

238 | 0E

239 | 01

240 | E3

241 | DB

242 | 00

243 | 87

244 | 30

245 | FB

246 | FA

247 | FB

248 | 00

249 | 7E

250 | ED

251 | 79

252 | 23

253 | E3

254 | E3

255 | E3

256 | 10

257 | EE

258 | C9

--------------------------------------------------------------------------------

/rtl/pll/pll_0002.v:

--------------------------------------------------------------------------------

1 | `timescale 1ns/10ps

2 | module pll_0002(

3 |

4 | // interface 'refclk'

5 | input wire refclk,

6 |

7 | // interface 'reset'

8 | input wire rst,

9 |

10 | // interface 'outclk0'

11 | output wire outclk_0,

12 |

13 | // interface 'locked'

14 | output wire locked

15 | );

16 |

17 | altera_pll #(

18 | .fractional_vco_multiplier("true"),

19 | .reference_clock_frequency("50.0 MHz"),

20 | .operation_mode("direct"),

21 | .number_of_clocks(1),

22 | .output_clock_frequency0("64.000000 MHz"),

23 | .phase_shift0("0 ps"),

24 | .duty_cycle0(50),

25 | .output_clock_frequency1("0 MHz"),

26 | .phase_shift1("0 ps"),

27 | .duty_cycle1(50),

28 | .output_clock_frequency2("0 MHz"),

29 | .phase_shift2("0 ps"),

30 | .duty_cycle2(50),

31 | .output_clock_frequency3("0 MHz"),

32 | .phase_shift3("0 ps"),

33 | .duty_cycle3(50),

34 | .output_clock_frequency4("0 MHz"),

35 | .phase_shift4("0 ps"),

36 | .duty_cycle4(50),

37 | .output_clock_frequency5("0 MHz"),

38 | .phase_shift5("0 ps"),

39 | .duty_cycle5(50),

40 | .output_clock_frequency6("0 MHz"),

41 | .phase_shift6("0 ps"),

42 | .duty_cycle6(50),

43 | .output_clock_frequency7("0 MHz"),

44 | .phase_shift7("0 ps"),

45 | .duty_cycle7(50),

46 | .output_clock_frequency8("0 MHz"),

47 | .phase_shift8("0 ps"),

48 | .duty_cycle8(50),

49 | .output_clock_frequency9("0 MHz"),

50 | .phase_shift9("0 ps"),

51 | .duty_cycle9(50),

52 | .output_clock_frequency10("0 MHz"),

53 | .phase_shift10("0 ps"),

54 | .duty_cycle10(50),

55 | .output_clock_frequency11("0 MHz"),

56 | .phase_shift11("0 ps"),

57 | .duty_cycle11(50),

58 | .output_clock_frequency12("0 MHz"),

59 | .phase_shift12("0 ps"),

60 | .duty_cycle12(50),

61 | .output_clock_frequency13("0 MHz"),

62 | .phase_shift13("0 ps"),

63 | .duty_cycle13(50),

64 | .output_clock_frequency14("0 MHz"),

65 | .phase_shift14("0 ps"),

66 | .duty_cycle14(50),

67 | .output_clock_frequency15("0 MHz"),

68 | .phase_shift15("0 ps"),

69 | .duty_cycle15(50),

70 | .output_clock_frequency16("0 MHz"),

71 | .phase_shift16("0 ps"),

72 | .duty_cycle16(50),

73 | .output_clock_frequency17("0 MHz"),

74 | .phase_shift17("0 ps"),

75 | .duty_cycle17(50),

76 | .pll_type("General"),

77 | .pll_subtype("General")

78 | ) altera_pll_i (

79 | .rst (rst),

80 | .outclk ({outclk_0}),

81 | .locked (locked),

82 | .fboutclk ( ),

83 | .fbclk (1'b0),

84 | .refclk (refclk)

85 | );

86 | endmodule

87 |

88 |

--------------------------------------------------------------------------------

/sys/math.sv:

--------------------------------------------------------------------------------

1 |

2 | // result = num/div

3 | module sys_udiv

4 | #(

5 | parameter NB_NUM,

6 | parameter NB_DIV

7 | )

8 | (

9 | input clk,

10 | input start,

11 | output busy,

12 |

13 | input [NB_NUM-1:0] num,

14 | input [NB_DIV-1:0] div,

15 | output reg [NB_NUM-1:0] result,

16 | output reg [NB_DIV-1:0] remainder

17 | );

18 |

19 | reg run;

20 | assign busy = run;

21 |

22 | always @(posedge clk) begin

23 | reg [5:0] cpt;

24 | reg [NB_NUM+NB_DIV+1:0] rem;

25 |

26 | if (start) begin

27 | cpt <= 0;

28 | run <= 1;

29 | rem <= num;

30 | end

31 | else if (run) begin

32 | cpt <= cpt + 1'd1;

33 | run <= (cpt != NB_NUM + 1'd1);

34 | remainder <= rem[NB_NUM+NB_DIV:NB_NUM+1];

35 | if (!rem[NB_DIV + NB_NUM + 1'd1])

36 | rem <= {rem[NB_DIV+NB_NUM:0] - (div << NB_NUM),1'b0};

37 | else

38 | rem <= {rem[NB_DIV+NB_NUM:0] + (div << NB_NUM),1'b0};

39 | result <= {result[NB_NUM-2:0], !rem[NB_DIV + NB_NUM + 1'd1]};

40 | end

41 | end

42 |

43 | endmodule

44 |

45 | // result = mul1*mul2

46 | module sys_umul

47 | #(

48 | parameter NB_MUL1,

49 | parameter NB_MUL2

50 | )

51 | (

52 | input clk,

53 | input start,

54 | output busy,

55 |

56 | input [NB_MUL1-1:0] mul1,

57 | input [NB_MUL2-1:0] mul2,

58 | output reg [NB_MUL1+NB_MUL2-1:0] result

59 | );

60 |

61 | reg run;

62 | assign busy = run;

63 |

64 | always @(posedge clk) begin

65 | reg [NB_MUL1+NB_MUL2-1:0] add;

66 | reg [NB_MUL2-1:0] map;

67 |

68 | if (start) begin

69 | run <= 1;

70 | result <= 0;

71 | add <= mul1;

72 | map <= mul2;

73 | end

74 | else if (run) begin

75 | if(!map) run <= 0;

76 | if(map[0]) result <= result + add;

77 | add <= add << 1;

78 | map <= map >> 1;

79 | end

80 | end

81 |

82 | endmodule

83 |

84 | // result = (mul1*mul2)/div

85 | module sys_umuldiv

86 | #(

87 | parameter NB_MUL1,

88 | parameter NB_MUL2,

89 | parameter NB_DIV

90 | )

91 | (

92 | input clk,

93 | input start,

94 | output busy,

95 |

96 | input [NB_MUL1-1:0] mul1,

97 | input [NB_MUL2-1:0] mul2,

98 | input [NB_DIV-1:0] div,

99 | output [NB_MUL1+NB_MUL2-1:0] result,

100 | output [NB_DIV-1:0] remainder

101 | );

102 |

103 | wire mul_run;

104 | wire [NB_MUL1+NB_MUL2-1:0] mul_res;

105 | sys_umul #(NB_MUL1,NB_MUL2) umul(clk,start,mul_run,mul1,mul2,mul_res);

106 |

107 | sys_udiv #(NB_MUL1+NB_MUL2,NB_DIV) udiv(clk,start|mul_run,busy,mul_res,div,result,remainder);

108 |

109 | endmodule

110 |

--------------------------------------------------------------------------------

/sys/pll_audio/pll_audio_0002.v:

--------------------------------------------------------------------------------

1 | `timescale 1ns/10ps

2 | module pll_audio_0002(

3 |

4 | // interface 'refclk'

5 | input wire refclk,

6 |

7 | // interface 'reset'

8 | input wire rst,

9 |

10 | // interface 'outclk0'

11 | output wire outclk_0,

12 |

13 | // interface 'locked'

14 | output wire locked

15 | );

16 |

17 | altera_pll #(

18 | .fractional_vco_multiplier("true"),

19 | .reference_clock_frequency("50.0 MHz"),

20 | .operation_mode("direct"),

21 | .number_of_clocks(1),

22 | .output_clock_frequency0("24.576000 MHz"),

23 | .phase_shift0("0 ps"),

24 | .duty_cycle0(50),

25 | .output_clock_frequency1("0 MHz"),

26 | .phase_shift1("0 ps"),

27 | .duty_cycle1(50),

28 | .output_clock_frequency2("0 MHz"),

29 | .phase_shift2("0 ps"),

30 | .duty_cycle2(50),

31 | .output_clock_frequency3("0 MHz"),

32 | .phase_shift3("0 ps"),

33 | .duty_cycle3(50),

34 | .output_clock_frequency4("0 MHz"),

35 | .phase_shift4("0 ps"),

36 | .duty_cycle4(50),

37 | .output_clock_frequency5("0 MHz"),

38 | .phase_shift5("0 ps"),

39 | .duty_cycle5(50),

40 | .output_clock_frequency6("0 MHz"),

41 | .phase_shift6("0 ps"),

42 | .duty_cycle6(50),

43 | .output_clock_frequency7("0 MHz"),

44 | .phase_shift7("0 ps"),

45 | .duty_cycle7(50),

46 | .output_clock_frequency8("0 MHz"),

47 | .phase_shift8("0 ps"),

48 | .duty_cycle8(50),

49 | .output_clock_frequency9("0 MHz"),

50 | .phase_shift9("0 ps"),

51 | .duty_cycle9(50),

52 | .output_clock_frequency10("0 MHz"),

53 | .phase_shift10("0 ps"),

54 | .duty_cycle10(50),

55 | .output_clock_frequency11("0 MHz"),

56 | .phase_shift11("0 ps"),

57 | .duty_cycle11(50),

58 | .output_clock_frequency12("0 MHz"),

59 | .phase_shift12("0 ps"),

60 | .duty_cycle12(50),

61 | .output_clock_frequency13("0 MHz"),

62 | .phase_shift13("0 ps"),

63 | .duty_cycle13(50),

64 | .output_clock_frequency14("0 MHz"),

65 | .phase_shift14("0 ps"),

66 | .duty_cycle14(50),

67 | .output_clock_frequency15("0 MHz"),

68 | .phase_shift15("0 ps"),

69 | .duty_cycle15(50),

70 | .output_clock_frequency16("0 MHz"),

71 | .phase_shift16("0 ps"),

72 | .duty_cycle16(50),

73 | .output_clock_frequency17("0 MHz"),

74 | .phase_shift17("0 ps"),

75 | .duty_cycle17(50),

76 | .pll_type("General"),

77 | .pll_subtype("General")

78 | ) altera_pll_i (

79 | .rst (rst),

80 | .outclk ({outclk_0}),

81 | .locked (locked),

82 | .fboutclk ( ),

83 | .fbclk (1'b0),

84 | .refclk (refclk)

85 | );

86 | endmodule

87 |

88 |

--------------------------------------------------------------------------------

/rtl/bleeper.sv:

--------------------------------------------------------------------------------

1 | //

2 | // Bleeper simulator

3 | //

4 | // Copyright (c) 2020 Stephen Eddy

5 | //

6 | // All rights reserved

7 | //

8 | // Redistribution and use in source and synthezised forms, with or without

9 | // modification, are permitted provided that the following conditions are met:

10 | //

11 | // * Redistributions of source code must retain the above copyright notice,

12 | // this list of conditions and the following disclaimer.

13 | //

14 | // * Redistributions in synthesized form must reproduce the above copyright

15 | // notice, this list of conditions and the following disclaimer in the

16 | // documentation and/or other materials provided with the distribution.

17 | //

18 | // * Neither the name of the author nor the names of other contributors may

19 | // be used to endorse or promote products derived from this software without

20 | // specific prior written agreement from the author.

21 | //

22 | // * License is granted for non-commercial use only. A fee may not be charged

23 | // for redistributions as source code or in synthesized/hardware form without

24 | // specific prior written agreement from the author.

25 | //

26 | // THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

27 | // AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO,

28 | // THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR

29 | // PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE AUTHOR OR CONTRIBUTORS BE

30 | // LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR

31 | // CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF

32 | // SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS

33 | // INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN

34 | // CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE)

35 | // ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE

36 | // POSSIBILITY OF SUCH DAMAGE.

37 |

38 | module bleeper(

39 | input wire clk_sys,

40 | input wire ce,

41 | output logic speaker

42 | );

43 |

44 | parameter bit[19:0] clkdivider = (64000000/4000)/2;

45 |

46 | logic [19:0] cnt = 'd0;

47 | reg sq_wave = 1'b0;

48 |

49 | assign speaker = sq_wave;

50 |

51 | always @(posedge clk_sys)

52 | begin

53 | if(ce)

54 | begin

55 | if(cnt == 'd0) begin

56 | sq_wave <= ~sq_wave;

57 | cnt = clkdivider;

58 | end

59 | else cnt <= cnt - 'd1;

60 | end

61 | end

62 |

63 | endmodule

--------------------------------------------------------------------------------

/rtl/edge_det.sv:

--------------------------------------------------------------------------------

1 | //

2 | // Simple edge detector

3 | //

4 | // Copyright (c) 2020 Stephen Eddy

5 | //

6 | // All rights reserved

7 | //

8 | // Redistribution and use in source and synthezised forms, with or without

9 | // modification, are permitted provided that the following conditions are met:

10 | //

11 | // * Redistributions of source code must retain the above copyright notice,

12 | // this list of conditions and the following disclaimer.

13 | //

14 | // * Redistributions in synthesized form must reproduce the above copyright

15 | // notice, this list of conditions and the following disclaimer in the

16 | // documentation and/or other materials provided with the distribution.

17 | //

18 | // * Neither the name of the author nor the names of other contributors may

19 | // be used to endorse or promote products derived from this software without

20 | // specific prior written agreement from the author.

21 | //

22 | // * License is granted for non-commercial use only. A fee may not be charged

23 | // for redistributions as source code or in synthesized/hardware form without

24 | // specific prior written agreement from the author.

25 | //

26 | // THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

27 | // AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO,

28 | // THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR

29 | // PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE AUTHOR OR CONTRIBUTORS BE

30 | // LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR

31 | // CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF

32 | // SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS

33 | // INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN

34 | // CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE)

35 | // ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE

36 | // POSSIBILITY OF SUCH DAMAGE.

37 |

38 |

39 | module edge_det(clk_sys, signal, pos_edge, neg_edge);

40 | input wire clk_sys;

41 | input wire signal;

42 | output logic pos_edge, neg_edge;

43 |

44 | logic old_edge;

45 | always @(posedge clk_sys)

46 | begin

47 | old_edge <= signal;

48 | if(~old_edge & signal)

49 | begin

50 | pos_edge <= 1'b1;

51 | neg_edge <= 1'b0;

52 | end

53 | else if(old_edge & ~signal)

54 | begin

55 | pos_edge <= 1'b0;

56 | neg_edge <= 1'b1;

57 | end

58 | else begin

59 | pos_edge <= 1'b0;

60 | neg_edge <= 1'b0;

61 | end

62 | end

63 |

64 | endmodule

--------------------------------------------------------------------------------

/sys/sys_dual_sdram.tcl:

--------------------------------------------------------------------------------

1 | #============================================================

2 | # Secondary SDRAM

3 | #============================================================

4 | set_location_assignment PIN_Y15 -to SDRAM2_DQ[0]

5 | set_location_assignment PIN_AC24 -to SDRAM2_DQ[1]

6 | set_location_assignment PIN_AA15 -to SDRAM2_DQ[2]

7 | set_location_assignment PIN_AD26 -to SDRAM2_DQ[3]

8 | set_location_assignment PIN_AG28 -to SDRAM2_DQ[4]

9 | set_location_assignment PIN_AF28 -to SDRAM2_DQ[5]

10 | set_location_assignment PIN_AE25 -to SDRAM2_DQ[6]

11 | set_location_assignment PIN_AF27 -to SDRAM2_DQ[7]

12 | set_location_assignment PIN_AG26 -to SDRAM2_DQ[14]

13 | set_location_assignment PIN_AH27 -to SDRAM2_DQ[15]

14 |

15 | set_location_assignment PIN_AG25 -to SDRAM2_DQ[13]

16 | set_location_assignment PIN_AH26 -to SDRAM2_DQ[12]

17 | set_location_assignment PIN_AH24 -to SDRAM2_DQ[11]

18 | set_location_assignment PIN_AF25 -to SDRAM2_DQ[10]

19 | set_location_assignment PIN_AG23 -to SDRAM2_DQ[9]

20 | set_location_assignment PIN_AF23 -to SDRAM2_DQ[8]

21 | set_location_assignment PIN_AG24 -to SDRAM2_A[12]

22 | set_location_assignment PIN_AH22 -to SDRAM2_CLK

23 | set_location_assignment PIN_AH21 -to SDRAM2_A[9]

24 | set_location_assignment PIN_AG21 -to SDRAM2_A[11]

25 | set_location_assignment PIN_AH23 -to SDRAM2_A[7]

26 | set_location_assignment PIN_AA20 -to SDRAM2_A[8]

27 | set_location_assignment PIN_AF22 -to SDRAM2_A[5]

28 | set_location_assignment PIN_AE22 -to SDRAM2_A[6]

29 | set_location_assignment PIN_AG20 -to SDRAM2_nWE

30 | set_location_assignment PIN_AF21 -to SDRAM2_A[4]

31 |

32 | set_location_assignment PIN_AG19 -to SDRAM2_nCAS

33 | set_location_assignment PIN_AH19 -to SDRAM2_nRAS

34 | set_location_assignment PIN_AG18 -to SDRAM2_nCS

35 | set_location_assignment PIN_AH18 -to SDRAM2_BA[0]

36 | set_location_assignment PIN_AF18 -to SDRAM2_BA[1]

37 | set_location_assignment PIN_AF20 -to SDRAM2_A[10]

38 | set_location_assignment PIN_AG15 -to SDRAM2_A[0]

39 | set_location_assignment PIN_AE20 -to SDRAM2_A[1]

40 | set_location_assignment PIN_AE19 -to SDRAM2_A[2]

41 | set_location_assignment PIN_AE17 -to SDRAM2_A[3]

42 |

43 | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to SDRAM2_*

44 | set_instance_assignment -name CURRENT_STRENGTH_NEW "MAXIMUM CURRENT" -to SDRAM2_*

45 | set_instance_assignment -name FAST_OUTPUT_REGISTER ON -to SDRAM2_*

46 | set_instance_assignment -name FAST_OUTPUT_ENABLE_REGISTER ON -to SDRAM2_DQ[*]

47 | set_instance_assignment -name FAST_INPUT_REGISTER ON -to SDRAM2_DQ[*]

48 | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to SDRAM2_DQ[*]

49 | set_instance_assignment -name ALLOW_SYNCH_CTRL_USAGE OFF -to *|SDRAM2_*

50 |

51 | set_global_assignment -name VERILOG_MACRO "MISTER_DUAL_SDRAM=1"

52 |

--------------------------------------------------------------------------------

/rtl/T80/README:

--------------------------------------------------------------------------------

1 | --------------------------------------------------------------------------------

2 | -- ****

3 | -- T80(c) core. Attempt to finish all undocumented features and provide

4 | -- accurate timings.

5 | --

6 | -- Version 351.

7 | -- Merged Gameboy fixes from Bruno Duarte Gouveia (brNX)

8 | -- Passes Blargg's test ROMs

9 | --

10 | -- Version 350.

11 | -- Copyright (c) 2018 Sorgelig

12 | -- Test passed: ZEXDOC, ZEXALL, Z80Full(*), Z80memptr

13 | -- (*) Currently only SCF and CCF instructions aren't passed X/Y flags check as

14 | -- correct implementation is still unclear.

15 | --

16 | -- ****

17 | -- T80(b) core. In an effort to merge and maintain bug fixes ....

18 | --

19 | -- Ver 303 add undocumented DDCB and FDCB opcodes by TobiFlex 20.04.2010

20 | -- Ver 301 parity flag is just parity for 8080, also overflow for Z80, by Sean Riddle

21 | -- Ver 300 started tidyup.

22 | --

23 | -- MikeJ March 2005

24 | -- Latest version from www.fpgaarcade.com (original www.opencores.org)

25 | --

26 | -- ****

27 | -- Z80 compatible microprocessor core

28 | --

29 | -- Version : 0250

30 | -- Copyright (c) 2001-2002 Daniel Wallner (jesus@opencores.org)

31 | -- All rights reserved

32 | --

33 | -- Redistribution and use in source and synthezised forms, with or without

34 | -- modification, are permitted provided that the following conditions are met:

35 | --

36 | -- Redistributions of source code must retain the above copyright notice,

37 | -- this list of conditions and the following disclaimer.

38 | --

39 | -- Redistributions in synthesized form must reproduce the above copyright

40 | -- notice, this list of conditions and the following disclaimer in the

41 | -- documentation and/or other materials provided with the distribution.

42 | --

43 | -- Neither the name of the author nor the names of other contributors may

44 | -- be used to endorse or promote products derived from this software without

45 | -- specific prior written permission.

46 | --

47 | -- THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

48 | -- AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO,

49 | -- THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR

50 | -- PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE AUTHOR OR CONTRIBUTORS BE

51 | -- LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR

52 | -- CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF

53 | -- SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS

54 | -- INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN

55 | -- CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE)

56 | -- ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE

57 | -- POSSIBILITY OF SUCH DAMAGE.

58 | --

59 |

--------------------------------------------------------------------------------

/rtl/pcw_starter.sv:

--------------------------------------------------------------------------------

1 | module pcw_starter(

2 | input wire clk,

3 | input wire reset,

4 | input wire sdram_clk_ref,