├── LICENSE

├── README.md

├── fpga

├── common

│ └── wlan_files.tcl

├── ip

│ ├── altera

│ │ ├── fft64

│ │ │ ├── fft64.qsys

│ │ │ └── generate.sh

│ │ ├── viterbi_decoder

│ │ │ ├── generate.sh

│ │ │ └── viterbi_decoder.qsys

│ │ └── wlan_pll

│ │ │ └── generate.sh

│ ├── generate.sh

│ └── nuand

│ │ ├── cordic.vhd

│ │ ├── fft

│ │ ├── model

│ │ │ ├── Makefile

│ │ │ ├── dft.c

│ │ │ └── idft.c

│ │ └── vhdl

│ │ │ ├── dual_port_ram.vhd

│ │ │ ├── fft.vhd

│ │ │ ├── fft_top.vhd

│ │ │ └── tb

│ │ │ ├── compile.do

│ │ │ └── fft_tb.vhd

│ │ ├── nco.vhd

│ │ └── viterbi_decoder

│ │ ├── model

│ │ ├── encoder.c

│ │ └── out.c

│ │ └── vhdl

│ │ ├── branch_compare.vhd

│ │ ├── comp2.vhd

│ │ ├── r2_comparator.vhd

│ │ ├── tb

│ │ ├── compile.do

│ │ ├── r2_comparator_tb.vhd

│ │ ├── viterbi_decoder_tb.vhd

│ │ └── wave.do

│ │ ├── traceback.vhd

│ │ ├── tracer.vhd

│ │ ├── viterbi_decoder.vhd

│ │ └── viterbi_p.vhd

├── modelsim

│ └── wlan.do

├── quartus

│ └── wlan.qip

└── vhdl

│ ├── clock_sync_logic.vhd

│ ├── clock_sync_logic_vector.vhd

│ ├── clock_sync_params.vhd

│ ├── tb

│ ├── wlan_ack_generator_tb.vhd

│ ├── wlan_acquisition_tb.vhd

│ ├── wlan_bsd_tb.vhd

│ ├── wlan_channel_inverter_tb.vhd

│ ├── wlan_clock_tb.vhd

│ ├── wlan_dsss_plcp_crc_tb.vhd

│ ├── wlan_interleaver_tb.vhd

│ ├── wlan_lfsr_tb.vhd

│ ├── wlan_modulator_tb.vhd

│ ├── wlan_peak_finder_tb.vhd

│ ├── wlan_rx_tb.vhd

│ ├── wlan_sample_loader.vhd

│ ├── wlan_sample_saver.vhd

│ ├── wlan_symbol_shaper_tb.vhd

│ ├── wlan_tables_p.vhd

│ ├── wlan_tb.vhd

│ ├── wlan_top_tb.vhd

│ ├── wlan_tx_long_tb.vhd

│ ├── wlan_tx_short_tb.vhd

│ ├── wlan_tx_tb.vhd

│ ├── wlan_viterbi_encoder_tb.vhd

│ └── wlan_viterbi_tb.vhd

│ ├── wlan_ack_generator.vhd

│ ├── wlan_acquisition.vhd

│ ├── wlan_agc.vhd

│ ├── wlan_agc_drv.vhd

│ ├── wlan_bsd.vhd

│ ├── wlan_cfo_correction.vhd

│ ├── wlan_cfo_estimate.vhd

│ ├── wlan_channel_inverter.vhd

│ ├── wlan_clamper.vhd

│ ├── wlan_correlator.vhd

│ ├── wlan_crc.vhd

│ ├── wlan_csma.vhd

│ ├── wlan_dcf.vhd

│ ├── wlan_deinterleaver.vhd

│ ├── wlan_delay_correlator.vhd

│ ├── wlan_demodulator.vhd

│ ├── wlan_depuncturer.vhd

│ ├── wlan_descrambler.vhd

│ ├── wlan_divide.vhd

│ ├── wlan_dsss_demodulator.vhd

│ ├── wlan_dsss_despreader.vhd

│ ├── wlan_dsss_p_norm.vhd

│ ├── wlan_dsss_peak_finder.vhd

│ ├── wlan_dsss_plcp_crc.vhd

│ ├── wlan_dsss_rx.vhd

│ ├── wlan_dsss_rx_controller.vhd

│ ├── wlan_dsss_rx_framer.vhd

│ ├── wlan_encoder.vhd

│ ├── wlan_equalizer.vhd

│ ├── wlan_fft64.vhd

│ ├── wlan_framer.vhd

│ ├── wlan_ifft64.vhd

│ ├── wlan_interleaver.vhd

│ ├── wlan_interleaver_p.vhd

│ ├── wlan_lfsr.vhd

│ ├── wlan_modulator.vhd

│ ├── wlan_p.vhd

│ ├── wlan_p_norm.vhd

│ ├── wlan_peak_finder.vhd

│ ├── wlan_phase_correction.vhd

│ ├── wlan_rx.vhd

│ ├── wlan_rx_controller.vhd

│ ├── wlan_rx_framer.vhd

│ ├── wlan_rx_p.vhd

│ ├── wlan_rx_packet_buffer.vhd

│ ├── wlan_sample_buffer.vhd

│ ├── wlan_scrambler.vhd

│ ├── wlan_symbol_shaper.vhd

│ ├── wlan_top.vhd

│ ├── wlan_tx.vhd

│ ├── wlan_tx_controller.vhd

│ ├── wlan_tx_long.vhd

│ ├── wlan_tx_p.vhd

│ ├── wlan_tx_short.vhd

│ ├── wlan_viterbi_decoder.vhd

│ └── wlan_viterbi_encoder.vhd

└── matlab

├── util.m

└── wlan_rx.m

/README.md:

--------------------------------------------------------------------------------

1 | # bladeRF-wiphy

2 |

3 | bladeRF-wiphy is an open-source IEEE 802.11 compatible software defined radio VHDL modem

4 |

5 |  6 |

7 | ## What is the bladeRF-wiphy project?

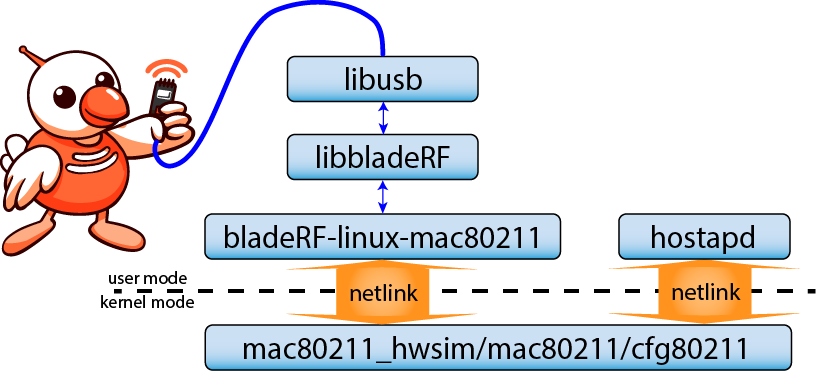

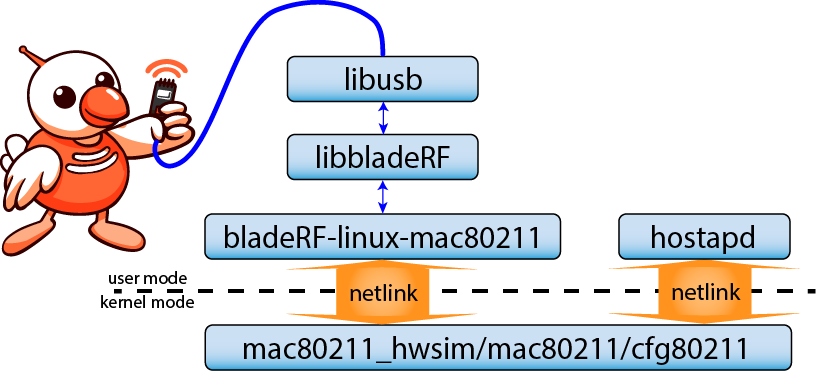

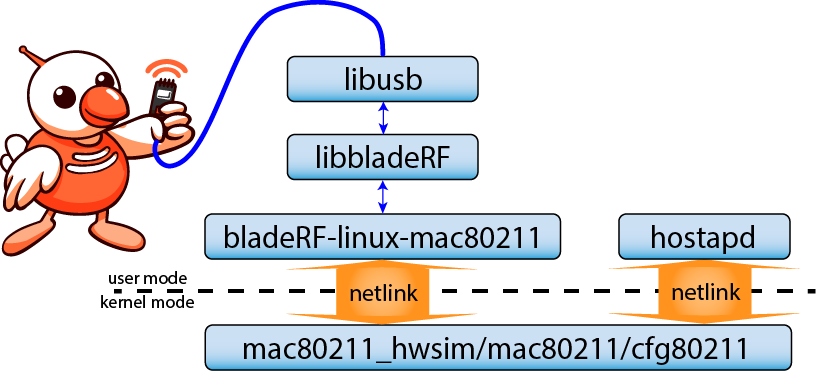

8 | The bladeRF-wiphy project is an open-source IEEE 802.11 compatible software defined radio VHDL modem. The modem is able to modulate and demodulate 802.11 packets (the protocol WiFi is based on), and run directly on the bladeRF 2.0 micro xA9’s FPGA.

9 |

10 | The bladeRF-wiphy coupled with Linux mac80211 allows the [bladeRF 2.0 micro xA9](https://www.nuand.com/product/bladerf-xA9/) to become a software defined radio 802.11 access point! 802.11 packets (PDUs) are modulated and demodulated directly on the FPGA, so only 802.11 packets are transferred between the FPGA and libbladeRF.

11 |

12 | ## Documentation

13 | A technical deep dive of bladeRF-wiphy https://www.nuand.com/bladeRF-wiphy/

14 |

15 | Instructions to compile, install, and run bladeRF-wiphy and tools https://www.nuand.com/bladeRF-wiphy-instructions/

16 |

17 | Instructions to simulate bladeRF-wiphy: https://www.nuand.com/bladeRF-wiphy-simulation/

18 |

19 |

6 |

7 | ## What is the bladeRF-wiphy project?

8 | The bladeRF-wiphy project is an open-source IEEE 802.11 compatible software defined radio VHDL modem. The modem is able to modulate and demodulate 802.11 packets (the protocol WiFi is based on), and run directly on the bladeRF 2.0 micro xA9’s FPGA.

9 |

10 | The bladeRF-wiphy coupled with Linux mac80211 allows the [bladeRF 2.0 micro xA9](https://www.nuand.com/product/bladerf-xA9/) to become a software defined radio 802.11 access point! 802.11 packets (PDUs) are modulated and demodulated directly on the FPGA, so only 802.11 packets are transferred between the FPGA and libbladeRF.

11 |

12 | ## Documentation

13 | A technical deep dive of bladeRF-wiphy https://www.nuand.com/bladeRF-wiphy/

14 |

15 | Instructions to compile, install, and run bladeRF-wiphy and tools https://www.nuand.com/bladeRF-wiphy-instructions/

16 |

17 | Instructions to simulate bladeRF-wiphy: https://www.nuand.com/bladeRF-wiphy-simulation/

18 |

19 |

20 |  21 |

21 |

22 |

23 | ## Features

24 | - IEEE 802.11 compatible FPGA based PHY receiver and transmitter

25 | - Compatible with [bladeRF 2.0 micro xA9](https://www.nuand.com/product/bladerf-xA9/)

26 | - Linux mac80211 MAC integration

27 | - RX and TX monitor mode support

28 | - Hardware Distributed Coordination Function (DCF) allows quick turn-around time ACKs

29 | - High-performance equalizer – implements Zero Forcing (ZF) and optionally Decision Feedback Equalizer (DFE)

30 |

31 | ## Modulation schemes

32 | - DSSS - CCK

33 | - OFDM - 20MHz (6Mbps, 9Mbps, 12Mbps, 18Mbps, 24Mbps, 36Mbps, 48Mbps, 54Mbps)

34 |

35 | ## Modulation constellations

36 | - DSSS-CCK DBPSK

37 | - OFDM-BPSK

38 | - OFDM-QPSK

39 | - OFDM-16-QAM

40 | - OFDM-64-QAM

41 |

42 | ## Contact information

43 | Email: bladeRF@nuand.com

44 |

45 | Slack: See Slack section on this [page](https://www.nuand.com/support/)

46 |

--------------------------------------------------------------------------------

/fpga/ip/altera/fft64/fft64.qsys:

--------------------------------------------------------------------------------

1 |

2 |

3 |

10 |

22 |

23 |

24 |

25 |

26 |

27 |

28 |

29 |

30 |

31 |

32 |

33 |

34 |

35 |

36 |

37 |

38 |

39 |

40 |

41 |

42 |

43 |

44 |

45 |

46 |

47 |

48 |

49 |

50 |

51 |

52 |

53 |

54 |

55 |

56 |

57 |

58 |

59 |

60 |

61 |

62 |

63 |

64 |

65 |

66 |

72 |

73 |

74 |

75 |

76 |

77 |

78 |

79 |

80 |

81 |

82 |

83 |

84 |

85 |

86 |

87 |

88 |

89 |

90 |

91 |

92 |

93 |

94 |

--------------------------------------------------------------------------------

/fpga/ip/altera/fft64/generate.sh:

--------------------------------------------------------------------------------

1 | qsys-generate --sim --synthesis=VHDL ./fft64.qsys

2 |

--------------------------------------------------------------------------------

/fpga/ip/altera/viterbi_decoder/generate.sh:

--------------------------------------------------------------------------------

1 | qsys-generate --sim --synthesis=VHDL viterbi_decoder.qsys

2 |

--------------------------------------------------------------------------------

/fpga/ip/altera/viterbi_decoder/viterbi_decoder.qsys:

--------------------------------------------------------------------------------

1 |

2 |

3 |

10 |

22 |

23 |

24 |

25 |

26 |

27 |

28 |

29 |

30 |

31 |

32 |

33 |

34 |

35 |

36 |

37 |

38 |

39 |

40 |

41 |

42 |

43 |

44 |

45 |

46 |

47 |

48 |

49 |

50 |

51 |

52 |

53 |

54 |

55 |

56 |

57 |

63 |

64 |

65 |

66 |

67 |

68 |

69 |

70 |

71 |

72 |

73 |

74 |

75 |

76 |

77 |

78 |

79 |

80 |

81 |

82 |

83 |

84 |

85 |

86 |

87 |

88 |

89 |

90 |

91 |

92 |

--------------------------------------------------------------------------------

/fpga/ip/altera/wlan_pll/generate.sh:

--------------------------------------------------------------------------------

1 | ip-generate --file-set=QUARTUS_SYNTH --component-name=altera_pll --output-name=wlan_pll \

2 | --component-param=gui_reference_clock_frequency="40MHz" \

3 | --component-param=gui_output_clock_frequency0="80MHz" \

4 | --component-param=gui_phase_shift0="0ps" \

5 | --component-param=gui_duty_cycle0="50%"

6 |

--------------------------------------------------------------------------------

/fpga/ip/generate.sh:

--------------------------------------------------------------------------------

1 | for i in */*/generate.sh; do echo "Running $i"; (cd `dirname $i`; sh generate.sh); done

2 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/fft/model/Makefile:

--------------------------------------------------------------------------------

1 | all: dft idft

2 |

3 | dft: dft.c

4 | gcc -o dft dft.c -g3 -lm

5 |

6 | idft: idft.c

7 | gcc -o idft idft.c -g3 -lm

8 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/fft/model/dft.c:

--------------------------------------------------------------------------------

1 | // This file is part of bladeRF-wiphy.

2 | //

3 | // Copyright (C) 2021 Nuand, LLC.

4 | //

5 | // This program is free software; you can redistribute it and/or modify

6 | // it under the terms of the GNU General Public License as published by

7 | // the Free Software Foundation; either version 2 of the License, or

8 | // (at your option) any later version.

9 | //

10 | // This program is distributed in the hope that it will be useful,

11 | // but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | // MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | // GNU General Public License for more details.

14 | //

15 | // You should have received a copy of the GNU General Public License along

16 | // with this program; if not, write to the Free Software Foundation, Inc.,

17 | // 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | #include

20 | #include

21 |

22 |

23 | int flip_bits(unsigned in, int bits) {

24 | unsigned ret = 0;

25 | int i;

26 | for (i = 0; i < bits; i++) {

27 | ret |= ( !!(in & (1 << i)) ) << (bits - i - 1);

28 | }

29 | printf("IN %d, OUT %d\n", in, ret);

30 | return ret;

31 | }

32 |

33 | unsigned rotate_left(unsigned in, int width, int num) {

34 | unsigned ret = 0;

35 | unsigned bottom = 0;

36 | unsigned mask = 0;

37 | bottom = in;

38 | //printf("#1 = %d\n", bottom);

39 | bottom >>= (width - num);

40 | //printf("#2 = %d\n", bottom);

41 | mask = ((1 << (num+1)) - 1);

42 | //printf("mask = %d\n", mask);

43 | bottom &= mask;

44 | //printf("BOTTOM = %d\n", bottom);

45 |

46 | ret = in;

47 | ret <<= num;

48 | ret = ret & ((1 << width) - 1);

49 | //printf("TOP = %d\n", ret);

50 |

51 | ret |= bottom;

52 | return(ret);

53 | }

54 |

55 | struct c_sample {

56 | float i, q;

57 | };

58 |

59 | #define N 64

60 | #define N_POW 6

61 | #define FMT "%f"

62 |

63 | struct c_sample rfs_i[] = {

64 | { 402, 750}, { -439, 700}, { 909, -96}, {-7, -496}, {76, -711}, {764, 601}, {-192, 315}, {411, -633},

65 | {-540, -139}, {-360, -640}, {821, -172}, {160, 291}, {9, -678}, {-679, -241}, {69, -293}, {565, -172},

66 | {-356, 999}, {515, -19}, {438, -498}, {78, 693}, {-276, 209}, {-865, 131}, {465, 487}, {454, 35},

67 | {-480, 437}, {-324, -45}, {-86, -991}, {-471, 2}, {-805, -38}, {543, -621}, {170, 397}, {-797, 606},

68 | {546, 369}, {150, 591}, {-1095, -17}, {109, -684}, {760, -450}, {-573, -478}, {-66, -409}, {682, 484},

69 | {-862, 201}, {-695, -192}, {16, 819}, {-403, 172}, {-342, -660}, {443, 14}, {544, -389}, {-734, -339},

70 | {-366, -141}, {381, -626}, {280, 382}, {624, 235}, {-218, 980}, {333, 54}, {333, 506}, {-944, 114},

71 | {46, 566}, {305, -48}, {457, -20}, {-56, 740}, {-919, 197}, {522, 295}, {-2, 20}, {438, -712}

72 | };

73 |

74 | void gen_sample(int n, struct c_sample *ptr) {

75 | int r, idx;

76 | for (r = 0; r < n; r++) {

77 | idx = flip_bits(r, N_POW);

78 | ptr[idx] = rfs_i[r];

79 | printf("Wrote %d to c[%d] = " FMT " + j*" FMT "\n", r, idx, ptr[idx].i, ptr[idx].q);

80 | }

81 | }

82 |

83 | void butter_fly(struct c_sample *A, struct c_sample *B, struct c_sample *TW)

84 | {

85 | struct c_sample mix, t_A, t_B;

86 | // A = a_i + j * a_q

87 | // B = b_i + j * b_q

88 |

89 | // C = A X B = (a_i * b_i + a_i * j * b_q + j * a_q * b_i + j * a_q * j * b_q)

90 | // C = ( a_i * b_i - a_q * b_q) + j ( a_i * b_q + a_q + b_i )

91 | // C_i = a_i * b_i - a_q * b_q

92 | // C_q = a_i * b_q + a_q * b_i

93 |

94 |

95 | mix.i = (B->i * TW->i - B->q * TW->q) /(32768);//>> 15;

96 | mix.q = (B->i * TW->q + B->q * TW->i) /(32768);//>> 15;

97 |

98 | //A->i *= 1;

99 | //A->q *= 1;

100 | //B->i *= 1;

101 | //B->q *= 1;

102 |

103 | t_A.i = A->i + mix.i;

104 | t_A.q = A->q + mix.q;

105 |

106 | t_B.i = A->i - mix.i;

107 | t_B.q = A->q - mix.q;

108 |

109 | printf("A: " FMT " + j* " FMT " B: " FMT " + j* " FMT " TW: " FMT " + j* " FMT "\n", A->i, A->q, B->i, B->q, TW->i, TW->q);

110 | printf("mix: " FMT " + j* " FMT "\n", mix.i, mix.q);

111 |

112 | *A = t_A;

113 | *B = t_B;

114 | printf("A: " FMT " + j* " FMT " B: " FMT " + j* " FMT "\n\n", A->i, A->q, B->i, B->q);

115 | }

116 |

117 |

118 | int W_i[N/2];

119 | int W_q[N/2];

120 | int main() {

121 | float ti, tq;

122 | int i, j;

123 | struct c_sample s_a[N], s_b[N], s_tw[N];

124 | gen_sample(N, s_a);

125 |

126 | #if 0

127 | for (i = 0; i < (N);i++) {

128 | printf("[%d] = " FMT " " FMT "\n", i, s_a[i].i, s_a[i].q);

129 | }

130 | #endif

131 | /*

132 | for (i = 0; i < (N/2);i++) {

133 | printf("%Lf, %Lf\n", sinl((2.0 * M_PI * (float)i) / N), cosl((2.0 * M_PI * (float)i) / N));

134 | }

135 | */

136 |

137 | for (i = 0; i < (N/2); i++) {

138 | ti = cosf((2.0 * M_PI * (float)i) / (float)N);

139 | s_tw[i].i = W_i[i] = ti * ((1<<15)-1);

140 | tq = sinf((2.0 * M_PI * (float)i) / (float)N);

141 | s_tw[i].q = W_q[i] = tq * ((1<<15)-1);

142 |

143 |

144 | printf("[%.2d] I= %.15f = 0x%.8x Q= %.15f = 0x%.8x\t\t" FMT ", " FMT "\n", i, ti, W_i[i], tq, W_q[i], s_tw[i].i, s_tw[i].q);

145 | }

146 |

147 | for (i = 0; i < N_POW; i++) {

148 | for (j = 0; j < (N/2); j++) {

149 | int a, b, tw;

150 | a = rotate_left(j * 2, N_POW, i);

151 | b = rotate_left(j * 2 + 1, N_POW, i);

152 | //tw = (j & ((1<< (i)) - 1)) << (N_POW-1-i); DIF

153 | tw = (j ) & ((1 << (N_POW - 1)) - 1) - ((1 << (N_POW - 1 - i)) -1);

154 |

155 | printf("Stage=%d A=%d,%d tw=%d\n", i, a, b, tw);

156 | if ( i == 0) {

157 | printf("\t%d,%d => A is timeidx = %d, B is timeidx = %d\n", a,b, flip_bits(a, N_POW), flip_bits(b, N_POW));

158 | }

159 | butter_fly(s_a + a, s_a + b, s_tw + tw );

160 |

161 | }

162 | printf("\n\n");

163 | }

164 |

165 | for (i = 0; i < N; i++) {

166 | printf("[%.2d] = " FMT " + j * " FMT "\n", i, s_a[i].i, s_a[i].q);

167 | }

168 | printf("\n\n");

169 | for (i = 0; i < N; i++) {

170 | printf("[%.2d] = %f\n", i, sqrt(s_a[i].i * s_a[i].i + s_a[i].q * s_a[i].q));

171 | }

172 | return 0;

173 | }

174 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/fft/model/idft.c:

--------------------------------------------------------------------------------

1 | // This file is part of bladeRF-wiphy.

2 | //

3 | // Copyright (C) 2021 Nuand, LLC.

4 | //

5 | // This program is free software; you can redistribute it and/or modify

6 | // it under the terms of the GNU General Public License as published by

7 | // the Free Software Foundation; either version 2 of the License, or

8 | // (at your option) any later version.

9 | //

10 | // This program is distributed in the hope that it will be useful,

11 | // but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | // MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | // GNU General Public License for more details.

14 | //

15 | // You should have received a copy of the GNU General Public License along

16 | // with this program; if not, write to the Free Software Foundation, Inc.,

17 | // 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | #include

20 | #include

21 |

22 |

23 | int flip_bits(unsigned in, int bits) {

24 | unsigned ret = 0;

25 | int i;

26 | for (i = 0; i < bits; i++) {

27 | ret |= ( !!(in & (1 << i)) ) << (bits - i - 1);

28 | }

29 | printf("IN %d, OUT %d\n", in, ret);

30 | return ret;

31 | }

32 |

33 | int f_s[]= {

34 | 0, 1, -1, -1, -1, 1, -1, 1, -1, -1, -1, 1, 1, -1, -1, 1, -1, 1, 1, -1, -1, -1, -1, -1, 1, -1, -1, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 1, 1, -1, 1, 1, 1, -1, 1, 1, -1, -1, -1, -1, 1, -1, -1, -1, -1, -1, 1, 1, -1, -1, 1, 1, -1 };

35 |

36 | unsigned rotate_left(unsigned in, int width, int num) {

37 | unsigned ret = 0;

38 | unsigned bottom = 0;

39 | unsigned mask = 0;

40 | bottom = in;

41 | //printf("#1 = %d\n", bottom);

42 | bottom >>= (width - num);

43 | //printf("#2 = %d\n", bottom);

44 | mask = ((1 << (num+1)) - 1);

45 | //printf("mask = %d\n", mask);

46 | bottom &= mask;

47 | //printf("BOTTOM = %d\n", bottom);

48 |

49 | ret = in;

50 | ret <<= num;

51 | ret = ret & ((1 << width) - 1);

52 | //printf("TOP = %d\n", ret);

53 |

54 | ret |= bottom;

55 | return(ret);

56 | }

57 |

58 | struct c_sample {

59 | long long int i, q;

60 | };

61 |

62 | #define N 64

63 | #define N_POW 6

64 | #define FMT "%lld"

65 |

66 | void gen_sample(int n, struct c_sample *ptr) {

67 | int r, idx;

68 | for (r = 0; r < n; r++) {

69 | idx = flip_bits(r, N_POW);

70 | ptr[idx].i = f_s[r] * 4096;

71 | ptr[idx].q = 0;

72 | printf("Wrote %d to c[%d] = " FMT " + j*" FMT "\n", r, idx, ptr[idx].i, ptr[idx].q);

73 | }

74 | }

75 |

76 | void butter_fly(struct c_sample *A, struct c_sample *B, struct c_sample *TW)

77 | {

78 | struct c_sample mix, t_A, t_B;

79 | // A = a_i + j * a_q

80 | // B = b_i + j * b_q

81 |

82 | // C = A X B = (a_i * b_i + a_i * j * b_q + j * a_q * b_i + j * a_q * j * b_q)

83 | // C = ( a_i * b_i - a_q * b_q) + j ( a_i * b_q + a_q + b_i )

84 | // C_i = a_i * b_i - a_q * b_q

85 | // C_q = a_i * b_q + a_q * b_i

86 |

87 |

88 | mix.i = (B->i * TW->i - B->q * TW->q) >> 15;

89 | mix.q = (B->i * TW->q + B->q * TW->i) >> 15;

90 |

91 | //A->i *= 1;

92 | //A->q *= 1;

93 | //B->i *= 1;

94 | //B->q *= 1;

95 |

96 | t_A.i = A->i + mix.i;

97 | t_A.q = A->q + mix.q;

98 |

99 | t_B.i = A->i - mix.i;

100 | t_B.q = A->q - mix.q;

101 |

102 | printf("A: " FMT " + j* " FMT " B: " FMT " + j* " FMT " TW: " FMT " + j* " FMT "\n", A->i, A->q, B->i, B->q, TW->i, TW->q);

103 | printf("mix: " FMT " + j* " FMT "\n", mix.i, mix.q);

104 |

105 | *A = t_A;

106 | *B = t_B;

107 | printf("A: " FMT " + j* " FMT " B: " FMT " + j* " FMT "\n\n", A->i, A->q, B->i, B->q);

108 | }

109 |

110 |

111 | int W_i[N/2];

112 | int W_q[N/2];

113 | int main() {

114 | float ti, tq;

115 | int i, j;

116 | struct c_sample s_a[N], s_b[N], s_tw[N];

117 | gen_sample(N, s_a);

118 |

119 | #if 0

120 | for (i = 0; i < (N);i++) {

121 | printf("[%d] = " FMT " " FMT "\n", i, s_a[i].i, s_a[i].q);

122 | }

123 | #endif

124 | /*

125 | for (i = 0; i < (N/2);i++) {

126 | printf("%Lf, %Lf\n", sinl((2.0 * M_PI * (float)i) / N), cosl((2.0 * M_PI * (float)i) / N));

127 | }

128 | */

129 |

130 | for (i = 0; i < (N/2); i++) {

131 | ti = cosf((2.0 * M_PI * (float)i) / (float)N);

132 | s_tw[i].i = W_i[i] = ti * ((1<<15)-1);

133 | tq = sinf((2.0 * M_PI * (float)i) / (float)N);

134 | s_tw[i].q = W_q[i] = tq * ((1<<15)-1);

135 |

136 |

137 | printf("[%.2d] I= %.15f = 0x%.8x Q= %.15f = 0x%.8x\t\t" FMT ", " FMT "\n", i, ti, W_i[i], tq, W_q[i], s_tw[i].i, s_tw[i].q);

138 | }

139 |

140 | for (i = 0; i < N_POW; i++) {

141 | for (j = 0; j < (N/2); j++) {

142 | int a, b, tw;

143 | a = rotate_left(j * 2, N_POW, i);

144 | b = rotate_left(j * 2 + 1, N_POW, i);

145 | //tw = (j & ((1<< (i)) - 1)) << (N_POW-1-i); DIF

146 | tw = (j) & ((1 << (N_POW - 1)) - 1) - ((1 << (N_POW - 1 - i)) -1);

147 |

148 | printf("Stage=%d A=%d,%d tw=%d\n", i, a, b, tw);

149 | if (i == 0) {

150 | printf("\t%d,%d => A is timeidx = %d, B is timeidx = %d\n", a,b, flip_bits(a, N_POW), flip_bits(b, N_POW));

151 | }

152 | butter_fly(s_a + a, s_a + b, s_tw + tw );

153 |

154 | }

155 | printf("\n\n");

156 | }

157 |

158 | for (i = 0; i < N; i++) {

159 | printf("[%.2d] = " FMT " + j * " FMT "\n", i, s_a[i].i/64, s_a[i].q/64);

160 | }

161 | printf("\n\n");

162 | for (i = 0; i < N; i++) {

163 | printf("[%.2d] = %f\n", i, sqrt(s_a[i].i * s_a[i].i + s_a[i].q * s_a[i].q));

164 | }

165 | return 0;

166 | }

167 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/fft/vhdl/dual_port_ram.vhd:

--------------------------------------------------------------------------------

1 | -- This file is part of bladeRF-wiphy.

2 | --

3 | -- Copyright (C) 2021 Nuand, LLC.

4 | --

5 | -- This program is free software; you can redistribute it and/or modify

6 | -- it under the terms of the GNU General Public License as published by

7 | -- the Free Software Foundation; either version 2 of the License, or

8 | -- (at your option) any later version.

9 | --

10 | -- This program is distributed in the hope that it will be useful,

11 | -- but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | -- MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | -- GNU General Public License for more details.

14 | --

15 | -- You should have received a copy of the GNU General Public License along

16 | -- with this program; if not, write to the Free Software Foundation, Inc.,

17 | -- 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | library ieee;

20 | use ieee.std_logic_1164.all;

21 | use ieee.numeric_std.all;

22 |

23 | entity dual_port_ram is

24 | generic(

25 | ADDR_BITS : in natural := 6;

26 | DATA_BITS : in natural := 32

27 | );

28 | port(

29 | clock : in std_logic;

30 | reset : in std_logic;

31 |

32 | acc : in std_logic;

33 | solo : in std_logic;

34 | write : in std_logic;

35 |

36 | addr_a : in std_logic_vector(ADDR_BITS-1 downto 0);

37 | in_a : in std_logic_vector(DATA_BITS-1 downto 0);

38 | data_a : out std_logic_vector(DATA_BITS-1 downto 0);

39 |

40 | addr_b : in std_logic_vector(ADDR_BITS-1 downto 0);

41 | in_b : in std_logic_vector(DATA_BITS-1 downto 0);

42 | data_b : out std_logic_vector(DATA_BITS-1 downto 0)

43 | );

44 | end entity;

45 |

46 | architecture arch of dual_port_ram is

47 | type ram_t is array(natural range <>) of std_logic_vector(DATA_BITS-1 downto 0);

48 |

49 | signal ram : ram_t((2**ADDR_BITS-1) downto 0);

50 | begin

51 | sync : process(clock, reset)

52 | variable add_a, add_b : integer;

53 | begin

54 | if (reset = '1') then

55 | for i in ram'range loop

56 | ram(i) <= ( others => '0' );

57 | end loop;

58 | elsif (rising_edge(clock)) then

59 | if (acc = '1') then

60 | add_a := to_integer(unsigned(addr_a));

61 | add_b := to_integer(unsigned(addr_b));

62 |

63 | if (write = '1') then

64 | ram(add_a) <= in_a;

65 | data_a <= in_a;

66 | if (solo = '0') then

67 | ram(add_b) <= in_b;

68 | data_b <= in_b;

69 | else

70 | data_b <= ( others => '0' );

71 | end if;

72 | else

73 | data_a <= ram(add_a);

74 | if (solo = '0') then

75 | data_b <= ram(add_b);

76 | else

77 | data_b <= ( others => '0' );

78 | end if;

79 | end if;

80 | end if;

81 |

82 | end if;

83 | end process;

84 | end architecture;

85 |

86 | architecture synth of dual_port_ram is

87 | type ram_t is array(natural range <>) of std_logic_vector(DATA_BITS-1 downto 0);

88 |

89 | shared variable ram : ram_t((2**ADDR_BITS-1) downto 0);

90 | begin

91 | synca : process(clock, reset)

92 | variable addra : integer;

93 | begin

94 | if (rising_edge(clock)) then

95 | addra := to_integer(unsigned(addr_a));

96 | if (write = '1') then

97 | ram(addra) := in_a;

98 | end if;

99 | data_a <= ram(addra);

100 | end if;

101 | end process;

102 |

103 | syncb : process(clock, reset)

104 | variable addrb : integer;

105 | begin

106 | if (rising_edge(clock)) then

107 | addrb := to_integer(unsigned(addr_b));

108 | if (write = '1') then

109 | ram(addrb) := in_b;

110 | end if;

111 | data_b <= ram(addrb);

112 | end if;

113 | end process;

114 | end architecture synth;

115 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/fft/vhdl/fft_top.vhd:

--------------------------------------------------------------------------------

1 | -- This file is part of bladeRF-wiphy.

2 | --

3 | -- Copyright (C) 2021 Nuand, LLC.

4 | --

5 | -- This program is free software; you can redistribute it and/or modify

6 | -- it under the terms of the GNU General Public License as published by

7 | -- the Free Software Foundation; either version 2 of the License, or

8 | -- (at your option) any later version.

9 | --

10 | -- This program is distributed in the hope that it will be useful,

11 | -- but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | -- MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | -- GNU General Public License for more details.

14 | --

15 | -- You should have received a copy of the GNU General Public License along

16 | -- with this program; if not, write to the Free Software Foundation, Inc.,

17 | -- 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | library ieee;

20 | use ieee.std_logic_1164.all;

21 | use ieee.numeric_std.all;

22 | use ieee.math_real.all;

23 | library pll;

24 | use pll.all;

25 | entity fft_top is

26 | generic(

27 | BITS : in natural := 16

28 | );

29 | port(

30 | clk : in std_logic;

31 | reset : in std_logic;

32 |

33 | inverse : in std_logic;

34 | in_real : in std_logic_vector(BITS-1 downto 0);

35 | in_imag : in std_logic_vector(BITS-1 downto 0);

36 | in_valid : in std_logic;

37 | in_sop : in std_logic;

38 | in_eop : in std_logic;

39 |

40 | out_real : out std_logic_vector(BITS-1 downto 0);

41 | out_imag : out std_logic_vector(BITS-1 downto 0);

42 | out_error : out std_logic;

43 | out_valid : out std_logic;

44 | out_sop : out std_logic;

45 | out_eop : out std_logic

46 | );

47 | end entity;

48 |

49 | architecture arch of fft_top is

50 | signal clock : std_logic;

51 | begin

52 |

53 | U_pll : entity pll.pll

54 | port map(

55 | refclk => clk,

56 | rst => '0',

57 | outclk_0 => clock,

58 | locked => open

59 | );

60 |

61 | U_fft : entity work.fft(mult)

62 | generic map(

63 | N => 64,

64 | BITS => 16

65 | )

66 | port map(

67 | clock => clock,

68 | reset => reset,

69 |

70 | inverse => inverse,

71 | in_real => in_real,

72 | in_imag => in_imag,

73 | in_valid => in_valid,

74 | in_sop => in_sop,

75 | in_eop => in_eop,

76 |

77 | out_real => out_real,

78 | out_imag => out_imag,

79 | out_error => out_error,

80 | out_valid => out_valid,

81 | out_sop => out_sop,

82 | out_eop => out_eop

83 | );

84 |

85 |

86 |

87 | end architecture;

88 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/fft/vhdl/tb/compile.do:

--------------------------------------------------------------------------------

1 | vcom -work work -2008 ../dual_port_ram.vhd

2 | vcom -work work -2008 ../fft.vhd

3 | vcom -work work -2008 fft_tb.vhd

4 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/fft/vhdl/tb/fft_tb.vhd:

--------------------------------------------------------------------------------

1 | -- This file is part of bladeRF-wiphy.

2 | --

3 | -- Copyright (C) 2021 Nuand, LLC.

4 | --

5 | -- This program is free software; you can redistribute it and/or modify

6 | -- it under the terms of the GNU General Public License as published by

7 | -- the Free Software Foundation; either version 2 of the License, or

8 | -- (at your option) any later version.

9 | --

10 | -- This program is distributed in the hope that it will be useful,

11 | -- but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | -- MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | -- GNU General Public License for more details.

14 | --

15 | -- You should have received a copy of the GNU General Public License along

16 | -- with this program; if not, write to the Free Software Foundation, Inc.,

17 | -- 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | library ieee;

20 | use ieee.std_logic_1164.all;

21 | use ieee.numeric_std.all;

22 |

23 | entity fft_tb is

24 | end entity;

25 |

26 | architecture arch of fft_tb is

27 | signal clock : std_logic := '0';

28 | signal reset : std_logic;

29 |

30 | signal in_real : std_logic_vector(15 downto 0);

31 | signal in_imag : std_logic_vector(15 downto 0);

32 | signal in_valid : std_logic;

33 | signal in_sop : std_logic;

34 | signal in_eop : std_logic;

35 |

36 | type lut_t is array(natural range <>) of integer;

37 |

38 | signal lut : lut_t(0 to 127) := (

39 | 750, 402, 700, -439, -96, 909, -496, -7, -711, 76, 601, 764, 315, -192, -633, 411,

40 | -139, -540, -640, -360, -172, 821, 291, 160, -678, 9, -241, -679, -293, 69, -172, 565,

41 | 999, -356, -19, 515, -498, 438, 693, 78, 209, -276, 131, -865, 487, 465, 35, 454,

42 | 437, -480, -45, -324, -991, -86, 2, -471, -38, -805, -621, 543, 397, 170, 606, -797,

43 | 369, 546, 591, 150, -17, -1095, -684, 109, -450, 760, -478, -573, -409, -66, 484, 682,

44 | 201, -826, -192, -695, 819, 16, 172, -403, -660, -342, 14, 443, -389, 544, -339, -734,

45 | -141, -366, -626, 381, 382, 280, 235, 624, -980, -218, 54, 333, 506, 333, 114, -944,

46 | 566, 46, -48, 305, -20, 457, 740, -56, 197, -919, 295, 522, 20, -2, -712, 438

47 | );

48 |

49 | signal ilut : lut_t(0 to 63) := (

50 | 0, 1, -1, -1, -1, 1, -1, 1, -1, -1, -1, 1, 1, -1, -1, 1, -1, 1, 1, -1, -1, -1, -1,

51 | -1, 1, -1, -1, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 1, 1, -1, 1, 1, 1, -1, 1, 1, -1,

52 | -1, -1, -1, 1, -1, -1, -1, -1, -1, 1, 1, -1, -1, 1, 1, -1 );

53 |

54 |

55 |

56 |

57 | constant N : integer := 64;

58 | begin

59 | clock <= not clock after 6.25 ns;

60 | reset <= '1', '0' after 50 ns;

61 |

62 | process

63 | begin

64 | in_real <= ( others => '0' );

65 | in_imag <= ( others => '0' );

66 | in_valid <= '0';

67 | in_sop <= '0';

68 | in_eop <= '0';

69 | wait for 100 ns;

70 | for iz in 0 to 80 loop

71 | for i in 0 to N-1 loop

72 | wait until rising_edge(clock);

73 | in_real <= std_logic_vector(to_signed(4096*ilut(i), in_real'high + 1));

74 | in_imag <= ( others => '0' ); --std_logic_vector(to_signed(lut(i*2+1), in_real'high + 1));

75 | in_valid <= '1';

76 | if (i = 0) then

77 | in_sop <= '1';

78 | else

79 | in_sop <= '0';

80 | end if;

81 |

82 | if (i = N-1) then

83 | in_eop <= '1';

84 | else

85 | in_eop <= '0';

86 | end if;

87 | end loop;

88 |

89 | wait until rising_edge(clock);

90 | in_valid <= '0';

91 | in_sop <= '0';

92 | in_eop <= '0';

93 | wait for 500 ns;

94 | end loop;

95 | wait for 5 ms;

96 | end process;

97 |

98 | U_uut: entity work.fft(mult)

99 | generic map(

100 | N => N

101 | )

102 | port map(

103 | clock => clock,

104 | reset => reset,

105 |

106 | inverse => '1',

107 | in_real => in_real,

108 | in_imag => in_imag,

109 | in_valid => in_valid,

110 | in_sop => in_sop,

111 | in_eop => in_eop,

112 |

113 | out_real => open,

114 | out_imag => open,

115 | out_error => open,

116 | out_valid => open

117 | );

118 |

119 | end architecture;

120 |

121 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/nco.vhd:

--------------------------------------------------------------------------------

1 | -- This file is part of bladeRF-wiphy.

2 | --

3 | -- Copyright (C) 2020 Nuand, LLC.

4 | --

5 | -- This program is free software; you can redistribute it and/or modify

6 | -- it under the terms of the GNU General Public License as published by

7 | -- the Free Software Foundation; either version 2 of the License, or

8 | -- (at your option) any later version.

9 | --

10 | -- This program is distributed in the hope that it will be useful,

11 | -- but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | -- MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | -- GNU General Public License for more details.

14 | --

15 | -- You should have received a copy of the GNU General Public License along

16 | -- with this program; if not, write to the Free Software Foundation, Inc.,

17 | -- 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | library ieee ;

20 | use ieee.std_logic_1164.all ;

21 | use ieee.numeric_std.all ;

22 |

23 | package nco_p is

24 |

25 | type nco_input_t is record

26 | dphase : signed(15 downto 0) ;

27 | valid : std_logic ;

28 | end record ;

29 |

30 | type nco_output_t is record

31 | re : signed(15 downto 0) ;

32 | im : signed(15 downto 0) ;

33 | valid : std_logic ;

34 | end record ;

35 |

36 | end package ; -- nco_p

37 |

38 | library ieee ;

39 | use ieee.std_logic_1164.all ;

40 | use ieee.numeric_std.all ;

41 |

42 | library work ;

43 | use work.cordic_p.all ;

44 | use work.nco_p.all ;

45 |

46 | entity nco is

47 | port (

48 | clock : in std_logic ;

49 | reset : in std_logic ;

50 | inputs : in nco_input_t ;

51 | outputs : out nco_output_t

52 | ) ;

53 | end entity ; -- nco

54 |

55 | architecture arch of nco is

56 |

57 | signal phase : signed(15 downto 0) ;

58 |

59 | signal cordic_inputs : cordic_xyz_t ;

60 | signal cordic_outputs : cordic_xyz_t ;

61 |

62 | begin

63 |

64 | accumulate_phase : process(clock, reset)

65 | variable temp : signed(15 downto 0) ;

66 | begin

67 | if( reset = '1' ) then

68 | phase <= (others =>'0') ;

69 | elsif( rising_edge( clock ) ) then

70 | if( inputs.valid = '1' ) then

71 | temp := phase + inputs.dphase ;

72 | if( temp > 16384 ) then

73 | temp := temp - 32768 ;

74 | elsif( temp < -16384 ) then

75 | temp := temp + 32768 ;

76 | end if ;

77 | phase <= temp ;

78 | end if ;

79 | end if ;

80 | end process ;

81 |

82 | cordic_inputs <= ( x => to_signed(1234,16), y => to_signed(0,16), z => phase, valid => inputs.valid ) ;

83 |

84 | U_cordic : entity work.cordic

85 | port map (

86 | clock => clock,

87 | reset => reset,

88 | mode => CORDIC_ROTATION,

89 | inputs => cordic_inputs,

90 | outputs => cordic_outputs

91 | ) ;

92 |

93 | outputs.re <= cordic_outputs.x ;

94 | outputs.im <= cordic_outputs.y ;

95 | outputs.valid <= cordic_outputs.valid ;

96 |

97 | end architecture ; -- arch

98 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/viterbi_decoder/model/out.c:

--------------------------------------------------------------------------------

1 | // This file is part of bladeRF-wiphy.

2 | //

3 | // Copyright (C) 2021 Nuand, LLC.

4 | //

5 | // This program is free software; you can redistribute it and/or modify

6 | // it under the terms of the GNU General Public License as published by

7 | // the Free Software Foundation; either version 2 of the License, or

8 | // (at your option) any later version.

9 | //

10 | // This program is distributed in the hope that it will be useful,

11 | // but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | // MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | // GNU General Public License for more details.

14 | //

15 | // You should have received a copy of the GNU General Public License along

16 | // with this program; if not, write to the Free Software Foundation, Inc.,

17 | // 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | #include

20 | #include

21 | #include

22 | #include

23 | #include

24 |

25 | #define K 7

26 | #define C_A 91

27 | #define C_B 121

28 |

29 | #define BIT(y) ( (state >> y) & 1)

30 |

31 | #define T_BIT(y) ( (t_state >> y) & 1)

32 |

33 | int main(int argc, char *argv[]) {

34 | unsigned t_state;

35 | unsigned next_state;

36 | uint8_t t_bit_a, t_bit_b;

37 | for (t_state = 0; t_state <= 0x3f; t_state++) {

38 | // bit is 0?

39 | t_bit_a = T_BIT(5) ^ T_BIT(4) ^ T_BIT(2) ^ T_BIT(1) ^ 0;

40 | t_bit_b = T_BIT(5) ^ T_BIT(2) ^ T_BIT(1) ^ T_BIT(0) ^ 0;

41 | next_state = (t_state << 1) & 0x3f;

42 | printf("S[%d] -- bit=%d coded=%d,%d -- D[%d]\n", t_state, 0, t_bit_a, t_bit_b, next_state);

43 |

44 | // bit is 1?

45 | t_bit_a = T_BIT(5) ^ T_BIT(4) ^ T_BIT(2) ^ T_BIT(1) ^ 1;

46 | t_bit_b = T_BIT(5) ^ T_BIT(2) ^ T_BIT(1) ^ T_BIT(0) ^ 1;

47 | next_state = ((t_state << 1) & 0x3f) | 1;

48 | printf("S[%d] -- bit=%d coded=%d,%d -- D[%d]\n", t_state, 1, t_bit_a, t_bit_b, next_state);

49 | }

50 | return 0;

51 | }

52 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/viterbi_decoder/vhdl/branch_compare.vhd:

--------------------------------------------------------------------------------

1 | -- This file is part of bladeRF-wiphy.

2 | --

3 | -- Copyright (C) 2021 Nuand, LLC.

4 | --

5 | -- This program is free software; you can redistribute it and/or modify

6 | -- it under the terms of the GNU General Public License as published by

7 | -- the Free Software Foundation; either version 2 of the License, or

8 | -- (at your option) any later version.

9 | --

10 | -- This program is distributed in the hope that it will be useful,

11 | -- but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | -- MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | -- GNU General Public License for more details.

14 | --

15 | -- You should have received a copy of the GNU General Public License along

16 | -- with this program; if not, write to the Free Software Foundation, Inc.,

17 | -- 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | library ieee;

20 | use ieee.std_logic_1164.all;

21 | use ieee.numeric_std.all;

22 |

23 | library work;

24 | use work.viterbi_p.all;

25 |

26 | entity branch_compare is

27 | generic(

28 | RESET_ACTIVE : boolean := false;

29 | REG_UNCODED : boolean := false

30 | );

31 | port(

32 | clock : in std_logic;

33 | reset : in std_logic;

34 |

35 | bm_a : in unsigned(15 downto 0);

36 | bm_b : in unsigned(15 downto 0);

37 | bm_valid : in std_logic;

38 |

39 | path_in_a : in path_t;

40 | path_in_b : in path_t;

41 |

42 | branch : in branch_inputs_t;

43 | path_out : out path_t;

44 |

45 | win : out std_logic

46 | );

47 | end entity;

48 |

49 | architecture arch of branch_compare is

50 | begin

51 |

52 | process(reset, clock)

53 | variable cost_a, cost_b : unsigned(path_in_a.cost'range);

54 | begin

55 | if (reset = '1') then

56 | path_out <= NULL_PATH_RST(RESET_ACTIVE);

57 | win <= '0';

58 | elsif (rising_edge(clock)) then

59 | if (bm_valid = '1') then

60 | cost_a := path_in_a.cost + bm_a;

61 | cost_b := path_in_b.cost + bm_b;

62 |

63 | if ((path_in_a.cost = (path_in_a.cost'range => '1')) and

64 | (path_in_b.cost = (path_in_b.cost'range => '1'))) then

65 | win <= '0';

66 | path_out.cost <= ( others => '1' );

67 | elsif (path_in_a.cost = (path_in_a.cost'range => '1')) then

68 | win <= '1';

69 | path_out.cost <= cost_b;

70 | elsif (path_in_b.cost = (path_in_b.cost'range => '1')) then

71 | win <= '0';

72 | path_out.cost <= cost_a;

73 | else

74 | if (cost_b < cost_a) then

75 | win <= '1';

76 | path_out.cost <= cost_b;

77 | else

78 | win <= '0';

79 | path_out.cost <= cost_a;

80 | end if;

81 | end if;

82 | end if;

83 | end if;

84 | end process;

85 | end architecture;

86 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/viterbi_decoder/vhdl/comp2.vhd:

--------------------------------------------------------------------------------

1 | -- This file is part of bladeRF-wiphy.

2 | --

3 | -- Copyright (C) 2021 Nuand, LLC.

4 | --

5 | -- This program is free software; you can redistribute it and/or modify

6 | -- it under the terms of the GNU General Public License as published by

7 | -- the Free Software Foundation; either version 2 of the License, or

8 | -- (at your option) any later version.

9 | --

10 | -- This program is distributed in the hope that it will be useful,

11 | -- but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | -- MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | -- GNU General Public License for more details.

14 | --

15 | -- You should have received a copy of the GNU General Public License along

16 | -- with this program; if not, write to the Free Software Foundation, Inc.,

17 | -- 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | library ieee;

20 | use ieee.std_logic_1164.all;

21 | use ieee.numeric_std.all;

22 |

23 | library work;

24 | use work.viterbi_p.all;

25 |

26 | entity comp2 is

27 | port(

28 | clock : in std_logic;

29 | reset : in std_logic;

30 |

31 | path_name_a : in path_name_t;

32 | path_name_b : in path_name_t;

33 | path_valid : in std_logic;

34 |

35 | path_name_out : out path_name_t

36 | );

37 | end entity;

38 |

39 | architecture arch of comp2 is

40 | begin

41 | process(clock, reset)

42 | begin

43 | if (reset = '1') then

44 | path_name_out.name <= (others => '0');

45 | path_name_out.path <= NULL_PATH_T;

46 | elsif (rising_edge(clock)) then

47 | if (path_valid = '1') then

48 | if (path_name_b.path.cost < path_name_a.path.cost) then

49 | path_name_out <= path_name_b;

50 | else

51 | path_name_out <= path_name_a;

52 | end if;

53 | end if;

54 | end if;

55 | end process;

56 | end architecture;

57 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/viterbi_decoder/vhdl/r2_comparator.vhd:

--------------------------------------------------------------------------------

1 | -- This file is part of bladeRF-wiphy.

2 | --

3 | -- Copyright (C) 2021 Nuand, LLC.

4 | --

5 | -- This program is free software; you can redistribute it and/or modify

6 | -- it under the terms of the GNU General Public License as published by

7 | -- the Free Software Foundation; either version 2 of the License, or

8 | -- (at your option) any later version.

9 | --

10 | -- This program is distributed in the hope that it will be useful,

11 | -- but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | -- MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | -- GNU General Public License for more details.

14 | --

15 | -- You should have received a copy of the GNU General Public License along

16 | -- with this program; if not, write to the Free Software Foundation, Inc.,

17 | -- 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | library ieee;

20 | use ieee.std_logic_1164.all;

21 | use ieee.numeric_std.all;

22 |

23 | library work;

24 | use work.viterbi_p.all;

25 |

26 | entity r2_comparator is

27 | generic(

28 | NUM_PATHS : in natural := 64;

29 | STATE_BITS : in natural := 6

30 | );

31 | port(

32 | clock : in std_logic;

33 | reset : in std_logic;

34 |

35 | paths : in path_arr_t(NUM_PATHS-1 downto 0);

36 | path_valid : in std_logic;

37 |

38 | label_out : out unsigned(STATE_BITS-1 downto 0);

39 | valid_out : out std_logic

40 | );

41 | end entity;

42 |

43 | architecture arch of r2_comparator is

44 | type path_name_arr_arr_t is array(natural range <>) of path_name_arr_t(NUM_PATHS-1 downto 0);

45 |

46 | signal r2_matrix : path_name_arr_arr_t(STATE_BITS downto 0);

47 |

48 | signal valid_out_r : std_logic_vector(STATE_BITS - 1 downto 1);

49 | begin

50 | gen_init_path: for i in paths'range generate

51 | r2_matrix(0)(i).path <= paths(i);

52 | r2_matrix(0)(i).name <= to_unsigned(i, 6);

53 | end generate;

54 |

55 | process(clock, reset)

56 | begin

57 | if (reset = '1') then

58 | valid_out_r <= ( others => '0' );

59 | valid_out <= '0';

60 | elsif (rising_edge(clock)) then

61 | if (path_valid = '1') then

62 | valid_out_r <= path_valid & valid_out_r(valid_out_r'high downto 2);

63 | valid_out <= valid_out_r(1);

64 | else

65 | valid_out <= '0';

66 | end if;

67 | end if;

68 | end process;

69 |

70 | gen_cs: for cs_i in 1 to STATE_BITS generate

71 | gen_rs: for rs_i in 0 to NUM_PATHS/(2**cs_i)-1 generate

72 | U_comp2 : entity work.comp2

73 | port map(

74 | clock => clock,

75 | reset => reset,

76 |

77 | path_name_a => r2_matrix(cs_i-1)(rs_i * 2),

78 | path_name_b => r2_matrix(cs_i-1)(rs_i * 2 + 1),

79 | path_valid => path_valid,

80 | path_name_out => r2_matrix(cs_i)(rs_i)

81 | );

82 | end generate;

83 | end generate;

84 |

85 | label_out <= r2_matrix(r2_matrix'high)(0).name;

86 |

87 | end architecture;

88 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/viterbi_decoder/vhdl/tb/compile.do:

--------------------------------------------------------------------------------

1 | vcom -work work -2008 ../viterbi_p.vhd

2 | vcom -work work -2008 ../tracer.vhd

3 | vcom -work work -2008 ../comp2.vhd

4 | vcom -work work -2008 ../r2_comparator.vhd

5 | vcom -work work -2008 ../branch_compare.vhd

6 | vcom -work work -2008 ../traceback.vhd

7 | vcom -work work -2008 ../viterbi_decoder.vhd

8 | vcom -work work -2008 viterbi_decoder_tb.vhd

9 | vcom -work work -2008 r2_comparator_tb.vhd

10 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/viterbi_decoder/vhdl/tb/r2_comparator_tb.vhd:

--------------------------------------------------------------------------------

1 | -- This file is part of bladeRF-wiphy.

2 | --

3 | -- Copyright (C) 2021 Nuand, LLC.

4 | --

5 | -- This program is free software; you can redistribute it and/or modify

6 | -- it under the terms of the GNU General Public License as published by

7 | -- the Free Software Foundation; either version 2 of the License, or

8 | -- (at your option) any later version.

9 | --

10 | -- This program is distributed in the hope that it will be useful,

11 | -- but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | -- MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | -- GNU General Public License for more details.

14 | --

15 | -- You should have received a copy of the GNU General Public License along

16 | -- with this program; if not, write to the Free Software Foundation, Inc.,

17 | -- 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | library ieee;

20 | use ieee.std_logic_1164.all;

21 | use ieee.numeric_std.all;

22 |

23 | library work;

24 | use work.viterbi_p.all;

25 |

26 | entity r2_comparator_tb is

27 | end entity;

28 |

29 | architecture behv of r2_comparator_tb is

30 | signal clock : std_logic := '0';

31 | signal reset : std_logic;

32 | signal valid : std_logic;

33 | signal paths : path_arr_t(63 downto 0);

34 |

35 | begin

36 | clock <= not clock after 10 ns;

37 | reset <= '1', '0' after 100 ns;

38 | valid <= '0', '1' after 198 ns, '0' after 548 ns;

39 |

40 | process

41 | variable i : integer;

42 | variable t_cost : integer;

43 | begin

44 | for i in paths'range loop

45 | if (i = 51) then

46 | t_cost := 10;

47 | else

48 | t_cost := 100 + i;

49 | end if;

50 | paths(i).cost <= to_unsigned(t_cost, paths(i).cost'high + 1);

51 | paths(i).active <= '0';

52 | end loop;

53 | wait;

54 | end process;

55 |

56 |

57 | U_uut: entity work.r2_comparator

58 | port map(

59 | clock => clock,

60 | reset => reset,

61 |

62 | paths => paths,

63 | path_valid => valid,

64 |

65 | label_out => open,

66 | valid_out => open

67 | );

68 | end architecture;

69 |

70 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/viterbi_decoder/vhdl/traceback.vhd:

--------------------------------------------------------------------------------

1 | -- This file is part of bladeRF-wiphy.

2 | --

3 | -- Copyright (C) 2021 Nuand, LLC.

4 | --

5 | -- This program is free software; you can redistribute it and/or modify

6 | -- it under the terms of the GNU General Public License as published by

7 | -- the Free Software Foundation; either version 2 of the License, or

8 | -- (at your option) any later version.

9 | --

10 | -- This program is distributed in the hope that it will be useful,

11 | -- but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | -- MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | -- GNU General Public License for more details.

14 | --

15 | -- You should have received a copy of the GNU General Public License along

16 | -- with this program; if not, write to the Free Software Foundation, Inc.,

17 | -- 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | library ieee;

20 | use ieee.std_logic_1164.all;

21 | use ieee.numeric_std.all;

22 |

23 | library work;

24 | use work.viterbi_p.all;

25 |

26 | entity traceback is

27 | generic(

28 | STATE_BITS : in integer;

29 | NUM_STATES : in integer;

30 | TB_LEN : in integer

31 | );

32 | port(

33 | clock : in std_logic;

34 | reset : in std_logic;

35 |

36 | acs_reg : in std_logic_vector(NUM_STATES-1 downto 0);

37 | acs_valid : in std_logic;

38 |

39 | best_idx : in unsigned(STATE_BITS-1 downto 0);

40 | best_valid : in std_logic;

41 |

42 | bit_out : out std_logic;

43 | valid_out : out std_logic

44 | );

45 | end entity;

46 |

47 | architecture arch of traceback is

48 | type history_t is array(7 + TB_LEN*2 downto 0) of std_logic_vector(NUM_STATES-1 downto 0);

49 |

50 | type fsm_t is (IDLE, START_TRACER);

51 |

52 | type state_t is record

53 | fsm : fsm_t;

54 | loaded : std_logic;

55 | history : history_t;

56 | acs_count : natural range 0 to TB_LEN+STATE_BITS*2;

57 | acs_enough : std_logic;

58 | bit_out : std_logic;

59 | valid_out : std_logic;

60 | end record;

61 |

62 | function NULL_STATE_T return state_t is

63 | variable ret : state_t;

64 | begin

65 | ret.fsm := IDLE;

66 | ret.loaded := '0';

67 | for i in ret.history'range loop

68 | ret.history(i) := ( others => '0' );

69 | end loop;

70 | ret.acs_count := 0;

71 | ret.acs_enough := '0';

72 | ret.bit_out := '0';

73 | ret.valid_out := '0';

74 | return(ret);

75 | end function;

76 |

77 | signal current, future : state_t := NULL_STATE_T;

78 |

79 | type trace_state_t is array(TB_LEN downto 0) of unsigned(STATE_BITS-1 downto 0);

80 |

81 | signal trace_state : trace_state_t;

82 | signal trace_state_valid : std_logic_vector(TB_LEN downto 0);

83 | begin

84 | sync : process(clock, reset)

85 | begin

86 | if (reset = '1') then

87 | current <= NULL_STATE_T;

88 | elsif (rising_edge(clock)) then

89 | current <= future;

90 | end if;

91 | end process;

92 |

93 | trace_state(0) <= best_idx;

94 | trace_state_valid(0) <= current.acs_enough;

95 |

96 | gen_tracers: for i in 0 to TB_LEN-1 generate

97 | U_tracer: entity work.tracer

98 | generic map(

99 | STATE_BITS => STATE_BITS,

100 | NUM_STATES => NUM_STATES

101 | )

102 | port map(

103 | clock => clock,

104 | reset => reset,

105 |

106 | state_in => trace_state(i),

107 | state_valid => trace_state_valid(i),

108 | acs_reg => current.history(6 + 2 * i),

109 | acs_valid => acs_valid,

110 |

111 | state_out => trace_state(i+1),

112 | valid_out => trace_state_valid(i+1)

113 | );

114 | end generate;

115 |

116 |

117 | bit_out <= current.bit_out;

118 | valid_out <= current.valid_out;

119 |

120 | comb : process(all)

121 | begin

122 | future <= current;

123 |

124 | future.bit_out <= '0';

125 | future.valid_out <= '0';

126 |

127 | if (acs_valid = '1') then

128 | if (current.acs_enough = '0') then

129 | if (current.acs_count = TB_LEN + 6 + 5) then

130 | future.acs_enough <= '1';

131 | else

132 | future.acs_count <= current.acs_count + 1;

133 | end if;

134 | end if;

135 | future.history <= current.history(current.history'high-1 downto 0) & acs_reg;

136 | end if;

137 |

138 | case current.fsm is

139 | when IDLE =>

140 | if (current.acs_enough = '1' and acs_valid = '1') then

141 | future.fsm <= START_TRACER;

142 | end if;

143 | when START_TRACER =>

144 | if (acs_valid = '1') then

145 | -- the bit that is about to be shifted out is actually the uncoded bit

146 | -- the new bit that is shifted in is from the current branch, the historical ACS reg basically determines the LSB of the new state

147 | future.bit_out <= trace_state(TB_LEN)(5);

148 | future.valid_out <= trace_state_valid(TB_LEN);

149 | end if;

150 | when others =>

151 | future <= NULL_STATE_T;

152 | end case;

153 | end process;

154 |

155 | end architecture;

156 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/viterbi_decoder/vhdl/tracer.vhd:

--------------------------------------------------------------------------------

1 | -- This file is part of bladeRF-wiphy.

2 | --

3 | -- Copyright (C) 2021 Nuand, LLC.

4 | --

5 | -- This program is free software; you can redistribute it and/or modify

6 | -- it under the terms of the GNU General Public License as published by

7 | -- the Free Software Foundation; either version 2 of the License, or

8 | -- (at your option) any later version.

9 | --

10 | -- This program is distributed in the hope that it will be useful,

11 | -- but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | -- MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | -- GNU General Public License for more details.

14 | --

15 | -- You should have received a copy of the GNU General Public License along

16 | -- with this program; if not, write to the Free Software Foundation, Inc.,

17 | -- 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | library ieee;

20 | use ieee.std_logic_1164.all;

21 | use ieee.numeric_std.all;

22 |

23 | library work;

24 | use work.viterbi_p.all;

25 |

26 | entity tracer is

27 | generic(

28 | STATE_BITS : in integer;

29 | NUM_STATES : in integer

30 | );

31 | port(

32 | clock : in std_logic;

33 | reset : in std_logic;

34 |

35 | state_in : in unsigned(STATE_BITS-1 downto 0);

36 | state_valid : in std_logic;

37 | acs_reg : in std_logic_vector(NUM_STATES-1 downto 0);

38 | acs_valid : in std_logic;

39 |

40 | state_out : out unsigned(STATE_BITS-1 downto 0);

41 | valid_out : out std_logic

42 | );

43 | end entity;

44 |

45 | architecture arch of tracer is

46 | begin

47 | process(clock, reset)

48 | variable s_bit : std_logic;

49 | begin

50 | if (reset='1') then

51 | state_out <= ( others => '0' );

52 | valid_out <= '0';

53 | elsif (rising_edge(clock)) then

54 | s_bit := acs_reg(to_integer(state_in));

55 | if (acs_valid = '1') then

56 | state_out <= s_bit & state_in(state_in'high downto 1);

57 | valid_out <= state_valid;

58 | end if;

59 | end if;

60 | end process;

61 | end architecture;

62 |

--------------------------------------------------------------------------------

/fpga/ip/nuand/viterbi_decoder/vhdl/viterbi_p.vhd:

--------------------------------------------------------------------------------

1 | -- This file is part of bladeRF-wiphy.

2 | --

3 | -- Copyright (C) 2021 Nuand, LLC.

4 | --

5 | -- This program is free software; you can redistribute it and/or modify

6 | -- it under the terms of the GNU General Public License as published by

7 | -- the Free Software Foundation; either version 2 of the License, or

8 | -- (at your option) any later version.

9 | --

10 | -- This program is distributed in the hope that it will be useful,

11 | -- but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | -- MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | -- GNU General Public License for more details.

14 | --

15 | -- You should have received a copy of the GNU General Public License along

16 | -- with this program; if not, write to the Free Software Foundation, Inc.,

17 | -- 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | library ieee;

20 | use ieee.std_logic_1164.all;

21 | use ieee.numeric_std.all;

22 |

23 | package viterbi_p is

24 | type path_t is record

25 | --- path metric stuff

26 | cost : unsigned(23 downto 0);

27 | active : std_logic;

28 | end record;

29 | type path_arr_t is array(natural range <>) of path_t;

30 |

31 | type path_name_t is record

32 | path : path_t;

33 | name : unsigned(5 downto 0);

34 | end record;

35 |

36 | type path_name_arr_t is array(natural range <>) of path_name_t;

37 |

38 |

39 | type branch_t is record

40 | -- starting conditions

41 | start_state : natural;

42 | u_bit : std_logic;

43 |

44 | -- internal state keeping

45 | bit_s : std_logic;

46 | set : boolean;

47 |

48 | -- output

49 | bit_a : std_logic;

50 | bit_b : std_logic;

51 | bm_idx : integer;

52 |

53 | -- final state

54 | prev_state : integer;

55 | next_state : integer;

56 | end record;

57 |

58 | type branch_inputs_t is array(1 downto 0) of branch_t;

59 |

60 | type bsd_t is array(natural range <>) of unsigned(7 downto 0);

61 |

62 | type bm_t is array(natural range <>) of unsigned(15 downto 0);

63 |

64 | function NULL_PATH_RST(init_state : boolean) return path_t;

65 | function NULL_PATH_T return path_t;

66 | end package;

67 |

68 | package body viterbi_p is

69 | function NULL_PATH_RST(init_state : boolean) return path_t is

70 | variable ret : path_t;

71 | begin

72 | if (init_state) then

73 | ret.cost := ( others => '0' );

74 | else

75 | ret.cost := ( others => '1' );

76 | end if;

77 | ret.active := '0';

78 | return ret;

79 | end function;

80 |

81 | function NULL_PATH_T return path_t is

82 | begin

83 | return NULL_PATH_RST(false);

84 | end function;

85 | end package body;

86 |

--------------------------------------------------------------------------------

/fpga/modelsim/wlan.do:

--------------------------------------------------------------------------------

1 | # Library

2 | vlib wlan

3 |

4 | if { ! [info exists wlan_path] } {

5 | set wlan_path "."

6 | }

7 |

8 | set modelsim 1

9 |

10 | vlib nuand

11 | vcom -work nuand -2008 [file join $wlan_path ../../../bladeRF/hdl/fpga/ip/nuand/synthesis/fifo_readwrite_p.vhd ]

12 |

13 | # altera ip simulation models

14 | vlib fft64

15 |

16 | set QSYS_SIMDIR [file normalize [ file join $wlan_path ../ip/altera/fft64/fft64/simulation/ ] ]

17 | source [file normalize [ file join $wlan_path $QSYS_SIMDIR/mentor/msim_setup.tcl ] ]

18 | dev_com

19 | com

20 | vmap fft64 libraries/fft_ii_0/

21 |

22 | vlog -work fft64 [ file join $wlan_path ../ip/altera/fft64/fft64/simulation/fft64.v ]

23 | set hexfiles [glob [file join $wlan_path "../ip/altera/fft64/fft64/simulation/submodules/*.hex"] ]

24 | foreach f $hexfiles {

25 | file copy -force $f .

26 | }

27 |

28 | vlib viterbi_decoder

29 | set QSYS_SIMDIR [file normalize [ file join $wlan_path ../ip/altera/viterbi_decoder/viterbi_decoder/simulation/ ] ]

30 | source [file normalize [ file join $wlan_path $QSYS_SIMDIR/mentor/msim_setup.tcl ] ]

31 | dev_com

32 | com

33 | vmap viterbi_decoder libraries/viterbi_ii_0/

34 |

35 | vlog -work viterbi_decoder [ file join $wlan_path ../ip/altera/viterbi_decoder/viterbi_decoder/simulation/viterbi_decoder.v ]

36 | vlog -work viterbi_decoder [ file join $wlan_path ../ip/altera/viterbi_decoder/viterbi_decoder/simulation/submodules/viterbi_decoder_viterbi_ii_0.v ]

37 |

38 |

39 | vlib wlan_pll

40 | vlog -work wlan_pll [ file join $wlan_path ../ip/altera/wlan_pll/wlan_pll/wlan_pll.v ]

41 |

42 | source [file normalize [ file join $wlan_path ../common/wlan_files.tcl ] ]

43 |

44 | # Common packages

45 | foreach f $wlan_common {

46 | vcom -work wlan -2008 $f

47 | }

48 |

49 | # TX Synthesis

50 | foreach f $wlan_synthesis_tx {

51 | vcom -work wlan -2008 $f

52 | }

53 |

54 | # RX Synthesis

55 | foreach f $wlan_synthesis_rx {

56 | vcom -work wlan -2008 $f

57 | }

58 |

59 | # Top Level Synthesis

60 | foreach f $wlan_synthesis_top {

61 | vcom -work wlan -2008 $f

62 | }

63 |

64 | # Simulation

65 | foreach f $wlan_sim {

66 | vcom -work wlan -2008 $f

67 | }

68 |

69 | proc wlan_sim_entity { entity } {

70 | vsim -t ps -L work -L work_lib -L fft_ii_0 -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L wlan -L fft64 -L viterbi_decoder -L altera_lnsim_ver $entity

71 | }

72 |

73 | alias tb_wlan_rx {

74 | wlan_sim_entity wlan_rx_tb

75 | }

76 |

--------------------------------------------------------------------------------

/fpga/quartus/wlan.qip:

--------------------------------------------------------------------------------

1 | # Altera FFT IP

2 | set_global_assignment -name QIP_FILE [file normalize "../../../../../bladeRF-wiphy/fpga/ip/altera/fft64/fft64/synthesis/fft64.qip"]

3 | set_global_assignment -name QIP_FILE [file normalize "../../../../../bladeRF-wiphy/fpga/ip/altera/viterbi_decoder/viterbi_decoder/synthesis/viterbi_decoder.qip"]

4 | set_global_assignment -library "wlan_pll" -name VERILOG_FILE [file normalize "../../../../../bladeRF-wiphy/fpga/ip/altera/wlan_pll/wlan_pll/wlan_pll.v"]

5 | set_global_assignment -library "wlan_pll" -name QIP_FILE [file normalize "../../../../../bladeRF-wiphy/fpga/ip/altera/wlan_pll/wlan_pll/wlan_pll.qip"]

6 |

7 | set modelsim 0

8 |

9 | # Nuand WLAN IP files

10 | source [file normalize [file join $::quartus(qip_path) ../common/wlan_files.tcl]]

11 | foreach f $wlan_common {

12 | set_global_assignment -library "wlan" -name VHDL_FILE [file normalize [file join $::quartus(qip_path) $f]] -hdl_version VHDL_2008

13 | }

14 |

15 | foreach f $wlan_synthesis_tx {

16 | set_global_assignment -library "wlan" -name VHDL_FILE [file normalize [file join $::quartus(qip_path) $f]] -hdl_version VHDL_2008

17 | }

18 |

19 | foreach f $wlan_synthesis_rx {

20 | set_global_assignment -library "wlan" -name VHDL_FILE [file normalize [file join $::quartus(qip_path) $f]] -hdl_version VHDL_2008

21 | }

22 |

23 | foreach f $wlan_synthesis_top {

24 | set_global_assignment -library "wlan" -name VHDL_FILE [file normalize [file join $::quartus(qip_path) $f]] -hdl_version VHDL_2008

25 | }

26 |

27 |

--------------------------------------------------------------------------------

/fpga/vhdl/clock_sync_logic.vhd:

--------------------------------------------------------------------------------

1 | -- This file is part of bladeRF-wiphy.

2 | --

3 | -- Copyright (C) 2020 Nuand, LLC.

4 | --

5 | -- This program is free software; you can redistribute it and/or modify

6 | -- it under the terms of the GNU General Public License as published by

7 | -- the Free Software Foundation; either version 2 of the License, or

8 | -- (at your option) any later version.

9 | --

10 | -- This program is distributed in the hope that it will be useful,

11 | -- but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | -- MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | -- GNU General Public License for more details.

14 | --

15 | -- You should have received a copy of the GNU General Public License along

16 | -- with this program; if not, write to the Free Software Foundation, Inc.,

17 | -- 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | library ieee ;

20 | use ieee.std_logic_1164.all ;

21 | use ieee.numeric_std.all ;

22 |

23 | library wlan ;

24 | use wlan.wlan_rx_p.all ;

25 |

26 | entity clock_sync_logic is

27 | port (

28 | from_signal : in std_logic ;

29 |

30 | to_clock : in std_logic ;

31 | to_reset : in std_logic ;

32 |

33 | to_signal : out std_logic

34 | ) ;

35 | end entity;

36 |

37 | architecture arch of clock_sync_logic is

38 |

39 | signal t_sig_r : std_logic ;

40 | signal t_sig_rr : std_logic ;

41 |

42 | attribute ALTERA_ATTRIBUTE : string;

43 |

44 | attribute ALTERA_ATTRIBUTE of arch: architecture is "-name SDC_STATEMENT ""set_false_path -to [get_registers *clock_sync_logic|*_r* ] "" ";

45 |

46 | begin

47 |

48 | process(all)

49 | begin

50 | if( to_reset = '1' ) then

51 | t_sig_rr <= '0' ;

52 | t_sig_r <= '0' ;

53 | to_signal <= '0' ;

54 | elsif( rising_edge( to_clock ) ) then

55 | t_sig_r <= from_signal ;

56 | t_sig_rr <= t_sig_r ;

57 | if( t_sig_rr = '0' and t_sig_r = '1' ) then

58 | to_signal <= '1' ;

59 | else

60 | to_signal <= '0' ;

61 | end if ;

62 | end if ;

63 | end process ;

64 |

65 | end architecture ;

66 |

--------------------------------------------------------------------------------

/fpga/vhdl/clock_sync_logic_vector.vhd:

--------------------------------------------------------------------------------

1 | -- This file is part of bladeRF-wiphy.

2 | --

3 | -- Copyright (C) 2020 Nuand, LLC.

4 | --

5 | -- This program is free software; you can redistribute it and/or modify

6 | -- it under the terms of the GNU General Public License as published by

7 | -- the Free Software Foundation; either version 2 of the License, or

8 | -- (at your option) any later version.

9 | --

10 | -- This program is distributed in the hope that it will be useful,

11 | -- but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | -- MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | -- GNU General Public License for more details.

14 | --

15 | -- You should have received a copy of the GNU General Public License along

16 | -- with this program; if not, write to the Free Software Foundation, Inc.,

17 | -- 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | library ieee ;

20 | use ieee.std_logic_1164.all ;

21 | use ieee.numeric_std.all ;

22 |

23 | library wlan ;

24 | use wlan.wlan_rx_p.all ;

25 |

26 | entity clock_sync_logic_vector is

27 | generic (

28 | LEN : integer := 8

29 | ) ;

30 | port (

31 | from_signal : in std_logic_vector(LEN-1 downto 0) ;

32 |

33 | to_clock : in std_logic ;

34 | to_reset : in std_logic ;

35 |

36 | to_signal : out std_logic_vector(LEN-1 downto 0)

37 | ) ;

38 | end entity;

39 |

40 | architecture arch of clock_sync_logic_vector is

41 |

42 | signal t_sig_r : std_logic_vector(LEN-1 downto 0) ;

43 |

44 | attribute ALTERA_ATTRIBUTE : string;

45 |

46 | attribute ALTERA_ATTRIBUTE of arch: architecture is "-name SDC_STATEMENT ""set_false_path -to [get_registers *clock_sync_logic_vector|*_r* ] "" ";

47 |

48 | begin

49 |

50 | process(all)

51 | begin

52 | if( to_reset = '1' ) then

53 | t_sig_r <= ( others => '0' ) ;

54 | to_signal <= ( others => '0' ) ;

55 | elsif( rising_edge( to_clock ) ) then

56 | t_sig_r <= from_signal ;

57 | to_signal <= t_sig_r ;

58 | end if ;

59 | end process ;

60 | end architecture ;

61 |

--------------------------------------------------------------------------------

/fpga/vhdl/clock_sync_params.vhd:

--------------------------------------------------------------------------------

1 | -- This file is part of bladeRF-wiphy.

2 | --

3 | -- Copyright (C) 2020 Nuand, LLC.

4 | --

5 | -- This program is free software; you can redistribute it and/or modify

6 | -- it under the terms of the GNU General Public License as published by

7 | -- the Free Software Foundation; either version 2 of the License, or

8 | -- (at your option) any later version.

9 | --

10 | -- This program is distributed in the hope that it will be useful,

11 | -- but WITHOUT ANY WARRANTY; without even the implied warranty of

12 | -- MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

13 | -- GNU General Public License for more details.

14 | --

15 | -- You should have received a copy of the GNU General Public License along

16 | -- with this program; if not, write to the Free Software Foundation, Inc.,

17 | -- 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301 USA.

18 |

19 | library ieee ;

20 | use ieee.std_logic_1164.all ;

21 | use ieee.numeric_std.all ;

22 |