├── 3D-model

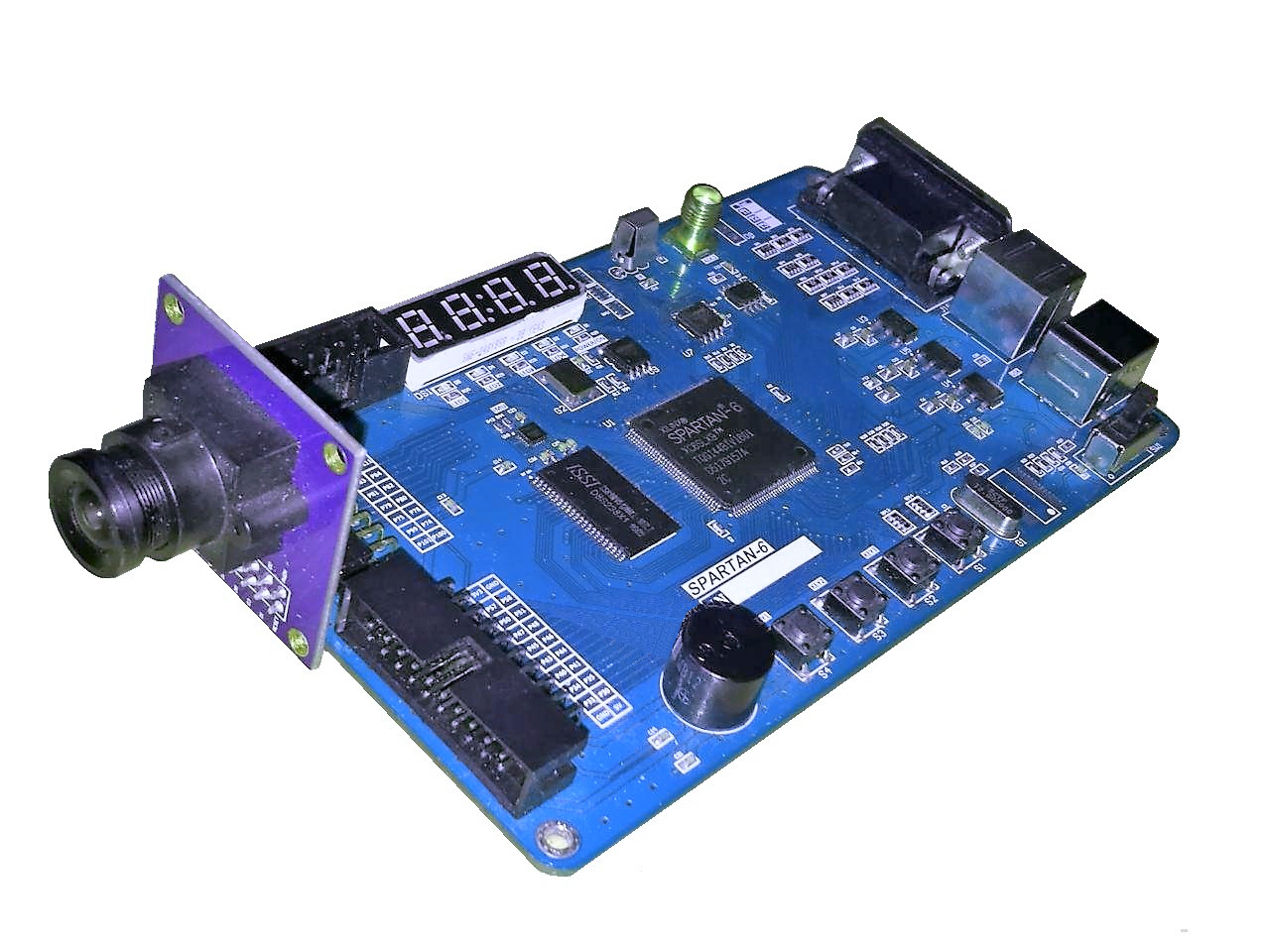

├── HDLab.step

└── View_3D.PNG

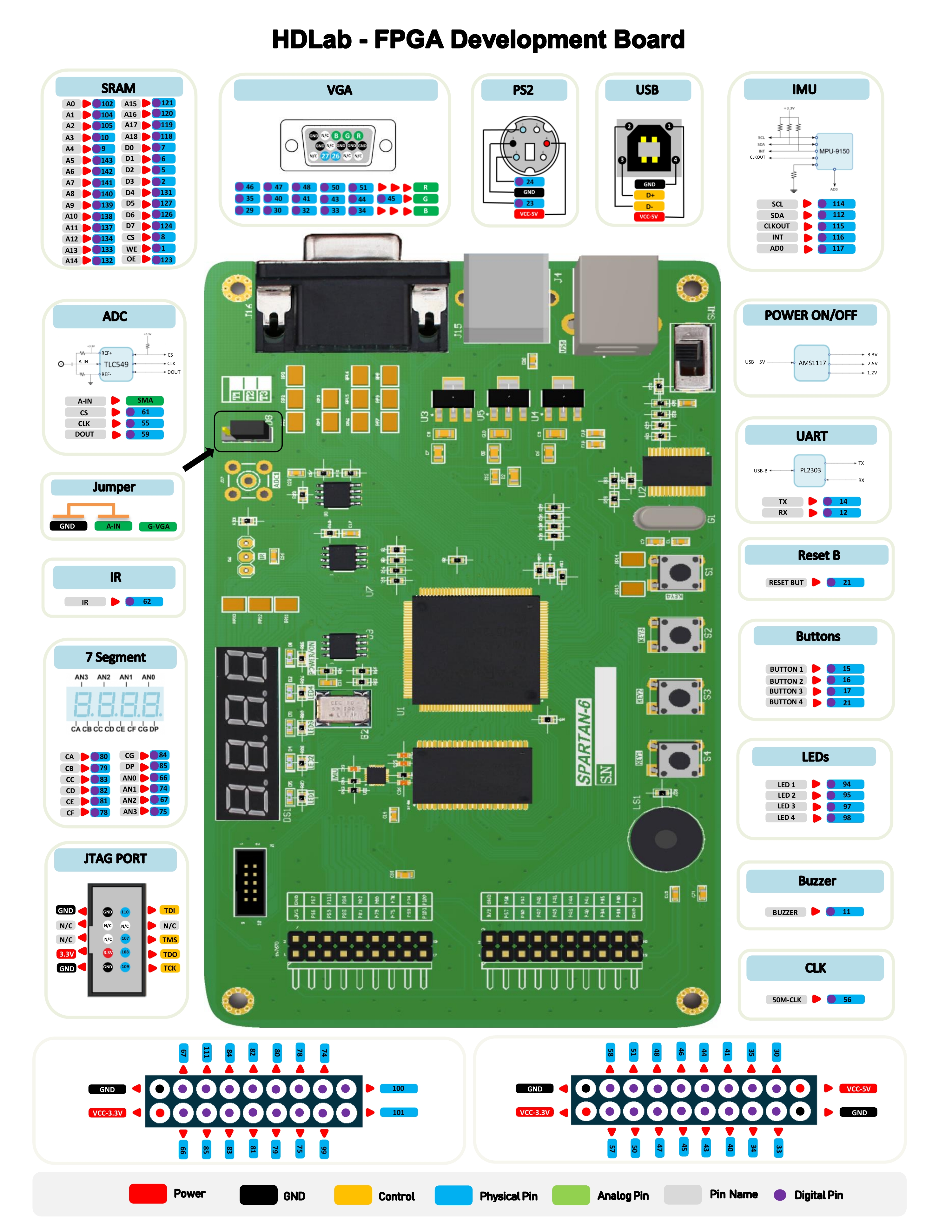

├── Block-diagram

├── Block-diagram-3000PX.jpg

├── Block-diagram.docx

├── Block-diagram.jpg

├── Block-diagram.pdf

└── PART

│ ├── 7SEG.PNG

│ ├── ADC.PNG

│ ├── BUTT.PNG

│ ├── BUZZ.PNG

│ ├── CLK.PNG

│ ├── IMU.PNG

│ ├── IO1.PNG

│ ├── IO2.PNG

│ ├── IR.PNG

│ ├── JTAG PORT.PNG

│ ├── JUMP.PNG

│ ├── LED.PNG

│ ├── POWER.PNG

│ ├── PS2.PNG

│ ├── RES.PNG

│ ├── SRAM.PNG

│ ├── UART.PNG

│ ├── USB.PNG

│ └── VGA.PNG

├── Document

├── BOM

│ └── Part Namber.xlsx

├── GERBER

│ ├── CAMtastic1.Cam

│ ├── CAMtastic2.Cam

│ ├── HDLab-NonPlated.TXT

│ ├── HDLab-Plated.TXT

│ ├── HDLab-macro.APR_LIB

│ ├── HDLab.DRR

│ ├── HDLab.EXTREP

│ ├── HDLab.GBL

│ ├── HDLab.GBO

│ ├── HDLab.GBP

│ ├── HDLab.GBS

│ ├── HDLab.GKO

│ ├── HDLab.GPB

│ ├── HDLab.GPT

│ ├── HDLab.GTL

│ ├── HDLab.GTO

│ ├── HDLab.GTP

│ ├── HDLab.GTS

│ ├── HDLab.LDP

│ ├── HDLab.REP

│ ├── HDLab.RUL

│ ├── HDLab.apr

│ └── Status Report.Txt

├── PCB

│ ├── PCB-src

│ │ └── HDLab.PcbDoc

│ └── PDF

│ │ └── HDLabPCB.pdf

├── PICTURES

│ ├── 7SEG.PNG

│ ├── ADC.PNG

│ ├── BUTT.PNG

│ ├── BUZZ.PNG

│ ├── Block-diagram.jpg

│ ├── CLK.PNG

│ ├── IMU.PNG

│ ├── IO1.PNG

│ ├── IO2.PNG

│ ├── IR.PNG

│ ├── JTAG PORT.PNG

│ ├── JUMP.PNG

│ ├── LED.PNG

│ ├── POWER.PNG

│ ├── PS2.PNG

│ ├── RES.PNG

│ ├── SRAM.PNG

│ ├── UART.PNG

│ ├── USB.PNG

│ ├── VGA.PNG

│ ├── View_3D.PNG

│ ├── View_F.jpg

│ ├── View_PCB.PNG

│ ├── View_T.jpg

│ └── View_TO.jpg

├── Schematic

│ ├── pdf

│ │ └── HDLab-schematics.pdf

│ └── schematics-src

│ │ └── HDLab.SchDoc

└── UCF

│ └── UCF-HDLab.txt

├── Example-Projects

└── VHDL_Module

│ ├── DFF

│ └── DFF.vhd

│ ├── HEX_TO_SSEG

│ └── HEX TO SSEG7.vhd

│ ├── I2C

│ ├── I2C_CLK.vhd

│ ├── I2C_MASTER.vhd

│ ├── I2C_MASTER_MODULE.vhd

│ ├── bof.vhd

│ └── timer.vhd

│ ├── TIMER

│ └── TIMER.vhd

│ └── UART

│ └── UART.vhd

├── LICENSE

├── PCB

├── HDLab-schematics.pdf

├── HDLab-v1.PcbDoc

├── HDLab-v1.PrjPCB

├── HDLab-v1.SchDoc

├── HDLabPCB.pdf

├── PCB

│ ├── PCB-src

│ │ └── HDLab.PcbDoc

│ └── PDF

│ │ └── HDLabPCB.pdf

└── Schematic

│ ├── pdf

│ └── HDLab-schematics.pdf

│ └── schematics-src

│ └── HDLab.SchDoc

└── README.md

/3D-model/View_3D.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/3D-model/View_3D.PNG

--------------------------------------------------------------------------------

/Block-diagram/Block-diagram-3000PX.jpg:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/Block-diagram-3000PX.jpg

--------------------------------------------------------------------------------

/Block-diagram/Block-diagram.docx:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/Block-diagram.docx

--------------------------------------------------------------------------------

/Block-diagram/Block-diagram.jpg:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/Block-diagram.jpg

--------------------------------------------------------------------------------

/Block-diagram/Block-diagram.pdf:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/Block-diagram.pdf

--------------------------------------------------------------------------------

/Block-diagram/PART/7SEG.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/7SEG.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/ADC.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/ADC.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/BUTT.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/BUTT.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/BUZZ.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/BUZZ.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/CLK.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/CLK.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/IMU.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/IMU.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/IO1.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/IO1.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/IO2.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/IO2.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/IR.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/IR.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/JTAG PORT.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/JTAG PORT.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/JUMP.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/JUMP.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/LED.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/LED.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/POWER.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/POWER.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/PS2.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/PS2.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/RES.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/RES.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/SRAM.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/SRAM.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/UART.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/UART.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/USB.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/USB.PNG

--------------------------------------------------------------------------------

/Block-diagram/PART/VGA.PNG:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Block-diagram/PART/VGA.PNG

--------------------------------------------------------------------------------

/Document/BOM/Part Namber.xlsx:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Document/BOM/Part Namber.xlsx

--------------------------------------------------------------------------------

/Document/GERBER/CAMtastic1.Cam:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Document/GERBER/CAMtastic1.Cam

--------------------------------------------------------------------------------

/Document/GERBER/CAMtastic2.Cam:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alialaei1/HDLab-FPGA-Development-Board/8222ca348099905bf8c129008aa4b7ec4e8b8d81/Document/GERBER/CAMtastic2.Cam

--------------------------------------------------------------------------------

/Document/GERBER/HDLab-NonPlated.TXT:

--------------------------------------------------------------------------------

1 | M48

2 | ;Layer_Color=9474304

3 | ;FILE_FORMAT=4:3

4 | METRIC,LZ

5 | ;TYPE=NON_PLATED

6 | T15F00S00C2.200

7 | %

8 | T15

9 | X0186397Y0103486

10 | X0187197Y0110236

11 | X0186397Y0116986

12 | M30

13 |

--------------------------------------------------------------------------------

/Document/GERBER/HDLab-Plated.TXT:

--------------------------------------------------------------------------------

1 | M48

2 | ;Layer_Color=9474304

3 | ;FILE_FORMAT=4:3

4 | METRIC,LZ

5 | ;TYPE=PLATED

6 | T1F00S00C0.300

7 | T2F00S00C0.635

8 | T3F00S00C0.700

9 | T4F00S00C0.900

10 | T5F00S00C1.000

11 | T6F00S00C1.016

12 | T7F00S00C1.100

13 | T8F00S00C1.190

14 | T9F00S00C1.270

15 | T10F00S00C1.500

16 | T11F00S00C2.300

17 | T12F00S00C2.500

18 | T13F00S00C3.150

19 | T14F00S00C3.180

20 | %

21 | T01

22 | X01868Y0079358

23 | X0188214Y0078772

24 | X0189628Y0079358

25 | X0073533Y0079248

26 | X0057421Y0079358

27 | X0056007Y0078772

28 | X0054593Y0079358

29 | X0054007Y0080772

30 | X0054593Y0082186

31 | X0056007Y0082772

32 | X0057421Y0082186

33 | X0058007Y0080772

34 | X0088138Y0113411

35 | X0088646Y0113919

36 | X0089154Y0114427

37 | X0089617Y011489

38 | X0096647Y0117602

39 | X009958Y011736

40 | Y0116725

41 | X0099072Y0116217

42 | X009958Y0117995

43 | X010541Y0116078

44 | X0106196Y0115824

45 | X0106819Y0115201

46 | X0108204Y0114173

47 | X0108712Y0110668

48 | X0112395Y0113411

49 | Y0114808

50 | X0115697

51 | X0117729Y0113411

52 | X0113919Y011811

53 | Y0118872

54 | X0114681Y0106299

55 | X011303

56 | X0117348Y0101727

57 | Y0100584

58 | X0118491Y0100711

59 | X0117983Y0099314

60 | X0118872Y0098425

61 | X0118999Y0097028

62 | X0118872Y0095949

63 | X011811Y0097536

64 | X0116967Y0085598

65 | X0107162Y010315

66 | X0124431Y0102685

67 | X0124587Y0107061

68 | X0125984Y0106934

69 | X0127381Y0107061

70 | X0129413Y0106553

71 | X012827Y0109474

72 | Y0110109

73 | X0125984Y0110236

74 | X0125603Y0109728

75 | X0123317

76 | X0122936Y0115189

77 | X0121539

78 | X0124206Y0115951

79 | X0122936Y0117348

80 | X0120904Y0118618

81 | X0126238Y0113665

82 | X0129159

83 | X0129413Y0115824

84 | X0134874Y0116459

85 | X0135001Y0114681

86 | X0134366Y0113919

87 | X0135636Y0112522

88 | X0137287Y0111887

89 | X013843Y0111252

90 | Y011303

91 | X0137414Y0114173

92 | X0137287Y0109855

93 | Y0108189

94 | X013843Y0108839

95 | Y0107315

96 | X0137795Y0105156

97 | X0137033Y0102108

98 | X0130937Y0102743

99 | X0131064Y0101189

100 | X012954Y0101473

101 | X0129794Y0099949

102 | X0128397Y0098933

103 | X0126492Y0091948

104 | X0125222Y0092075

105 | X012573Y0091186

106 | X0123063Y0092202

107 | X0122174Y0092964

108 | X0121412Y0093726

109 | X012065Y0094488

110 | X0119703Y0095181

111 | X0135255Y009271

112 | Y0091186

113 | Y0089652

114 | Y0088138

115 | X0137033Y008255

116 | X0148717Y0083693

117 | Y0086106

118 | Y0080772

119 | X0152889Y008168

120 | X0152702Y008428

121 | X015548Y0084201

122 | X0155575Y008255

123 | X0147574Y0091694

124 | X0140843Y0091948

125 | X0141224Y0092583

126 | X0140462Y0092613

127 | X014986Y0098298

128 | X0149225Y0100076

129 | X014859Y0100457

130 | X014856Y0099695

131 | X0153416Y0100076

132 | X0154051Y0099695

133 | X0154081Y0100457

134 | X0154178Y0103632

135 | X0154208Y0104394

136 | X0153543Y0104013

137 | X0151257Y0105791

138 | X0149352Y010541

139 | X0148971Y0105791

140 | X0148941Y0105029

141 | X0154239Y0113599

142 | X0153416Y011811

143 | X0153797Y0118745

144 | X0153035Y0118775

145 | X0158623Y0118745

146 | X0137795Y0118999

147 | X0135255Y0108077

148 | X0159131Y0109982

149 | X0159766Y0109601

150 | X0159796Y0110363

151 | X0159766Y0111887

152 | Y0112649

153 | X0162941

154 | Y0111887

155 | Y0104013

156 | Y0103251

157 | X0159766

158 | Y0104013

159 | Y0101854

160 | X0159736Y0101092

161 | X0160401Y0101473

162 | X0160147Y0099822

163 | X0160117Y009906

164 | X0160782Y0099441

165 | X0160274Y0095377

166 | X0164846Y009017

167 | Y0084201

168 | X0160528Y0082296

169 | Y0079629

170 | X0170942Y0086106

171 | X0169164Y0092329

172 | X01868Y0082186

173 | X0186214Y0080772

174 | X0190214

175 | X0189628Y0082186

176 | X0188214Y0082772

177 | X0159258Y0118364

178 | X0159288Y0119126

179 | X0159766Y012065

180 | Y0121539

181 | X0162814

182 | Y012065

183 | X01868Y0151494

184 | X0188214Y0150908

185 | X0189628Y0151494

186 | X0190214Y0152908

187 | X0189628Y0154322

188 | X0188214Y0154908

189 | X01868Y0154322

190 | X0186214Y0152908

191 | X0149225Y0141224

192 | X0147955

193 | X0148209Y0137922

194 | X0147828Y0137287

195 | X014859Y0137257

196 | X0139192Y0136398

197 | X0138811Y0135763

198 | X0139573Y0135733

199 | X0142113Y0132461

200 | X01397Y0129286

201 | X0137795Y0129413

202 | X0133985Y0131191

203 | X0133858Y0134112

204 | X0132538Y0132854

205 | X013133Y0133108

206 | X0130695Y0134378

207 | X0130429Y0135509

208 | X012954Y0136398

209 | X0128917Y0138061

210 | X0127889Y0137287

211 | X0126885Y0137934

212 | X0125857Y0138684

213 | X0125334Y0139939

214 | X0125857Y0141224

215 | X0126619Y0141194

216 | X0126238Y0141859

217 | X0122492Y0144589

218 | X0121793Y0151257

219 | X0133289Y0153247

220 | X0134366Y0137541

221 | X0133985Y0136906

222 | X0134747Y0136876

223 | X0132067Y012813

224 | X0133731Y0125095

225 | X0138049Y012319

226 | X0127254Y0123952

227 | X0122301

228 | X0120904

229 | X0122428Y0120269

230 | X0128397Y0119761

231 | X0128016Y0119126

232 | X0128778Y0119096

233 | X0121539Y0129413

234 | X0122682Y0135001

235 | X0117221Y0131826

236 | X0115189Y0132588

237 | X0115062Y0137922

238 | X0113284Y0140843

239 | X0112395

240 | X011176Y0140208

241 | X0113792Y0141478

242 | X0107569Y0141194

243 | X0106807Y0141224

244 | X0107315Y0141732

245 | Y0142367

246 | X010414Y014224

247 | X0102743

248 | X0102489Y0139573

249 | X01036Y0139541

250 | X010541Y0139446

251 | X0101092Y0139573

252 | X0097663Y014224

253 | X0096139

254 | X009017Y0143891

255 | Y0144653

256 | Y0145415

257 | Y0146177

258 | X0089916Y013843

259 | X0090055Y0136537

260 | X0089928Y0134886

261 | X0089916Y013335

262 | X0088404Y0134124

263 | X0088392Y0135763

264 | Y0137414

265 | X0088265Y0132334

266 | X0091313Y0130048

267 | X0094615Y0128651

268 | X0095135Y013387

269 | X0096786

270 | X0099949Y0132969

271 | X0100457Y0128651

272 | X0099072Y0124472

273 | X0108839Y0126492

274 | X0109601Y012573

275 | X0111125Y0125857

276 | X0112395Y0122809

277 | X0113919Y0119761

278 | X0117221Y0122809

279 | X0118364Y0123952

280 | X0108204Y0127508

281 | X0108077Y0128524

282 | X0107061Y0129032

283 | X010541Y0130048

284 | X0107315Y0132588

285 | X010795

286 | X0108585

287 | X010922

288 | X0107696Y0135509

289 | X0117729Y0152146

290 | X011557Y015494

291 | X009652Y0151511

292 | X0084709Y0130302

293 | X0084142Y0129735

294 | X0083578Y0129171

295 | X0087884Y0122555

296 | X0089123Y0121697

297 | X0090043Y0120904

298 | X0070739Y0144907

299 | X0065913Y0149733

300 | X0057421Y0151494

301 | X0058007Y0152908

302 | X0057421Y0154322

303 | X0056007Y0154908

304 | X0054593Y0154322

305 | X0054007Y0152908

306 | X0054593Y0151494

307 | X0056007Y0150908

308 | T02

309 | X0145542Y0082015

310 | Y0086895

311 | T03

312 | X0162033Y0079365

313 | X0174033

314 | X0142033

315 | X0130033

316 | X0118033

317 | X0106033

318 | X0094033

319 | X0090033

320 | X0086033

321 | X0082033

322 | X0070033

323 | X0066033

324 | X0062033

325 | Y0087365

326 | X0066033

327 | X0060033Y0091365

328 | X0056033

329 | X0054033Y0087365

330 | Y0095365

331 | X0056033Y0099365

332 | X0060033

333 | X0062033Y0095365

334 | Y0103365

335 | X0060033Y0107365

336 | X0056033

337 | X0054033Y0103365

338 | Y0111365

339 | X0056033Y0115365

340 | X0062033Y0111365

341 | X0070033

342 | X0074033

343 | X0078033

344 | X0080033Y0107365

345 | X0086033Y0111365

346 | X0094033

347 | X0098033

348 | X0100033Y0107365

349 | X0096033

350 | X0090033Y0103365

351 | Y0087365

352 | X0094033

353 | X0096033Y0083365

354 | X0092033

355 | X0088033

356 | X0084033

357 | X0106033Y0087365

358 | X0118033

359 | X0110033Y0103365

360 | X0134033Y0095365

361 | X0138033

362 | X0142033

363 | X0144033Y0083365

364 | X0156033Y0091365

365 | X0158033Y0095365

366 | X0150033Y0111365

367 | X0168033Y0115365

368 | X0172033

369 | X0176033

370 | X0180033

371 | X0184033

372 | X0188033

373 | Y0107365

374 | Y0099365

375 | X0186033Y0095365

376 | X0182033

377 | X0184033Y0091365

378 | X0188033

379 | X0186033Y0087365

380 | X0184033Y0083365

381 | X0180033

382 | X0172033

383 | X0164033

384 | Y0091365

385 | X0160033

386 | X0168033

387 | X0166033Y0095365

388 | X0168033Y0099365

389 | X0174033Y0103365

390 | Y0111365

391 | X0178033

392 | X0174033Y0119365

393 | X0176033Y0123365

394 | X0178033Y0127365

395 | X0182033

396 | X0188033Y0123365

397 | X0186033Y0119365

398 | X0188033Y0139365

399 | X0186033Y0143365

400 | X0182033

401 | Y0151365

402 | X0178033

403 | X0174033

404 | X0176033Y0147365

405 | X0172033

406 | X0168033

407 | X0164033

408 | X0160033

409 | Y0139365

410 | X0172033

411 | X0176033

412 | X0172033Y0131365

413 | X0168033

414 | X0166033Y0151365

415 | X0188033Y0147365

416 | X0158033Y0143365

417 | X0146033

418 | X0148033Y0147365

419 | X0144033

420 | X0150033Y0151365

421 | X0152033Y0131365

422 | X0142033Y0127365

423 | X0110033Y0143365

424 | X0096033Y0147365

425 | X0092033

426 | X0088033

427 | X0086033Y0151365

428 | X0082033Y0143365

429 | X0084033Y0131365

430 | X0082033Y0119365

431 | X0086033

432 | X0094033

433 | X0098033

434 | X0096033Y0123365

435 | X0078033Y0119365

436 | X0066033

437 | X0062033

438 | X0060033Y0123365

439 | X0056033

440 | X0054033Y0119365

441 | Y0127365

442 | X0056033Y0131365

443 | X0060033

444 | X0062033Y0127365

445 | Y0135365

446 | X0060033Y0139365

447 | X0056033

448 | X0054033Y0135365

449 | Y0143365

450 | X0056033Y0147365

451 | X0060033

452 | X0064033

453 | X0068033

454 | X0062033Y0151365

455 | X0078033Y0143365

456 | T04

457 | X0064516Y0090043

458 | Y0092583

459 | Y0095123

460 | Y0097663

461 | Y0100203

462 | Y0102743

463 | Y0105283

464 | Y0107823

465 | Y0110363

466 | Y0112903

467 | X0067056

468 | Y0110363

469 | Y0107823

470 | Y0105283

471 | Y0102743

472 | Y0100203

473 | Y0097663

474 | Y0095123

475 | Y0092583

476 | Y0090043

477 | X0180897Y0106836

478 | X0183397

479 | Y0108936

480 | Y0111536

481 | Y0113636

482 | X0180897

483 | X0112141Y014732

484 | X0109474

485 | X0106934

486 | X0104267

487 | X01016

488 | X0098933

489 | Y0155321

490 | X01016

491 | X0104267

492 | X0106934

493 | X0109474

494 | X0112141

495 | X0083058Y0152273

496 | X0080518

497 | Y0149733

498 | X0083058

499 | X0077978

500 | X0075438

501 | X0072898

502 | Y0152273

503 | X0075438

504 | X0077978

505 | X0067056Y0143764

506 | X0064516

507 | Y0141224

508 | X0067056

509 | Y0138684

510 | X0064516

511 | Y0136144

512 | X0067056

513 | Y0133604

514 | X0064516

515 | Y0131064

516 | X0067056

517 | Y0128524

518 | X0064516

519 | Y0125984

520 | X0067056

521 | Y0123444

522 | X0064516

523 | T05

524 | X0172387Y0080772

525 | X0175387

526 | X0178387

527 | X0178887Y0092349

528 | X0176887

529 | Y0094849

530 | X0178887

531 | T06

532 | X0082169Y0084963

533 | X0089789

534 | X013589Y0151638

535 | X013843

536 | X014097

537 | T07

538 | X0161036Y0148844

539 | Y0151384

540 | Y0153924

541 | T08

542 | X0179705Y013004

543 | Y013233

544 | Y013462

545 | Y013691

546 | Y01392

547 | X0182245Y014034

548 | Y013805

549 | Y013576

550 | Y013347

551 | Y013118

552 | X0184785Y013004

553 | Y013233

554 | Y013462

555 | Y013691

556 | Y01392

557 | T09

558 | X0098869Y0079947

559 | X0103314

560 | X0110299

561 | X0114744

562 | Y0086932

563 | X0110299

564 | X0103314

565 | X0098869

566 | X0121729Y0086804

567 | X0126174

568 | X013316

569 | X0137605

570 | Y007982

571 | X013316

572 | X0126174

573 | X0121729

574 | T10

575 | X0169787Y0080772

576 | X0180987

577 | X0155027Y0148757

578 | Y0153757

579 | X0150027

580 | Y0148757

581 | X0152527Y0151257

582 | T11

583 | X0181597Y0087579

584 | Y0099619

585 | T12

586 | X0188214Y0152908

587 | T13

588 | X0056007Y0080772

589 | X0188214

590 | X0056007Y0152908

591 | T14

592 | X0182245Y012162

593 | Y014762

594 | M30

595 |

--------------------------------------------------------------------------------

/Document/GERBER/HDLab-macro.APR_LIB:

--------------------------------------------------------------------------------

1 | G04:AMPARAMS|DCode=48|XSize=2.032mm|YSize=1.524mm|CornerRadius=0mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=Octagon|*

2 | %AMOCTAGOND48*

3 | 4,1,8,-0.381,-1.016,0.381,-1.016,0.762,-0.635,0.762,0.635,0.381,1.016,-0.381,1.016,-0.762,0.635,-0.762,-0.635,-0.381,-1.016,0.0*

4 | %

5 | G04:AMPARAMS|DCode=51|XSize=1.2mm|YSize=1.6mm|CornerRadius=0.3mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=RoundedRectangle|*

6 | %AMROUNDEDRECTD51*

7 | 21,1,1.200,1.000,0,0,270.0*

8 | 21,1,0.600,1.600,0,0,270.0*

9 | 1,1,0.600,-0.500,-0.300*

10 | 1,1,0.600,-0.500,0.300*

11 | 1,1,0.600,0.500,0.300*

12 | 1,1,0.600,0.500,-0.300*

13 | %

14 | G04:AMPARAMS|DCode=113|XSize=2.235mm|YSize=1.727mm|CornerRadius=0mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=Octagon|*

15 | %AMOCTAGOND113*

16 | 4,1,8,-0.432,-1.118,0.432,-1.118,0.864,-0.686,0.864,0.686,0.432,1.118,-0.432,1.118,-0.864,0.686,-0.864,-0.686,-0.432,-1.118,0.0*

17 | %

18 | G04:AMPARAMS|DCode=116|XSize=1.403mm|YSize=1.803mm|CornerRadius=0.402mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=RoundedRectangle|*

19 | %AMROUNDEDRECTD116*

20 | 21,1,1.403,1.000,0,0,270.0*

21 | 21,1,0.600,1.803,0,0,270.0*

22 | 1,1,0.803,-0.500,-0.300*

23 | 1,1,0.803,-0.500,0.300*

24 | 1,1,0.803,0.500,0.300*

25 | 1,1,0.803,0.500,-0.300*

26 | %

27 |

--------------------------------------------------------------------------------

/Document/GERBER/HDLab.DRR:

--------------------------------------------------------------------------------

1 | ---------------------------------------------------------------------------

2 | NCDrill File Report For: HDLab.PcbDoc 8/9/2018 11:45:04 PM

3 | ---------------------------------------------------------------------------

4 |

5 | Layer Pair : Top Layer to Bottom Layer

6 | ASCII Plated RoundHoles File : HDLab-Plated.TXT

7 | ASCII Non-Plated RoundHoles File : HDLab-NonPlated.TXT

8 |

9 | Tool Hole Size Hole Type Hole Count Plated Tool Travel

10 | ---------------------------------------------------------------------------

11 | T1 0.3mm (11.811mil) Round 286 1297.13 mm (51.07 Inch)

12 | T2 0.635mm (25mil) Round 2 4.88 mm (0.19 Inch)

13 | T3 0.7mm (27.559mil) Round 144 1110.31 mm (43.71 Inch)

14 | T4 0.9mm (35.433mil) Round 66 397.78 mm (15.66 Inch)

15 | T5 1mm (39.37mil) Round 7 24.09 mm (0.95 Inch)

16 | T6 1.016mm (40mil) Round 5 93.76 mm (3.69 Inch)

17 | T7 1.1mm (43.307mil) Round 3 5.08 mm (0.20 Inch)

18 | T8 1.19mm (46.85mil) Round 15 33.05 mm (1.30 Inch)

19 | T9 1.27mm (50mil) Round 16 100.33 mm (3.95 Inch)

20 | T10 1.5mm (59.055mil) Round 7 102.51 mm (4.04 Inch)

21 | T11 2.3mm (90.551mil) Round 2 12.04 mm (0.47 Inch)

22 | T12 2.5mm (98.425mil) Round 1 0.00 mm (0.00 Inch)

23 | T13 3.15mm (124.016mil) Round 3 282.81 mm (11.13 Inch)

24 | T14 3.18mm (125.197mil) Round 2 26.00 mm (1.02 Inch)

25 | T15 2.2mm (86.614mil) Round 3 NPTH 13.59 mm (0.54 Inch)

26 | ---------------------------------------------------------------------------

27 | Totals 562 3503.37 mm (137.93 Inch)

28 |

29 | Total Processing Time (hh:mm:ss) : 00:00:00

30 |

--------------------------------------------------------------------------------

/Document/GERBER/HDLab.EXTREP:

--------------------------------------------------------------------------------

1 | ------------------------------------------------------------------------------------------

2 | Gerber File Extension Report For: HDLab.GBR 8/9/2018 11:39:10 PM

3 | ------------------------------------------------------------------------------------------

4 |

5 |

6 | ------------------------------------------------------------------------------------------

7 | Layer Extension Layer Description

8 | ------------------------------------------------------------------------------------------

9 | .GTL Top Layer

10 | .GBL Bottom Layer

11 | .GPB Bottom Pad Master

12 | .GPT Top Pad Master

13 | .GTO Top Overlay

14 | .GTP Top Paste

15 | .GTS Top Solder

16 | .GBS Bottom Solder

17 | .GBP Bottom Paste

18 | .GBO Bottom Overlay

19 | .GKO Keep-Out Layer

20 | ------------------------------------------------------------------------------------------

21 |

--------------------------------------------------------------------------------

/Document/GERBER/HDLab.GBO:

--------------------------------------------------------------------------------

1 | %FSLAX43Y43*%

2 | %MOMM*%

3 | G71*

4 | G01*

5 | G75*

6 | G04 Layer_Color=32896*

7 | %ADD10R,0.650X0.600*%

8 | %ADD11R,0.500X0.600*%

9 | %ADD12R,0.800X0.800*%

10 | %ADD13R,0.900X1.300*%

11 | %ADD14R,1.300X0.900*%

12 | %ADD15R,0.800X0.800*%

13 | %ADD16R,0.850X0.600*%

14 | %ADD17R,0.600X0.850*%

15 | %ADD18R,0.600X0.650*%

16 | %ADD19R,0.600X0.500*%

17 | %ADD20O,1.800X0.300*%

18 | %ADD21O,0.300X1.800*%

19 | %ADD22O,2.100X0.450*%

20 | %ADD23R,2.400X3.300*%

21 | %ADD24R,2.400X1.000*%

22 | %ADD25O,0.510X2.000*%

23 | %ADD26R,0.510X2.000*%

24 | %ADD27R,2.400X2.500*%

25 | %ADD28R,2.500X2.500*%

26 | %ADD29O,1.650X0.550*%

27 | %ADD30O,0.700X0.200*%

28 | %ADD31O,0.200X0.700*%

29 | %ADD32C,0.254*%

30 | %ADD33C,0.200*%

31 | %ADD34C,1.000*%

32 | %ADD35C,0.250*%

33 | %ADD36C,1.500*%

34 | %ADD37C,0.500*%

35 | %ADD38C,0.245*%

36 | %ADD39O,1.800X1.524*%

37 | %ADD40O,1.800X1.500*%

38 | %ADD41O,5.000X4.000*%

39 | %ADD42C,3.000*%

40 | %ADD43P,1.524X8X112.5*%

41 | %ADD44C,0.600*%

42 | %ADD45C,5.000*%

43 | %ADD46C,1.700*%

44 | %ADD47O,1.700X3.556*%

45 | G04:AMPARAMS|DCode=48|XSize=2.032mm|YSize=1.524mm|CornerRadius=0mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=Octagon|*

46 | %AMOCTAGOND48*

47 | 4,1,8,-0.381,-1.016,0.381,-1.016,0.762,-0.635,0.762,0.635,0.381,1.016,-0.381,1.016,-0.762,0.635,-0.762,-0.635,-0.381,-1.016,0.0*

48 | %

49 | %ADD48OCTAGOND48*%

50 |

51 | %ADD49O,2.400X1.800*%

52 | %ADD50R,2.400X1.800*%

53 | G04:AMPARAMS|DCode=51|XSize=1.2mm|YSize=1.6mm|CornerRadius=0.3mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=RoundedRectangle|*

54 | %AMROUNDEDRECTD51*

55 | 21,1,1.200,1.000,0,0,270.0*

56 | 21,1,0.600,1.600,0,0,270.0*

57 | 1,1,0.600,-0.500,-0.300*

58 | 1,1,0.600,-0.500,0.300*

59 | 1,1,0.600,0.500,0.300*

60 | 1,1,0.600,0.500,-0.300*

61 | %

62 | %ADD51ROUNDEDRECTD51*%

63 | %ADD52R,1.600X1.200*%

64 | %ADD53C,1.397*%

65 | %ADD54C,3.800*%

66 | %ADD55O,1.600X1.900*%

67 | %ADD56R,1.600X1.900*%

68 | %ADD57C,2.032*%

69 | %ADD58R,2.032X2.032*%

70 | %ADD59C,1.500*%

71 | %ADD60R,1.500X1.500*%

72 | %ADD61R,1.500X1.500*%

73 | %ADD62C,2.500*%

74 | %ADD63P,2.337X8X202.5*%

75 | %ADD64C,0.700*%

76 | %ADD65C,1.000*%

77 | %ADD66C,0.255*%

78 | %ADD67C,0.800*%

79 | %ADD68C,0.178*%

80 | %ADD69C,0.860*%

81 | %ADD70C,0.127*%

82 | %ADD71C,0.600*%

83 | %ADD72C,0.152*%

84 | %ADD73C,0.203*%

85 | %ADD74C,0.762*%

86 | %ADD75C,0.051*%

87 | %ADD76C,0.120*%

88 | %ADD77C,0.150*%

89 | %ADD78R,17.755X3.175*%

90 | %ADD79R,2.159X1.905*%

91 | %ADD80R,0.508X0.508*%

92 | %ADD81R,1.778X0.254*%

93 | %ADD82R,0.701X0.651*%

94 | %ADD83R,0.551X0.651*%

95 | %ADD84R,1.003X1.003*%

96 | %ADD85R,1.103X1.503*%

97 | %ADD86R,1.503X1.103*%

98 | %ADD87R,1.003X1.003*%

99 | %ADD88R,1.053X0.803*%

100 | %ADD89R,0.803X1.053*%

101 | %ADD90R,0.651X0.701*%

102 | %ADD91R,0.651X0.551*%

103 | %ADD92O,2.003X0.503*%

104 | %ADD93O,0.503X2.003*%

105 | %ADD94O,2.303X0.653*%

106 | %ADD95R,2.603X3.503*%

107 | %ADD96R,2.603X1.203*%

108 | %ADD97O,0.713X2.203*%

109 | %ADD98R,0.713X2.203*%

110 | %ADD99R,2.603X2.703*%

111 | %ADD100R,2.703X2.703*%

112 | %ADD101O,1.853X0.753*%

113 | %ADD102O,0.903X0.403*%

114 | %ADD103O,0.403X0.903*%

115 | %ADD104O,2.003X1.727*%

116 | %ADD105O,2.003X1.703*%

117 | %ADD106O,5.203X4.203*%

118 | %ADD107C,3.203*%

119 | %ADD108P,1.744X8X112.5*%

120 | %ADD109C,0.803*%

121 | %ADD110C,5.200*%

122 | %ADD111C,1.903*%

123 | %ADD112O,1.903X3.759*%

124 | G04:AMPARAMS|DCode=113|XSize=2.235mm|YSize=1.727mm|CornerRadius=0mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=Octagon|*

125 | %AMOCTAGOND113*

126 | 4,1,8,-0.432,-1.118,0.432,-1.118,0.864,-0.686,0.864,0.686,0.432,1.118,-0.432,1.118,-0.864,0.686,-0.864,-0.686,-0.432,-1.118,0.0*

127 | %

128 | %ADD113OCTAGOND113*%

129 |

130 | %ADD114O,2.603X2.003*%

131 | %ADD115R,2.603X2.003*%

132 | G04:AMPARAMS|DCode=116|XSize=1.403mm|YSize=1.803mm|CornerRadius=0.402mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=RoundedRectangle|*

133 | %AMROUNDEDRECTD116*

134 | 21,1,1.403,1.000,0,0,270.0*

135 | 21,1,0.600,1.803,0,0,270.0*

136 | 1,1,0.803,-0.500,-0.300*

137 | 1,1,0.803,-0.500,0.300*

138 | 1,1,0.803,0.500,0.300*

139 | 1,1,0.803,0.500,-0.300*

140 | %

141 | %ADD116ROUNDEDRECTD116*%

142 | %ADD117R,1.803X1.403*%

143 | %ADD118C,1.600*%

144 | %ADD119C,4.003*%

145 | %ADD120O,1.803X2.103*%

146 | %ADD121R,1.803X2.103*%

147 | %ADD122C,2.235*%

148 | %ADD123R,2.235X2.235*%

149 | %ADD124C,1.703*%

150 | %ADD125R,1.703X1.703*%

151 | %ADD126R,1.703X1.703*%

152 | %ADD127C,2.703*%

153 | %ADD128P,2.557X8X202.5*%

154 | %ADD129C,0.100*%

155 | D33*

156 | X96972Y115330D02*

157 | Y115530D01*

158 | X96322Y115330D02*

159 | Y115530D01*

160 | X70302Y143270D02*

161 | Y143470D01*

162 | X69652Y143270D02*

163 | Y143470D01*

164 | X71953Y143270D02*

165 | Y143470D01*

166 | X71303Y143270D02*

167 | Y143470D01*

168 | D76*

169 | X70358Y145288D02*

170 | Y145738D01*

171 | X70133D01*

172 | X70058Y145663D01*

173 | Y145513D01*

174 | X70133Y145438D01*

175 | X70358D01*

176 | X70208D02*

177 | X70058Y145288D01*

178 | X69683D02*

179 | Y145738D01*

180 | X69908Y145513D01*

181 | X69608D01*

182 | X69158Y145738D02*

183 | X69458D01*

184 | Y145513D01*

185 | X69308Y145588D01*

186 | X69233D01*

187 | X69158Y145513D01*

188 | Y145363D01*

189 | X69233Y145288D01*

190 | X69383D01*

191 | X69458Y145363D01*

192 | X72263Y141478D02*

193 | Y141928D01*

194 | X72038D01*

195 | X71963Y141853D01*

196 | Y141703D01*

197 | X72038Y141628D01*

198 | X72263D01*

199 | X72113D02*

200 | X71963Y141478D01*

201 | X71588D02*

202 | Y141928D01*

203 | X71813Y141703D01*

204 | X71513D01*

205 | X71063Y141928D02*

206 | X71213Y141853D01*

207 | X71363Y141703D01*

208 | Y141553D01*

209 | X71288Y141478D01*

210 | X71138D01*

211 | X71063Y141553D01*

212 | Y141628D01*

213 | X71138Y141703D01*

214 | X71363D01*

215 | D129*

216 | X97008Y116755D02*

217 | Y116955D01*

218 | X96908D01*

219 | X96875Y116921D01*

220 | Y116855D01*

221 | X96908Y116821D01*

222 | X97008D01*

223 | X96941D02*

224 | X96875Y116755D01*

225 | X96708D02*

226 | Y116955D01*

227 | X96808Y116855D01*

228 | X96675D01*

229 | X96475Y116755D02*

230 | X96608D01*

231 | X96475Y116888D01*

232 | Y116921D01*

233 | X96508Y116955D01*

234 | X96575D01*

235 | X96608Y116921D01*

236 | M02*

237 |

--------------------------------------------------------------------------------

/Document/GERBER/HDLab.GBP:

--------------------------------------------------------------------------------

1 | %FSLAX43Y43*%

2 | %MOMM*%

3 | G71*

4 | G01*

5 | G75*

6 | G04 Layer_Color=128*

7 | %ADD10R,0.650X0.600*%

8 | %ADD11R,0.500X0.600*%

9 | %ADD12R,0.800X0.800*%

10 | %ADD13R,0.900X1.300*%

11 | %ADD14R,1.300X0.900*%

12 | %ADD15R,0.800X0.800*%

13 | %ADD16R,0.850X0.600*%

14 | %ADD17R,0.600X0.850*%

15 | %ADD18R,0.600X0.650*%

16 | %ADD19R,0.600X0.500*%

17 | %ADD20O,1.800X0.300*%

18 | %ADD21O,0.300X1.800*%

19 | %ADD22O,2.100X0.450*%

20 | %ADD23R,2.400X3.300*%

21 | %ADD24R,2.400X1.000*%

22 | %ADD25O,0.510X2.000*%

23 | %ADD26R,0.510X2.000*%

24 | %ADD27R,2.400X2.500*%

25 | %ADD28R,2.500X2.500*%

26 | %ADD29O,1.650X0.550*%

27 | %ADD30O,0.700X0.200*%

28 | %ADD31O,0.200X0.700*%

29 | %ADD32C,0.254*%

30 | %ADD33C,0.200*%

31 | %ADD34C,1.000*%

32 | %ADD35C,0.250*%

33 | %ADD36C,1.500*%

34 | %ADD37C,0.500*%

35 | %ADD38C,0.245*%

36 | %ADD39O,1.800X1.524*%

37 | %ADD40O,1.800X1.500*%

38 | %ADD41O,5.000X4.000*%

39 | %ADD42C,3.000*%

40 | %ADD43P,1.524X8X112.5*%

41 | %ADD44C,0.600*%

42 | %ADD45C,5.000*%

43 | %ADD46C,1.700*%

44 | %ADD47O,1.700X3.556*%

45 | G04:AMPARAMS|DCode=48|XSize=2.032mm|YSize=1.524mm|CornerRadius=0mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=Octagon|*

46 | %AMOCTAGOND48*

47 | 4,1,8,-0.381,-1.016,0.381,-1.016,0.762,-0.635,0.762,0.635,0.381,1.016,-0.381,1.016,-0.762,0.635,-0.762,-0.635,-0.381,-1.016,0.0*

48 | %

49 | %ADD48OCTAGOND48*%

50 |

51 | %ADD49O,2.400X1.800*%

52 | %ADD50R,2.400X1.800*%

53 | G04:AMPARAMS|DCode=51|XSize=1.2mm|YSize=1.6mm|CornerRadius=0.3mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=RoundedRectangle|*

54 | %AMROUNDEDRECTD51*

55 | 21,1,1.200,1.000,0,0,270.0*

56 | 21,1,0.600,1.600,0,0,270.0*

57 | 1,1,0.600,-0.500,-0.300*

58 | 1,1,0.600,-0.500,0.300*

59 | 1,1,0.600,0.500,0.300*

60 | 1,1,0.600,0.500,-0.300*

61 | %

62 | %ADD51ROUNDEDRECTD51*%

63 | %ADD52R,1.600X1.200*%

64 | %ADD53C,1.397*%

65 | %ADD54C,3.800*%

66 | %ADD55O,1.600X1.900*%

67 | %ADD56R,1.600X1.900*%

68 | %ADD57C,2.032*%

69 | %ADD58R,2.032X2.032*%

70 | %ADD59C,1.500*%

71 | %ADD60R,1.500X1.500*%

72 | %ADD61R,1.500X1.500*%

73 | %ADD62C,2.500*%

74 | %ADD63P,2.337X8X202.5*%

75 | %ADD64C,0.700*%

76 | %ADD65C,1.000*%

77 | %ADD66C,0.255*%

78 | %ADD67C,0.800*%

79 | %ADD68C,0.178*%

80 | %ADD69C,0.860*%

81 | %ADD70C,0.127*%

82 | %ADD71C,0.600*%

83 | %ADD72C,0.152*%

84 | %ADD73C,0.203*%

85 | %ADD74C,0.762*%

86 | %ADD75C,0.051*%

87 | %ADD76C,0.120*%

88 | %ADD77C,0.150*%

89 | %ADD78R,17.755X3.175*%

90 | %ADD79R,2.159X1.905*%

91 | %ADD80R,0.508X0.508*%

92 | %ADD81R,1.778X0.254*%

93 | %ADD82R,0.701X0.651*%

94 | %ADD83R,0.551X0.651*%

95 | %ADD84R,1.003X1.003*%

96 | %ADD85R,1.103X1.503*%

97 | %ADD86R,1.503X1.103*%

98 | %ADD87R,1.003X1.003*%

99 | %ADD88R,1.053X0.803*%

100 | %ADD89R,0.803X1.053*%

101 | %ADD90R,0.651X0.701*%

102 | %ADD91R,0.651X0.551*%

103 | %ADD92O,2.003X0.503*%

104 | %ADD93O,0.503X2.003*%

105 | %ADD94O,2.303X0.653*%

106 | %ADD95R,2.603X3.503*%

107 | %ADD96R,2.603X1.203*%

108 | %ADD97O,0.713X2.203*%

109 | %ADD98R,0.713X2.203*%

110 | %ADD99R,2.603X2.703*%

111 | %ADD100R,2.703X2.703*%

112 | %ADD101O,1.853X0.753*%

113 | %ADD102O,0.903X0.403*%

114 | %ADD103O,0.403X0.903*%

115 | %ADD104O,2.003X1.727*%

116 | %ADD105O,2.003X1.703*%

117 | %ADD106O,5.203X4.203*%

118 | %ADD107C,3.203*%

119 | %ADD108P,1.744X8X112.5*%

120 | %ADD109C,0.803*%

121 | %ADD110C,5.200*%

122 | %ADD111C,1.903*%

123 | %ADD112O,1.903X3.759*%

124 | G04:AMPARAMS|DCode=113|XSize=2.235mm|YSize=1.727mm|CornerRadius=0mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=Octagon|*

125 | %AMOCTAGOND113*

126 | 4,1,8,-0.432,-1.118,0.432,-1.118,0.864,-0.686,0.864,0.686,0.432,1.118,-0.432,1.118,-0.864,0.686,-0.864,-0.686,-0.432,-1.118,0.0*

127 | %

128 | %ADD113OCTAGOND113*%

129 |

130 | %ADD114O,2.603X2.003*%

131 | %ADD115R,2.603X2.003*%

132 | G04:AMPARAMS|DCode=116|XSize=1.403mm|YSize=1.803mm|CornerRadius=0.402mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=RoundedRectangle|*

133 | %AMROUNDEDRECTD116*

134 | 21,1,1.403,1.000,0,0,270.0*

135 | 21,1,0.600,1.803,0,0,270.0*

136 | 1,1,0.803,-0.500,-0.300*

137 | 1,1,0.803,-0.500,0.300*

138 | 1,1,0.803,0.500,0.300*

139 | 1,1,0.803,0.500,-0.300*

140 | %

141 | %ADD116ROUNDEDRECTD116*%

142 | %ADD117R,1.803X1.403*%

143 | %ADD118C,1.600*%

144 | %ADD119C,4.003*%

145 | %ADD120O,1.803X2.103*%

146 | %ADD121R,1.803X2.103*%

147 | %ADD122C,2.235*%

148 | %ADD123R,2.235X2.235*%

149 | %ADD124C,1.703*%

150 | %ADD125R,1.703X1.703*%

151 | %ADD126R,1.703X1.703*%

152 | %ADD127C,2.703*%

153 | %ADD128P,2.557X8X202.5*%

154 | D16*

155 | X96647Y114808D02*

156 | D03*

157 | Y116052D02*

158 | D03*

159 | X69977Y142748D02*

160 | D03*

161 | Y143992D02*

162 | D03*

163 | X71628Y142748D02*

164 | D03*

165 | Y143992D02*

166 | D03*

167 | M02*

168 |

--------------------------------------------------------------------------------

/Document/GERBER/HDLab.GBS:

--------------------------------------------------------------------------------

1 | %FSLAX43Y43*%

2 | %MOMM*%

3 | G71*

4 | G01*

5 | G75*

6 | G04 Layer_Color=16711935*

7 | %ADD10R,0.650X0.600*%

8 | %ADD11R,0.500X0.600*%

9 | %ADD12R,0.800X0.800*%

10 | %ADD13R,0.900X1.300*%

11 | %ADD14R,1.300X0.900*%

12 | %ADD15R,0.800X0.800*%

13 | %ADD16R,0.850X0.600*%

14 | %ADD17R,0.600X0.850*%

15 | %ADD18R,0.600X0.650*%

16 | %ADD19R,0.600X0.500*%

17 | %ADD20O,1.800X0.300*%

18 | %ADD21O,0.300X1.800*%

19 | %ADD22O,2.100X0.450*%

20 | %ADD23R,2.400X3.300*%

21 | %ADD24R,2.400X1.000*%

22 | %ADD25O,0.510X2.000*%

23 | %ADD26R,0.510X2.000*%

24 | %ADD27R,2.400X2.500*%

25 | %ADD28R,2.500X2.500*%

26 | %ADD29O,1.650X0.550*%

27 | %ADD30O,0.700X0.200*%

28 | %ADD31O,0.200X0.700*%

29 | %ADD32C,0.254*%

30 | %ADD33C,0.200*%

31 | %ADD34C,1.000*%

32 | %ADD35C,0.250*%

33 | %ADD36C,1.500*%

34 | %ADD37C,0.500*%

35 | %ADD38C,0.245*%

36 | %ADD39O,1.800X1.524*%

37 | %ADD40O,1.800X1.500*%

38 | %ADD41O,5.000X4.000*%

39 | %ADD42C,3.000*%

40 | %ADD43P,1.524X8X112.5*%

41 | %ADD44C,0.600*%

42 | %ADD45C,5.000*%

43 | %ADD46C,1.700*%

44 | %ADD47O,1.700X3.556*%

45 | G04:AMPARAMS|DCode=48|XSize=2.032mm|YSize=1.524mm|CornerRadius=0mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=Octagon|*

46 | %AMOCTAGOND48*

47 | 4,1,8,-0.381,-1.016,0.381,-1.016,0.762,-0.635,0.762,0.635,0.381,1.016,-0.381,1.016,-0.762,0.635,-0.762,-0.635,-0.381,-1.016,0.0*

48 | %

49 | %ADD48OCTAGOND48*%

50 |

51 | %ADD49O,2.400X1.800*%

52 | %ADD50R,2.400X1.800*%

53 | G04:AMPARAMS|DCode=51|XSize=1.2mm|YSize=1.6mm|CornerRadius=0.3mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=RoundedRectangle|*

54 | %AMROUNDEDRECTD51*

55 | 21,1,1.200,1.000,0,0,270.0*

56 | 21,1,0.600,1.600,0,0,270.0*

57 | 1,1,0.600,-0.500,-0.300*

58 | 1,1,0.600,-0.500,0.300*

59 | 1,1,0.600,0.500,0.300*

60 | 1,1,0.600,0.500,-0.300*

61 | %

62 | %ADD51ROUNDEDRECTD51*%

63 | %ADD52R,1.600X1.200*%

64 | %ADD53C,1.397*%

65 | %ADD54C,3.800*%

66 | %ADD55O,1.600X1.900*%

67 | %ADD56R,1.600X1.900*%

68 | %ADD57C,2.032*%

69 | %ADD58R,2.032X2.032*%

70 | %ADD59C,1.500*%

71 | %ADD60R,1.500X1.500*%

72 | %ADD61R,1.500X1.500*%

73 | %ADD62C,2.500*%

74 | %ADD63P,2.337X8X202.5*%

75 | %ADD64C,0.700*%

76 | %ADD65C,1.000*%

77 | %ADD66C,0.255*%

78 | %ADD67C,0.800*%

79 | %ADD68C,0.178*%

80 | %ADD69C,0.860*%

81 | %ADD70C,0.127*%

82 | %ADD71C,0.600*%

83 | %ADD72C,0.152*%

84 | %ADD73C,0.203*%

85 | %ADD74C,0.762*%

86 | %ADD75C,0.051*%

87 | %ADD76C,0.120*%

88 | %ADD77C,0.150*%

89 | %ADD78R,17.755X3.175*%

90 | %ADD79R,2.159X1.905*%

91 | %ADD80R,0.508X0.508*%

92 | %ADD81R,1.778X0.254*%

93 | %ADD82R,0.701X0.651*%

94 | %ADD83R,0.551X0.651*%

95 | %ADD84R,1.003X1.003*%

96 | %ADD85R,1.103X1.503*%

97 | %ADD86R,1.503X1.103*%

98 | %ADD87R,1.003X1.003*%

99 | %ADD88R,1.053X0.803*%

100 | %ADD89R,0.803X1.053*%

101 | %ADD90R,0.651X0.701*%

102 | %ADD91R,0.651X0.551*%

103 | %ADD92O,2.003X0.503*%

104 | %ADD93O,0.503X2.003*%

105 | %ADD94O,2.303X0.653*%

106 | %ADD95R,2.603X3.503*%

107 | %ADD96R,2.603X1.203*%

108 | %ADD97O,0.713X2.203*%

109 | %ADD98R,0.713X2.203*%

110 | %ADD99R,2.603X2.703*%

111 | %ADD100R,2.703X2.703*%

112 | %ADD101O,1.853X0.753*%

113 | %ADD102O,0.903X0.403*%

114 | %ADD103O,0.403X0.903*%

115 | %ADD104O,2.003X1.727*%

116 | %ADD105O,2.003X1.703*%

117 | %ADD106O,5.203X4.203*%

118 | %ADD107C,3.203*%

119 | %ADD108P,1.744X8X112.5*%

120 | %ADD109C,0.803*%

121 | %ADD110C,5.200*%

122 | %ADD111C,1.903*%

123 | %ADD112O,1.903X3.759*%

124 | G04:AMPARAMS|DCode=113|XSize=2.235mm|YSize=1.727mm|CornerRadius=0mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=Octagon|*

125 | %AMOCTAGOND113*

126 | 4,1,8,-0.432,-1.118,0.432,-1.118,0.864,-0.686,0.864,0.686,0.432,1.118,-0.432,1.118,-0.864,0.686,-0.864,-0.686,-0.432,-1.118,0.0*

127 | %

128 | %ADD113OCTAGOND113*%

129 |

130 | %ADD114O,2.603X2.003*%

131 | %ADD115R,2.603X2.003*%

132 | G04:AMPARAMS|DCode=116|XSize=1.403mm|YSize=1.803mm|CornerRadius=0.402mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=RoundedRectangle|*

133 | %AMROUNDEDRECTD116*

134 | 21,1,1.403,1.000,0,0,270.0*

135 | 21,1,0.600,1.803,0,0,270.0*

136 | 1,1,0.803,-0.500,-0.300*

137 | 1,1,0.803,-0.500,0.300*

138 | 1,1,0.803,0.500,0.300*

139 | 1,1,0.803,0.500,-0.300*

140 | %

141 | %ADD116ROUNDEDRECTD116*%

142 | %ADD117R,1.803X1.403*%

143 | %ADD118C,1.600*%

144 | %ADD119C,4.003*%

145 | %ADD120O,1.803X2.103*%

146 | %ADD121R,1.803X2.103*%

147 | %ADD122C,2.235*%

148 | %ADD123R,2.235X2.235*%

149 | %ADD124C,1.703*%

150 | %ADD125R,1.703X1.703*%

151 | %ADD126R,1.703X1.703*%

152 | %ADD127C,2.703*%

153 | %ADD128P,2.557X8X202.5*%

154 | D88*

155 | X96647Y114808D02*

156 | D03*

157 | Y116052D02*

158 | D03*

159 | X69977Y142748D02*

160 | D03*

161 | Y143992D02*

162 | D03*

163 | X71628Y142748D02*

164 | D03*

165 | Y143992D02*

166 | D03*

167 | D104*

168 | X184785Y132330D02*

169 | D03*

170 | Y139200D02*

171 | D03*

172 | Y130040D02*

173 | D03*

174 | Y134620D02*

175 | D03*

176 | Y136910D02*

177 | D03*

178 | X179705D02*

179 | D03*

180 | Y134620D02*

181 | D03*

182 | Y139200D02*

183 | D03*

184 | Y132330D02*

185 | D03*

186 | X182245Y138050D02*

187 | D03*

188 | Y135760D02*

189 | D03*

190 | Y131180D02*

191 | D03*

192 | Y140340D02*

193 | D03*

194 | Y133470D02*

195 | D03*

196 | D105*

197 | X179705Y130040D02*

198 | D03*

199 | D106*

200 | X182245Y147620D02*

201 | D03*

202 | Y121620D02*

203 | D03*

204 | D107*

205 | X186397Y116986D02*

206 | D03*

207 | Y103486D02*

208 | D03*

209 | X187197Y110236D02*

210 | D03*

211 | D108*

212 | X180897Y106836D02*

213 | D03*

214 | Y113636D02*

215 | D03*

216 | X183397Y106836D02*

217 | D03*

218 | Y113636D02*

219 | D03*

220 | Y108936D02*

221 | D03*

222 | Y111536D02*

223 | D03*

224 | D109*

225 | X189628Y79358D02*

226 | D03*

227 | X190214Y80772D02*

228 | D03*

229 | X186800Y79358D02*

230 | D03*

231 | X188214Y78772D02*

232 | D03*

233 | X186800Y82186D02*

234 | D03*

235 | X186214Y80772D02*

236 | D03*

237 | X188214Y82772D02*

238 | D03*

239 | X189628Y82186D02*

240 | D03*

241 | X57421Y79358D02*

242 | D03*

243 | X58007Y80772D02*

244 | D03*

245 | X54593Y79358D02*

246 | D03*

247 | X56007Y78772D02*

248 | D03*

249 | X54593Y82186D02*

250 | D03*

251 | X54007Y80772D02*

252 | D03*

253 | X56007Y82772D02*

254 | D03*

255 | X57421Y82186D02*

256 | D03*

257 | X189628Y151494D02*

258 | D03*

259 | X190214Y152908D02*

260 | D03*

261 | X186800Y151494D02*

262 | D03*

263 | X188214Y150908D02*

264 | D03*

265 | X186800Y154322D02*

266 | D03*

267 | X186214Y152908D02*

268 | D03*

269 | X188214Y154908D02*

270 | D03*

271 | X189628Y154322D02*

272 | D03*

273 | X57421Y151494D02*

274 | D03*

275 | X58007Y152908D02*

276 | D03*

277 | X54593Y151494D02*

278 | D03*

279 | X56007Y150908D02*

280 | D03*

281 | X54593Y154322D02*

282 | D03*

283 | X54007Y152908D02*

284 | D03*

285 | X56007Y154908D02*

286 | D03*

287 | X57421Y154322D02*

288 | D03*

289 | D110*

290 | X188214Y80772D02*

291 | D03*

292 | X56007D02*

293 | D03*

294 | X188214Y152908D02*

295 | D03*

296 | X56007D02*

297 | D03*

298 | D111*

299 | X172387Y80772D02*

300 | D03*

301 | X178387D02*

302 | D03*

303 | X175387D02*

304 | D03*

305 | D112*

306 | X180987D02*

307 | D03*

308 | X169787D02*

309 | D03*

310 | D113*

311 | X135890Y151638D02*

312 | D03*

313 | X138430D02*

314 | D03*

315 | X140970D02*

316 | D03*

317 | D114*

318 | X161036Y153924D02*

319 | D03*

320 | Y148844D02*

321 | D03*

322 | D115*

323 | Y151384D02*

324 | D03*

325 | D116*

326 | X112141Y147320D02*

327 | D03*

328 | X109474D02*

329 | D03*

330 | X106934D02*

331 | D03*

332 | X104267D02*

333 | D03*

334 | X101600D02*

335 | D03*

336 | Y155321D02*

337 | D03*

338 | X104267D02*

339 | D03*

340 | X106934D02*

341 | D03*

342 | X109474D02*

343 | D03*

344 | X98933D02*

345 | D03*

346 | X112141D02*

347 | D03*

348 | D117*

349 | X98933Y147320D02*

350 | D03*

351 | D118*

352 | X145542Y82015D02*

353 | D03*

354 | Y86895D02*

355 | D03*

356 | D119*

357 | X181597Y87579D02*

358 | D03*

359 | Y99619D02*

360 | D03*

361 | D120*

362 | X178887Y92349D02*

363 | D03*

364 | Y94849D02*

365 | D03*

366 | X176887Y92349D02*

367 | D03*

368 | D121*

369 | Y94849D02*

370 | D03*

371 | D122*

372 | X137605Y86804D02*

373 | D03*

374 | Y79820D02*

375 | D03*

376 | X126174Y86804D02*

377 | D03*

378 | Y79820D02*

379 | D03*

380 | X114744Y86932D02*

381 | D03*

382 | Y79947D02*

383 | D03*

384 | X103314Y86932D02*

385 | D03*

386 | Y79947D02*

387 | D03*

388 | D123*

389 | X133160Y86804D02*

390 | D03*

391 | Y79820D02*

392 | D03*

393 | X121729Y86804D02*

394 | D03*

395 | Y79820D02*

396 | D03*

397 | X110299Y86932D02*

398 | D03*

399 | Y79947D02*

400 | D03*

401 | X98869Y86932D02*

402 | D03*

403 | Y79947D02*

404 | D03*

405 | D124*

406 | X72898Y149733D02*

407 | D03*

408 | Y152273D02*

409 | D03*

410 | X75438Y149733D02*

411 | D03*

412 | Y152273D02*

413 | D03*

414 | X77978Y149733D02*

415 | D03*

416 | Y152273D02*

417 | D03*

418 | X80518Y149733D02*

419 | D03*

420 | Y152273D02*

421 | D03*

422 | X83058Y149733D02*

423 | D03*

424 | X67056Y112903D02*

425 | D03*

426 | X64516Y110363D02*

427 | D03*

428 | X67056D02*

429 | D03*

430 | X64516Y107823D02*

431 | D03*

432 | X67056D02*

433 | D03*

434 | X64516Y105283D02*

435 | D03*

436 | X67056D02*

437 | D03*

438 | X64516Y102743D02*

439 | D03*

440 | X67056D02*

441 | D03*

442 | X64516Y100203D02*

443 | D03*

444 | X67056D02*

445 | D03*

446 | X64516Y97663D02*

447 | D03*

448 | X67056D02*

449 | D03*

450 | X64516Y95123D02*

451 | D03*

452 | X67056D02*

453 | D03*

454 | X64516Y92583D02*

455 | D03*

456 | X67056D02*

457 | D03*

458 | X64516Y90043D02*

459 | D03*

460 | X67056D02*

461 | D03*

462 | Y143764D02*

463 | D03*

464 | X64516Y141224D02*

465 | D03*

466 | X67056D02*

467 | D03*

468 | X64516Y138684D02*

469 | D03*

470 | X67056D02*

471 | D03*

472 | X64516Y136144D02*

473 | D03*

474 | X67056D02*

475 | D03*

476 | X64516Y133604D02*

477 | D03*

478 | X67056D02*

479 | D03*

480 | X64516Y131064D02*

481 | D03*

482 | X67056D02*

483 | D03*

484 | X64516Y128524D02*

485 | D03*

486 | X67056D02*

487 | D03*

488 | X64516Y125984D02*

489 | D03*

490 | X67056D02*

491 | D03*

492 | X64516Y123444D02*

493 | D03*

494 | X67056D02*

495 | D03*

496 | D125*

497 | X83058Y152273D02*

498 | D03*

499 | D126*

500 | X64516Y112903D02*

501 | D03*

502 | Y143764D02*

503 | D03*

504 | D127*

505 | X150027Y153757D02*

506 | D03*

507 | X155027D02*

508 | D03*

509 | Y148757D02*

510 | D03*

511 | X150027D02*

512 | D03*

513 | X152527Y151257D02*

514 | D03*

515 | D128*

516 | X89789Y84963D02*

517 | D03*

518 | X82169D02*

519 | D03*

520 | M02*

521 |

--------------------------------------------------------------------------------

/Document/GERBER/HDLab.GKO:

--------------------------------------------------------------------------------

1 | %FSLAX43Y43*%

2 | %MOMM*%

3 | G71*

4 | G01*

5 | G75*

6 | G04 Layer_Color=16711935*

7 | %ADD10R,0.650X0.600*%

8 | %ADD11R,0.500X0.600*%

9 | %ADD12R,0.800X0.800*%

10 | %ADD13R,0.900X1.300*%

11 | %ADD14R,1.300X0.900*%

12 | %ADD15R,0.800X0.800*%

13 | %ADD16R,0.850X0.600*%

14 | %ADD17R,0.600X0.850*%

15 | %ADD18R,0.600X0.650*%

16 | %ADD19R,0.600X0.500*%

17 | %ADD20O,1.800X0.300*%

18 | %ADD21O,0.300X1.800*%

19 | %ADD22O,2.100X0.450*%

20 | %ADD23R,2.400X3.300*%

21 | %ADD24R,2.400X1.000*%

22 | %ADD25O,0.510X2.000*%

23 | %ADD26R,0.510X2.000*%

24 | %ADD27R,2.400X2.500*%

25 | %ADD28R,2.500X2.500*%

26 | %ADD29O,1.650X0.550*%

27 | %ADD30O,0.700X0.200*%

28 | %ADD31O,0.200X0.700*%

29 | %ADD32C,0.254*%

30 | %ADD33C,0.200*%

31 | %ADD34C,1.000*%

32 | %ADD35C,0.250*%

33 | %ADD36C,1.500*%

34 | %ADD37C,0.500*%

35 | %ADD38C,0.245*%

36 | %ADD39O,1.800X1.524*%

37 | %ADD40O,1.800X1.500*%

38 | %ADD41O,5.000X4.000*%

39 | %ADD42C,3.000*%

40 | %ADD43P,1.524X8X112.5*%

41 | %ADD44C,0.600*%

42 | %ADD45C,5.000*%

43 | %ADD46C,1.700*%

44 | %ADD47O,1.700X3.556*%

45 | G04:AMPARAMS|DCode=48|XSize=2.032mm|YSize=1.524mm|CornerRadius=0mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=Octagon|*

46 | %AMOCTAGOND48*

47 | 4,1,8,-0.381,-1.016,0.381,-1.016,0.762,-0.635,0.762,0.635,0.381,1.016,-0.381,1.016,-0.762,0.635,-0.762,-0.635,-0.381,-1.016,0.0*

48 | %

49 | %ADD48OCTAGOND48*%

50 |

51 | %ADD49O,2.400X1.800*%

52 | %ADD50R,2.400X1.800*%

53 | G04:AMPARAMS|DCode=51|XSize=1.2mm|YSize=1.6mm|CornerRadius=0.3mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=RoundedRectangle|*

54 | %AMROUNDEDRECTD51*

55 | 21,1,1.200,1.000,0,0,270.0*

56 | 21,1,0.600,1.600,0,0,270.0*

57 | 1,1,0.600,-0.500,-0.300*

58 | 1,1,0.600,-0.500,0.300*

59 | 1,1,0.600,0.500,0.300*

60 | 1,1,0.600,0.500,-0.300*

61 | %

62 | %ADD51ROUNDEDRECTD51*%

63 | %ADD52R,1.600X1.200*%

64 | %ADD53C,1.397*%

65 | %ADD54C,3.800*%

66 | %ADD55O,1.600X1.900*%

67 | %ADD56R,1.600X1.900*%

68 | %ADD57C,2.032*%

69 | %ADD58R,2.032X2.032*%

70 | %ADD59C,1.500*%

71 | %ADD60R,1.500X1.500*%

72 | %ADD61R,1.500X1.500*%

73 | %ADD62C,2.500*%

74 | %ADD63P,2.337X8X202.5*%

75 | %ADD64C,0.700*%

76 | %ADD65C,1.000*%

77 | %ADD66C,0.255*%

78 | %ADD67C,0.800*%

79 | %ADD68C,0.178*%

80 | %ADD69C,0.860*%

81 | %ADD70C,0.127*%

82 | %ADD71C,0.600*%

83 | %ADD72C,0.152*%

84 | %ADD73C,0.203*%

85 | %ADD74C,0.762*%

86 | %ADD75C,0.051*%

87 | %ADD76C,0.120*%

88 | %ADD77C,0.150*%

89 | %ADD78R,17.755X3.175*%

90 | %ADD79R,2.159X1.905*%

91 | %ADD80R,0.508X0.508*%

92 | %ADD81R,1.778X0.254*%

93 | %ADD82R,0.701X0.651*%

94 | %ADD83R,0.551X0.651*%

95 | %ADD84R,1.003X1.003*%

96 | %ADD85R,1.103X1.503*%

97 | %ADD86R,1.503X1.103*%

98 | %ADD87R,1.003X1.003*%

99 | %ADD88R,1.053X0.803*%

100 | %ADD89R,0.803X1.053*%

101 | %ADD90R,0.651X0.701*%

102 | %ADD91R,0.651X0.551*%

103 | %ADD92O,2.003X0.503*%

104 | %ADD93O,0.503X2.003*%

105 | %ADD94O,2.303X0.653*%

106 | %ADD95R,2.603X3.503*%

107 | %ADD96R,2.603X1.203*%

108 | %ADD97O,0.713X2.203*%

109 | %ADD98R,0.713X2.203*%

110 | %ADD99R,2.603X2.703*%

111 | %ADD100R,2.703X2.703*%

112 | %ADD101O,1.853X0.753*%

113 | %ADD102O,0.903X0.403*%

114 | %ADD103O,0.403X0.903*%

115 | %ADD104O,2.003X1.727*%

116 | %ADD105O,2.003X1.703*%

117 | %ADD106O,5.203X4.203*%

118 | %ADD107C,3.203*%

119 | %ADD108P,1.744X8X112.5*%

120 | %ADD109C,0.803*%

121 | %ADD110C,5.200*%

122 | %ADD111C,1.903*%

123 | %ADD112O,1.903X3.759*%

124 | G04:AMPARAMS|DCode=113|XSize=2.235mm|YSize=1.727mm|CornerRadius=0mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=Octagon|*

125 | %AMOCTAGOND113*

126 | 4,1,8,-0.432,-1.118,0.432,-1.118,0.864,-0.686,0.864,0.686,0.432,1.118,-0.432,1.118,-0.864,0.686,-0.864,-0.686,-0.432,-1.118,0.0*

127 | %

128 | %ADD113OCTAGOND113*%

129 |

130 | %ADD114O,2.603X2.003*%

131 | %ADD115R,2.603X2.003*%

132 | G04:AMPARAMS|DCode=116|XSize=1.403mm|YSize=1.803mm|CornerRadius=0.402mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=RoundedRectangle|*

133 | %AMROUNDEDRECTD116*

134 | 21,1,1.403,1.000,0,0,270.0*

135 | 21,1,0.600,1.803,0,0,270.0*

136 | 1,1,0.803,-0.500,-0.300*

137 | 1,1,0.803,-0.500,0.300*

138 | 1,1,0.803,0.500,0.300*

139 | 1,1,0.803,0.500,-0.300*

140 | %

141 | %ADD116ROUNDEDRECTD116*%

142 | %ADD117R,1.803X1.403*%

143 | %ADD118C,1.600*%

144 | %ADD119C,4.003*%

145 | %ADD120O,1.803X2.103*%

146 | %ADD121R,1.803X2.103*%

147 | %ADD122C,2.235*%

148 | %ADD123R,2.235X2.235*%

149 | %ADD124C,1.703*%

150 | %ADD125R,1.703X1.703*%

151 | %ADD126R,1.703X1.703*%

152 | %ADD127C,2.703*%

153 | %ADD128P,2.557X8X202.5*%

154 | %ADD129C,0.100*%

155 | %ADD130C,0.300*%

156 | D32*

157 | X192151Y152400D02*

158 | G03*

159 | X187960Y156865I-4328J137D01*

160 | G01*

161 | X187668Y76835D02*

162 | G03*

163 | X192133Y81026I137J4328D01*

164 | G01*

165 | X52070Y81330D02*

166 | G03*

167 | X56261Y76865I4328J-137D01*

168 | G01*

169 | X56515Y156883D02*

170 | G03*

171 | X52050Y152692I-137J-4328D01*

172 | G01*

173 | D130*

174 | X57170Y156865D02*

175 | X57188Y156883D01*

176 | X56515D02*

177 | X57188D01*

178 | X57170Y156865D02*

179 | X187960D01*

180 | X192133Y81026D02*

181 | Y152400D01*

182 | X56261Y76865D02*

183 | X187668D01*

184 | X52070Y81330D02*

185 | Y152692D01*

186 | M02*

187 |

--------------------------------------------------------------------------------

/Document/GERBER/HDLab.GPB:

--------------------------------------------------------------------------------

1 | %FSLAX43Y43*%

2 | %MOMM*%

3 | G71*

4 | G01*

5 | G75*

6 | G04 Layer_Color=255*

7 | %ADD10R,0.650X0.600*%

8 | %ADD11R,0.500X0.600*%

9 | %ADD12R,0.800X0.800*%

10 | %ADD13R,0.900X1.300*%

11 | %ADD14R,1.300X0.900*%

12 | %ADD15R,0.800X0.800*%

13 | %ADD16R,0.850X0.600*%

14 | %ADD17R,0.600X0.850*%

15 | %ADD18R,0.600X0.650*%

16 | %ADD19R,0.600X0.500*%

17 | %ADD20O,1.800X0.300*%

18 | %ADD21O,0.300X1.800*%

19 | %ADD22O,2.100X0.450*%

20 | %ADD23R,2.400X3.300*%

21 | %ADD24R,2.400X1.000*%

22 | %ADD25O,0.510X2.000*%

23 | %ADD26R,0.510X2.000*%

24 | %ADD27R,2.400X2.500*%

25 | %ADD28R,2.500X2.500*%

26 | %ADD29O,1.650X0.550*%

27 | %ADD30O,0.700X0.200*%

28 | %ADD31O,0.200X0.700*%

29 | %ADD32C,0.254*%

30 | %ADD33C,0.200*%

31 | %ADD34C,1.000*%

32 | %ADD35C,0.250*%

33 | %ADD36C,1.500*%

34 | %ADD37C,0.500*%

35 | %ADD38C,0.245*%

36 | %ADD39O,1.800X1.524*%

37 | %ADD40O,1.800X1.500*%

38 | %ADD41O,5.000X4.000*%

39 | %ADD42C,3.000*%

40 | %ADD43P,1.524X8X112.5*%

41 | %ADD44C,0.600*%

42 | %ADD45C,5.000*%

43 | %ADD46C,1.700*%

44 | %ADD47O,1.700X3.556*%

45 | G04:AMPARAMS|DCode=48|XSize=2.032mm|YSize=1.524mm|CornerRadius=0mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=Octagon|*

46 | %AMOCTAGOND48*

47 | 4,1,8,-0.381,-1.016,0.381,-1.016,0.762,-0.635,0.762,0.635,0.381,1.016,-0.381,1.016,-0.762,0.635,-0.762,-0.635,-0.381,-1.016,0.0*

48 | %

49 | %ADD48OCTAGOND48*%

50 |

51 | %ADD49O,2.400X1.800*%

52 | %ADD50R,2.400X1.800*%

53 | G04:AMPARAMS|DCode=51|XSize=1.2mm|YSize=1.6mm|CornerRadius=0.3mm|HoleSize=0mm|Usage=FLASHONLY|Rotation=270.000|XOffset=0mm|YOffset=0mm|HoleType=Round|Shape=RoundedRectangle|*

54 | %AMROUNDEDRECTD51*

55 | 21,1,1.200,1.000,0,0,270.0*

56 | 21,1,0.600,1.600,0,0,270.0*

57 | 1,1,0.600,-0.500,-0.300*

58 | 1,1,0.600,-0.500,0.300*

59 | 1,1,0.600,0.500,0.300*

60 | 1,1,0.600,0.500,-0.300*

61 | %

62 | %ADD51ROUNDEDRECTD51*%

63 | %ADD52R,1.600X1.200*%

64 | %ADD53C,1.397*%

65 | %ADD54C,3.800*%

66 | %ADD55O,1.600X1.900*%

67 | %ADD56R,1.600X1.900*%

68 | %ADD57C,2.032*%

69 | %ADD58R,2.032X2.032*%

70 | %ADD59C,1.500*%

71 | %ADD60R,1.500X1.500*%

72 | %ADD61R,1.500X1.500*%

73 | %ADD62C,2.500*%

74 | %ADD63P,2.337X8X202.5*%

75 | %ADD64C,0.700*%

76 | %ADD65C,1.000*%

77 | %ADD66C,0.255*%

78 | %ADD67C,0.800*%

79 | D16*

80 | X96647Y114808D02*

81 | D03*

82 | Y116052D02*

83 | D03*

84 | X69977Y142748D02*

85 | D03*

86 | Y143992D02*

87 | D03*

88 | X71628Y142748D02*

89 | D03*

90 | Y143992D02*

91 | D03*

92 | D39*

93 | X184785Y132330D02*

94 | D03*

95 | Y139200D02*

96 | D03*

97 | Y130040D02*

98 | D03*

99 | Y134620D02*

100 | D03*

101 | Y136910D02*

102 | D03*

103 | X179705D02*

104 | D03*

105 | Y134620D02*

106 | D03*

107 | Y139200D02*

108 | D03*

109 | Y132330D02*

110 | D03*

111 | X182245Y138050D02*

112 | D03*

113 | Y135760D02*

114 | D03*

115 | Y131180D02*

116 | D03*

117 | Y140340D02*

118 | D03*

119 | Y133470D02*

120 | D03*

121 | D40*

122 | X179705Y130040D02*

123 | D03*

124 | D41*

125 | X182245Y147620D02*

126 | D03*

127 | Y121620D02*

128 | D03*

129 | D42*

130 | X186397Y116986D02*

131 | D03*

132 | Y103486D02*

133 | D03*

134 | X187197Y110236D02*

135 | D03*

136 | D43*

137 | X180897Y106836D02*

138 | D03*

139 | Y113636D02*

140 | D03*

141 | X183397Y106836D02*

142 | D03*

143 | Y113636D02*

144 | D03*

145 | Y108936D02*

146 | D03*

147 | Y111536D02*

148 | D03*

149 | D44*

150 | X189628Y79358D02*

151 | D03*

152 | X190214Y80772D02*

153 | D03*

154 | X186800Y79358D02*

155 | D03*

156 | X188214Y78772D02*

157 | D03*

158 | X186800Y82186D02*

159 | D03*

160 | X186214Y80772D02*

161 | D03*

162 | X188214Y82772D02*

163 | D03*

164 | X189628Y82186D02*

165 | D03*

166 | X57421Y79358D02*

167 | D03*

168 | X58007Y80772D02*

169 | D03*

170 | X54593Y79358D02*

171 | D03*

172 | X56007Y78772D02*

173 | D03*

174 | X54593Y82186D02*

175 | D03*

176 | X54007Y80772D02*

177 | D03*

178 | X56007Y82772D02*

179 | D03*

180 | X57421Y82186D02*

181 | D03*

182 | X189628Y151494D02*

183 | D03*

184 | X190214Y152908D02*

185 | D03*

186 | X186800Y151494D02*

187 | D03*

188 | X188214Y150908D02*

189 | D03*

190 | X186800Y154322D02*

191 | D03*

192 | X186214Y152908D02*

193 | D03*

194 | X188214Y154908D02*

195 | D03*

196 | X189628Y154322D02*

197 | D03*

198 | X57421Y151494D02*

199 | D03*

200 | X58007Y152908D02*

201 | D03*

202 | X54593Y151494D02*

203 | D03*

204 | X56007Y150908D02*

205 | D03*

206 | X54593Y154322D02*

207 | D03*

208 | X54007Y152908D02*

209 | D03*

210 | X56007Y154908D02*

211 | D03*

212 | X57421Y154322D02*

213 | D03*

214 | D45*

215 | X188214Y80772D02*

216 | D03*

217 | X56007D02*

218 | D03*

219 | X188214Y152908D02*

220 | D03*

221 | X56007D02*

222 | D03*

223 | D46*

224 | X172387Y80772D02*

225 | D03*

226 | X178387D02*

227 | D03*

228 | X175387D02*

229 | D03*

230 | D47*

231 | X180987D02*

232 | D03*

233 | X169787D02*

234 | D03*

235 | D48*

236 | X135890Y151638D02*

237 | D03*

238 | X138430D02*

239 | D03*

240 | X140970D02*

241 | D03*

242 | D49*

243 | X161036Y153924D02*

244 | D03*

245 | Y148844D02*

246 | D03*

247 | D50*

248 | Y151384D02*

249 | D03*

250 | D51*

251 | X112141Y147320D02*

252 | D03*

253 | X109474D02*

254 | D03*

255 | X106934D02*

256 | D03*

257 | X104267D02*

258 | D03*

259 | X101600D02*

260 | D03*

261 | Y155321D02*

262 | D03*

263 | X104267D02*

264 | D03*

265 | X106934D02*

266 | D03*

267 | X109474D02*

268 | D03*

269 | X98933D02*

270 | D03*

271 | X112141D02*

272 | D03*

273 | D52*

274 | X98933Y147320D02*

275 | D03*

276 | D53*

277 | X145542Y82015D02*

278 | D03*

279 | Y86895D02*

280 | D03*

281 | D54*

282 | X181597Y87579D02*

283 | D03*

284 | Y99619D02*

285 | D03*

286 | D55*

287 | X178887Y92349D02*

288 | D03*

289 | Y94849D02*

290 | D03*

291 | X176887Y92349D02*

292 | D03*

293 | D56*

294 | Y94849D02*

295 | D03*

296 | D57*

297 | X137605Y86804D02*

298 | D03*

299 | Y79820D02*

300 | D03*

301 | X126174Y86804D02*

302 | D03*

303 | Y79820D02*

304 | D03*

305 | X114744Y86932D02*

306 | D03*

307 | Y79947D02*

308 | D03*

309 | X103314Y86932D02*

310 | D03*

311 | Y79947D02*

312 | D03*

313 | D58*

314 | X133160Y86804D02*

315 | D03*

316 | Y79820D02*

317 | D03*

318 | X121729Y86804D02*

319 | D03*

320 | Y79820D02*

321 | D03*

322 | X110299Y86932D02*

323 | D03*

324 | Y79947D02*

325 | D03*

326 | X98869Y86932D02*

327 | D03*

328 | Y79947D02*

329 | D03*

330 | D59*

331 | X72898Y149733D02*

332 | D03*

333 | Y152273D02*

334 | D03*

335 | X75438Y149733D02*

336 | D03*

337 | Y152273D02*

338 | D03*

339 | X77978Y149733D02*

340 | D03*

341 | Y152273D02*

342 | D03*

343 | X80518Y149733D02*

344 | D03*

345 | Y152273D02*

346 | D03*

347 | X83058Y149733D02*

348 | D03*

349 | X67056Y112903D02*

350 | D03*

351 | X64516Y110363D02*

352 | D03*

353 | X67056D02*

354 | D03*

355 | X64516Y107823D02*

356 | D03*

357 | X67056D02*

358 | D03*

359 | X64516Y105283D02*

360 | D03*

361 | X67056D02*

362 | D03*

363 | X64516Y102743D02*

364 | D03*

365 | X67056D02*

366 | D03*

367 | X64516Y100203D02*

368 | D03*

369 | X67056D02*

370 | D03*

371 | X64516Y97663D02*

372 | D03*

373 | X67056D02*

374 | D03*

375 | X64516Y95123D02*

376 | D03*

377 | X67056D02*

378 | D03*

379 | X64516Y92583D02*

380 | D03*

381 | X67056D02*

382 | D03*

383 | X64516Y90043D02*

384 | D03*

385 | X67056D02*

386 | D03*

387 | Y143764D02*

388 | D03*

389 | X64516Y141224D02*

390 | D03*

391 | X67056D02*

392 | D03*

393 | X64516Y138684D02*

394 | D03*

395 | X67056D02*

396 | D03*

397 | X64516Y136144D02*

398 | D03*

399 | X67056D02*

400 | D03*

401 | X64516Y133604D02*

402 | D03*

403 | X67056D02*

404 | D03*

405 | X64516Y131064D02*

406 | D03*

407 | X67056D02*

408 | D03*

409 | X64516Y128524D02*

410 | D03*

411 | X67056D02*

412 | D03*

413 | X64516Y125984D02*

414 | D03*

415 | X67056D02*

416 | D03*

417 | X64516Y123444D02*

418 | D03*

419 | X67056D02*

420 | D03*

421 | D60*

422 | X83058Y152273D02*

423 | D03*

424 | D61*

425 | X64516Y112903D02*

426 | D03*

427 | Y143764D02*

428 | D03*

429 | D62*

430 | X150027Y153757D02*

431 | D03*

432 | X155027D02*

433 | D03*

434 | Y148757D02*

435 | D03*

436 | X150027D02*

437 | D03*

438 | X152527Y151257D02*

439 | D03*

440 | D63*

441 | X89789Y84963D02*

442 | D03*

443 | X82169D02*

444 | D03*

445 | M02*

446 |

--------------------------------------------------------------------------------

/Document/GERBER/HDLab.GPT:

--------------------------------------------------------------------------------

1 | %FSLAX43Y43*%

2 | %MOMM*%

3 | G71*

4 | G01*

5 | G75*

6 | %ADD10R,0.650X0.600*%