├── CAR.vhd

├── CZN.vhd

├── ControlMemory.vhd

├── Controller.vhd

├── DI.vhd

├── DataPath.vhd

├── IR.vhd

├── LICENSE

├── MDR.vhd

├── MEM.vhd

├── Main.vhd

├── MyCPU.pdf

├── PC.vhd

├── README.md

├── ROM1.vhd

├── ROM2.vhd

├── RegFile.vhd

├── _config.yml

├── adder.vhd

├── alu.vhd

├── mux.vhd

├── mux_2bits.vhd

└── wave1.wcfg

/CAR.vhd:

--------------------------------------------------------------------------------

1 | ----------------------------------------------------------------------------------

2 | -- Company:

3 | -- Engineer:

4 | --

5 | -- Create Date: 20:52:36 06/25/2017

6 | -- Design Name:

7 | -- Module Name: CAR - Behavioral

8 | -- Project Name:

9 | -- Target Devices:

10 | -- Tool versions:

11 | -- Description:

12 | --

13 | -- Dependencies:

14 | --

15 | -- Revision:

16 | -- Revision 0.01 - File Created

17 | -- Additional Comments:

18 | --

19 | ----------------------------------------------------------------------------------

20 | library IEEE;

21 | use IEEE.STD_LOGIC_1164.ALL;

22 |

23 | -- Uncomment the following library declaration if using

24 | -- arithmetic functions with Signed or Unsigned values

25 | --use IEEE.NUMERIC_STD.ALL;

26 |

27 | -- Uncomment the following library declaration if instantiating

28 | -- any Xilinx primitives in this code.

29 | --library UNISIM;

30 | --use UNISIM.VComponents.all;

31 |

32 | entity CAR is

33 | port( clk, rst_n : in std_logic;

34 | memIndex_input : in std_logic_vector(3 downto 0);

35 | memIndex_output : out std_logic_vector(3 downto 0)

36 | );

37 | end CAR;

38 |

39 | architecture Behavioral of CAR is

40 | signal temp : std_logic_vector(3 downto 0):="0000";

41 | begin

42 | process(clk, rst_n) begin

43 | if rst_n = '0' then

44 | temp <= "1111";

45 | else

46 | if rising_edge(clk) then

47 | temp <= memIndex_input;

48 | end if;

49 | end if;

50 | end process;

51 | memindex_output <= temp;

52 |

53 |

54 | end Behavioral;

55 |

56 |

--------------------------------------------------------------------------------

/CZN.vhd:

--------------------------------------------------------------------------------

1 | ----------------------------------------------------------------------------------

2 | -- Company:

3 | -- Engineer:

4 | --

5 | -- Create Date: 17:47:34 06/25/2017

6 | -- Design Name:

7 | -- Module Name: CZN - Behavioral

8 | -- Project Name:

9 | -- Target Devices:

10 | -- Tool versions:

11 | -- Description:

12 | --

13 | -- Dependencies:

14 | --

15 | -- Revision:

16 | -- Revision 0.01 - File Created

17 | -- Additional Comments:

18 | --

19 | ----------------------------------------------------------------------------------

20 | library IEEE;

21 | use IEEE.STD_LOGIC_1164.ALL;

22 |

23 | -- Uncomment the following library declaration if using

24 | -- arithmetic functions with Signed or Unsigned values

25 | use IEEE.NUMERIC_STD.ALL;

26 |

27 | -- Uncomment the following library declaration if instantiating

28 | -- any Xilinx primitives in this code.

29 | --library UNISIM;

30 | --use UNISIM.VComponents.all;

31 |

32 | entity CZN is

33 | port(

34 | clk : in std_logic;

35 | cznWrite : in std_logic;

36 | CZNin : in std_logic_vector(2 downto 0);

37 | CZNout : out std_logic_vector(2 downto 0)

38 | );

39 | end CZN;

40 |

41 | architecture behave of CZN is

42 |

43 | begin

44 | process (clk) begin

45 | if rising_edge(clk) then

46 | if cznWrite = '1' then

47 | CZNout <= CZNin;

48 | end if;

49 | end if;

50 | end process;

51 |

52 | end behave;

53 |

54 |

--------------------------------------------------------------------------------

/ControlMemory.vhd:

--------------------------------------------------------------------------------

1 | ----------------------------------------------------------------------------------

2 | -- Company:

3 | -- Engineer:

4 | --

5 | -- Create Date: 20:53:57 06/25/2017

6 | -- Design Name:

7 | -- Module Name: ControlMemory - Behavioral

8 | -- Project Name:

9 | -- Target Devices:

10 | -- Tool versions:

11 | -- Description:

12 | --

13 | -- Dependencies:

14 | --

15 | -- Revision:

16 | -- Revision 0.01 - File Created

17 | -- Additional Comments:

18 | --

19 | ----------------------------------------------------------------------------------

20 | library IEEE;

21 | use IEEE.std_logic_1164.all;

22 | use IEEE.std_logic_unsigned.all;

23 |

24 | entity ControlMemory is

25 | generic (K: integer:=19; -- number of bits per word (data size)

26 | W: integer:=4 -- number of address bits (address size)

27 | );

28 | port (

29 | clk, rst_n : std_logic;

30 | ADDR: in std_logic_vector (W-1 downto 0); -- RAM address

31 | DOUT: out std_logic_vector (K-1 downto 0)); -- read data

32 | end ControlMemory;

33 |

34 |

35 | architecture behave of ControlMemory is

36 |

37 | subtype WORD is std_logic_vector ( K-1 downto 0); -- define size of WORD

38 | type MEMORY is array (0 to 2**W-1) of WORD; -- define size of MEMORY

39 | signal RAM16: MEMORY; -- define RAM16 as signal of type MEMORY

40 |

41 | begin

42 | process (clk, rst_n, ADDR, RAM16)

43 |

44 | variable RAM_ADDR_IN: integer range 0 to 2**W-1; -- to translate address to integer

45 | --variable STARTUP: boolean :=true; -- temporary variable for initialization

46 |

47 | begin

48 | if (rst_n = '0') then -- for initialization of RAM during start of simulation

49 | RAM16 <= (0 => "0100010000000000011", -- initializes first 12 locations in Control Memory

50 | 1 => "0000001000000000001", -- to specific values

51 | 2 => "0000000110100000000",

52 | 3 => "0000000110100100100",

53 | 4 => "0000000110101000100",

54 | 5 => "0000000110101010100",

55 | 6 => "0000000000000001000",

56 | 7 => "0001000000000000010",

57 | 8 => "1010000000000000000",

58 | 9 => "0100000001100000000",

59 | 10 => "0101100000000000000",

60 | 11 => "0100000000110010100",

61 | 12 => "0100000000111000100",

62 | others => "0000000000000000000"

63 | );

64 | DOUT <= "XXXXXXXXXXXXXXXXXXX"; -- force undefined logic values on RAM output

65 | else

66 | --if rising_edge(clk) then

67 | RAM_ADDR_IN := conv_integer (ADDR); -- converts address to integer

68 | --end if;

69 | DOUT <= RAM16 (RAM_ADDR_IN);

70 | end if;

71 | end process;

72 |

73 | end architecture behave;

74 |

75 |

--------------------------------------------------------------------------------

/Controller.vhd:

--------------------------------------------------------------------------------

1 | ----------------------------------------------------------------------------------

2 | -- Company:

3 | -- Engineer:

4 | --

5 | -- Create Date: 20:19:14 06/25/2017

6 | -- Design Name:

7 | -- Module Name: Controller - Behavioral

8 | -- Project Name:

9 | -- Target Devices:

10 | -- Tool versions:

11 | -- Description:

12 | --

13 | -- Dependencies:

14 | --

15 | -- Revision:

16 | -- Revision 0.01 - File Created

17 | -- Additional Comments:

18 | --

19 | ----------------------------------------------------------------------------------

20 | library IEEE;

21 | use IEEE.STD_LOGIC_1164.ALL;

22 |

23 | -- Uncomment the following library declaration if using

24 | -- arithmetic functions with Signed or Unsigned values

25 | --use IEEE.NUMERIC_STD.ALL;

26 | use ieee.std_logic_unsigned.all;

27 |

28 | -- Uncomment the following library declaration if instantiating

29 | -- any Xilinx primitives in this code.

30 | --library UNISIM;

31 | --use UNISIM.VComponents.all;

32 |

33 | entity Controller is

34 | port( clk, reset: in std_logic;

35 | opcode: in std_logic_vector(3 downto 0);

36 | pcSrc, pcWrite, pcWriteCond, IorD, MemWrite, IRWrite1, IRWrite2, MUXR1,

37 | RegDST, MemToReg, RegWrite, AluSrc2, DIWrite, CZNWrite : out std_logic;

38 | AluOp : out std_logic_vector(2 downto 0);

39 | controlmemData : out std_logic_vector(18 downto 0);

40 | nxtline :out std_logic_vector(3 downto 0);

41 | cardata : out std_logic_vector(3 downto 0)

42 | );

43 |

44 | end Controller;

45 |

46 | architecture behave of Controller is

47 |

48 | component ROM1 is

49 | port(

50 | opcode: in std_logic_vector(3 downto 0);

51 | lineNumber: out std_logic_vector(3 downto 0)

52 | );

53 | end component;

54 |

55 | component ROM2 is

56 | port(

57 | opcode: in std_logic_vector(2 downto 0);

58 | lineNumber: out std_logic_vector(3 downto 0)

59 | );

60 | end component;

61 |

62 | component ControlMemory is

63 | generic (K: integer:=19; -- number of bits per word (data size)

64 | W: integer:=4 -- number of address bits (address size)

65 | );

66 | port ( clk, rst_n : std_logic;

67 | ADDR: in std_logic_vector (W-1 downto 0); -- RAM address

68 | DOUT: out std_logic_vector (K-1 downto 0)

69 | ); -- read data

70 | end component;

71 |

72 | component CAR is

73 | port( clk, rst_n : in std_logic;

74 | memIndex_input : in std_logic_vector(3 downto 0);

75 | memIndex_output : out std_logic_vector(3 downto 0)

76 | );

77 | end component;

78 |

79 | component mux_2bits is

80 | Generic(W : integer :=4);

81 | Port (D0, D1, D2, D3 : in std_logic_vector(W-1 downto 0);

82 | S : in std_logic_vector(1 downto 0);

83 | Y : out std_logic_vector(W-1 downto 0));

84 | end component;

85 |

86 | signal rom1ToMux : std_logic_vector(3 downto 0);

87 | signal rom2ToMux : std_logic_vector(3 downto 0);

88 | signal nextLine : std_logic_vector(3 downto 0);

89 | signal seq : std_logic_vector(1 downto 0) := "00";

90 | signal muxOut : std_logic_vector(3 downto 0);

91 | signal CARout : std_logic_vector(3 downto 0);

92 | signal controlWord : std_logic_vector(18 downto 0) := (others => '0');

93 | signal nextlinetemp : std_logic_vector(3 downto 0);

94 | signal zero4Signal : std_logic_vector(3 downto 0);

95 |

96 |

97 | begin

98 | R1: ROM1 port map(opcode, rom1ToMux);

99 | R2: ROM2 port map(opcode(3 downto 1), rom2ToMux);

100 |

101 | zero4signal <= "0000";

102 | M: mux_2bits port map(zero4signal, rom1ToMux, rom2ToMux, nextLine, seq, muxOut);

103 |

104 | C: CAR port map(clk, reset, muxOut, CARout);

105 | cardata <= carout;

106 |

107 | Mem: ControlMemory port map(clk, reset, CARout, controlWord);

108 |

109 | seq <= controlWord(1 downto 0);

110 | nextlinetemp <= CARout + "0001";

111 | nextLine <= nextlinetemp;

112 | nxtline <= nextline;

113 | controlmemData <= controlword;

114 |

115 | process (clk, reset, controlword) begin

116 | if(reset = '0') then

117 | pcsrc <= '0';

118 | pcwrite <= '0';

119 | pcwritecond <= '0';

120 | iord <= '0';

121 | memwrite <= '0';

122 | irwrite1 <= '0';

123 | irwrite2 <= '0';

124 | muxr1 <= '0';

125 | regdst <= '0';

126 | memtoreg <= '0';

127 | regwrite <= '0';

128 | alusrc2 <= '0';

129 | aluop <= "000";

130 | diwrite <= '0';

131 | cznwrite <= '0';

132 | else

133 | pcsrc <= controlWord(18);

134 | pcwrite <= controlWord(17);

135 | pcwritecond <= controlWord(16);

136 | iord <= controlWord(15);

137 | memwrite <= controlWord(14);

138 | irwrite1 <= controlWord(13);

139 | irwrite2 <= controlWord(12);

140 | muxr1 <= controlWord(11);

141 | regdst <= controlWord(10);

142 | memtoreg <= controlWord(9);

143 | regwrite <= controlWord(8);

144 | alusrc2 <= controlWord(7);

145 | aluop <= controlWord(6 downto 4);

146 | diwrite <= controlWord(3);

147 | cznwrite <= controlWord(2);

148 | end if;

149 | end process;

150 |

151 |

152 | end behave;

153 |

154 |

--------------------------------------------------------------------------------

/DI.vhd:

--------------------------------------------------------------------------------

1 | ----------------------------------------------------------------------------------

2 | -- Company:

3 | -- Engineer:

4 | --

5 | -- Create Date: 17:03:20 06/25/2017

6 | -- Design Name:

7 | -- Module Name: DI - Behavioral

8 | -- Project Name:

9 | -- Target Devices:

10 | -- Tool versions:

11 | -- Description:

12 | --

13 | -- Dependencies:

14 | --

15 | -- Revision:

16 | -- Revision 0.01 - File Created

17 | -- Additional Comments:

18 | --

19 | ----------------------------------------------------------------------------------

20 | library IEEE;

21 | use IEEE.STD_LOGIC_1164.ALL;

22 |

23 | -- Uncomment the following library declaration if using

24 | -- arithmetic functions with Signed or Unsigned values

25 | use IEEE.NUMERIC_STD.ALL;

26 |

27 | -- Uncomment the following library declaration if instantiating

28 | -- any Xilinx primitives in this code.

29 | --library UNISIM;

30 | --use UNISIM.VComponents.all;

31 |

32 | entity DI is

33 | port( clk : in std_logic;

34 | rst_n : in std_logic;

35 | writeDI : in std_logic;

36 | Din : in std_logic_vector(4 downto 0);

37 | Dout : out std_logic_vector(4 downto 0)

38 | );

39 | end DI;

40 |

41 | architecture behave of DI is

42 |

43 | begin

44 | process (clk, rst_n)

45 | begin

46 | if rst_n = '0' then

47 | Dout <= (others => '0');

48 | elsif rising_edge(clk) then

49 | if(writeDI = '1') then

50 | Dout <= Din;

51 | end if;

52 | end if;

53 | end process;

54 |

55 | end behave;

56 |

57 |

--------------------------------------------------------------------------------

/DataPath.vhd:

--------------------------------------------------------------------------------

1 | ----------------------------------------------------------------------------------

2 | -- Company:

3 | -- Engineer:

4 | --

5 | -- Create Date: 17:30:37 06/25/2017

6 | -- Design Name:

7 | -- Module Name: DataPath - Behavioral

8 | -- Project Name:

9 | -- Target Devices:

10 | -- Tool versions:

11 | -- Description:

12 | --

13 | -- Dependencies:

14 | --

15 | -- Revision:

16 | -- Revision 0.01 - File Created

17 | -- Additional Comments:

18 | --

19 | ----------------------------------------------------------------------------------

20 | library IEEE;

21 | use IEEE.STD_LOGIC_1164.ALL;

22 |

23 | -- Uncomment the following library declaration if using

24 | -- arithmetic functions with Signed or Unsigned values

25 | use IEEE.NUMERIC_STD.ALL;

26 |

27 | -- Uncomment the following library declaration if instantiating

28 | -- any Xilinx primitives in this code.

29 | --library UNISIM;

30 | --use UNISIM.VComponents.all;

31 |

32 | entity DataPath is

33 | port(

34 | clk : in std_logic;

35 | reset : in std_logic;

36 | pcSrc, pcWrite, pcWriteCond, IorD, MemWrite, IRWrite1, IRWrite2, MUXR1,

37 | RegDST, MemToReg, RegWrite, AluSrc2, DIWrite, CZNWrite : in std_logic;

38 | AluOp : in std_logic_vector(2 downto 0);

39 | opcode : out std_logic_vector(3 downto 0);

40 | memorydata : out std_logic_vector(7 downto 0);

41 | aluResult : out std_logic_vector(7 downto 0)

42 | );

43 | end DataPath;

44 |

45 | architecture rtl of DataPath is

46 |

47 | component pc is

48 | generic(width: natural := 13);

49 | PORT (

50 | clk : IN STD_LOGIC;

51 | rst_n : IN STD_LOGIC;

52 | pc_in : IN STD_LOGIC_VECTOR(width-1 DOWNTO 0);

53 | PC_en : IN STD_LOGIC;

54 | pc_out : OUT STD_LOGIC_VECTOR(width-1 DOWNTO 0)

55 | );

56 | END component;

57 |

58 | component MEM is

59 | port (

60 | clock : in std_logic;

61 | rst_n : in std_logic;

62 | we : in std_logic;

63 | address : in std_logic_vector(12 downto 0);

64 | datain : in std_logic_vector(7 downto 0);

65 | dataout : out std_logic_vector(7 downto 0)

66 | );

67 | end component;

68 |

69 | component adder is

70 | Port (A, B : in std_logic_vector(12 downto 0);

71 | Y : out std_logic_vector(12 downto 0)

72 | );

73 | End component;

74 |

75 | component IR IS

76 | generic (width : natural :=8);

77 | PORT (

78 | clk : IN STD_LOGIC; -- clock signal

79 | rst_n : IN STD_LOGIC; -- reset signal

80 | memdata : IN STD_LOGIC_VECTOR(width-1 DOWNTO 0); -- memoryData stored into the IR

81 | IRWrite : IN STD_LOGIC;

82 | instr : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

83 | );

84 | END component;

85 |

86 | component MDR IS

87 | generic (width : natural :=8);

88 | PORT (

89 | clk : IN STD_LOGIC; -- clock signal

90 | rst_n : IN STD_LOGIC; -- reset signal

91 | memdata : IN STD_LOGIC_VECTOR(width-1 DOWNTO 0); -- memoryData stored into the IR

92 | dataOut : OUT STD_LOGIC_VECTOR(width-1 DOWNTO 0)

93 | );

94 | END component;

95 |

96 | component DI is

97 | port( clk : in std_logic;

98 | rst_n : in std_logic;

99 | writeDI : in std_logic;

100 | Din : in std_logic_vector(4 downto 0);

101 | Dout : out std_logic_vector(4 downto 0)

102 | );

103 | end component;

104 |

105 | component alu is

106 | Generic(W : natural := 8; Cw : natural := 3);

107 | port(SrcA : in std_logic_vector(W-1 downto 0);

108 | SrcB : in std_logic_vector(W-1 downto 0);

109 | Cin : in std_logic;

110 | AluControl : in std_logic_vector(Cw-1 downto 0);

111 | AluResult : out std_logic_vector(W-1 downto 0);

112 | Zero : out std_logic;

113 | Overflow : out std_logic;

114 | CarryOut : out std_logic;

115 | Neg : out std_logic --negative signal

116 | );

117 | End component;

118 |

119 | component CZN is

120 | port(

121 | clk : in std_logic;

122 | cznWrite : in std_logic;

123 | CZNin : in std_logic_vector(2 downto 0);

124 | CZNout : out std_logic_vector(2 downto 0)

125 | );

126 | end component ;

127 |

128 | component mux is

129 | Generic(W : integer );

130 | Port (D0, D1 : in std_logic_vector(W-1 downto 0);

131 | S : in std_logic;

132 | Y : out std_logic_vector(W-1 downto 0));

133 | End component ;

134 |

135 | component regfile IS

136 | GENERIC ( width : natural := 8; --data width

137 | regfile_depth : positive := 4; --number of accumulator registers

138 | regfile_adrsize : positive := 2 --address size for addressing acc. registers

139 | );

140 | PORT (clk,rst_n : IN std_logic;

141 | RegWrite : IN std_logic; -- write control

142 | writeport : IN std_logic_vector(width-1 DOWNTO 0); -- register input

143 | adrwport : IN std_logic_vector(regfile_adrsize-1 DOWNTO 0);-- address write

144 | adrport0 : IN std_logic_vector(regfile_adrsize-1 DOWNTO 0);-- address port 0

145 | adrport1 : IN std_logic_vector(regfile_adrsize-1 DOWNTO 0);-- address port 1

146 | readport0 : OUT std_logic_vector(width-1 DOWNTO 0); -- output port 0

147 | readport1 : OUT std_logic_vector(width-1 DOWNTO 0) -- output port 1

148 | );

149 |

150 | END component;

151 |

152 | component mux_2bits is

153 | Generic(W : integer :=1);

154 | Port (D0, D1, D2, D3 : in std_logic_vector(W-1 downto 0);

155 | S : in std_logic_vector(1 downto 0);

156 | Y : out std_logic_vector(W-1 downto 0));

157 | end component;

158 |

159 |

160 | signal pcin : std_logic_vector(12 downto 0) := "0000000000000";

161 | --signal reset : std_logic := '0';

162 | signal pcen : std_logic; --pc enable signal

163 | signal pcout : std_logic_vector(12 downto 0);

164 | signal mux1out : std_logic_vector(12 downto 0);

165 | signal memdata : std_logic_vector(7 downto 0);

166 | --signal IRreset : std_logic :='0';

167 | signal instr1 : std_logic_vector(7 downto 0) ;

168 | signal instr2 : std_logic_vector(7 downto 0);

169 | signal mux1D1 : std_logic_vector(12 downto 0);

170 | signal mdrdata : std_logic_vector(7 downto 0) ;

171 | signal Acci : std_logic_vector(7 downto 0);

172 | signal Accj : std_logic_vector(7 downto 0);

173 | signal regfileWD : std_logic_vector(7 downto 0);

174 | signal regfileWR : std_logic_vector(1 downto 0);

175 | signal regfileR1 : std_logic_vector(1 downto 0) ;

176 | signal regfileR2 : std_logic_vector(1 downto 0);

177 | --signal regfilereset : std_logic := '0';

178 | signal DIout : std_logic_vector(4 downto 0); -- output of DI register

179 | signal nextLinePc : std_logic_vector(12 downto 0);

180 | signal jumpPc : std_logic_vector(12 downto 0);

181 | signal AluIn2 : std_logic_vector(7 downto 0) ; -- alu in B

182 | signal CZNin : std_logic_vector(2 downto 0) ;

183 | signal CZNout : std_logic_vector(2 downto 0) ;

184 | signal C : std_logic := '0';

185 | signal Z : std_logic := '0';

186 | signal N : std_logic := '0';

187 | signal overflow : std_logic := '0';

188 | --signal DIreset: std_logic := '0';

189 | signal aluout : std_logic_vector(7 downto 0);

190 | signal m0out : std_logic;

191 |

192 |

193 |

194 | begin

195 | --M0: mux_2bits port map(logicone, c, z, n, diout(2 downto 1), m0out);

196 | m0out <= ((not diout(2)) and (not diout(1))) or ((not diout(2)) and diout(1) and c)

197 | or (diout(2) and (not diout(1)) and z) or (diout(2) and diout(1) and n);

198 |

199 | pcen <= ((m0out and pcwritecond)or(pcwrite));

200 | myPC : PC port map(clk, reset, pcin, pcen, pcout);

201 |

202 | mux1d1 <= (instr1(4 downto 0) & instr2);

203 | M1 : mux generic map(13) port map(pcout, mux1D1, IorD, mux1out);

204 |

205 | IR1 : IR port map(clk, reset, memdata, irwrite1, instr1);

206 | opcode <= instr1(7 downto 4);

207 | IR2 : IR port map(clk, reset, memdata, irwrite2, instr2);

208 | myMDR : MDR port map(clk, reset, memdata, mdrdata);

209 |

210 | RAM : MEM port map(clk, reset, memwrite, mux1out, acci, memdata);

211 | memorydata <= memdata;

212 |

213 | regfiler2 <= instr1(3 downto 2);

214 | myREGFILE : regFile port map(clk, reset, regwrite, regfileWD, regfileWR, regfileR1, regfileR2, acci, accj);

215 |

216 | M2 : mux generic map(2) port map(diout(4 downto 3), instr1(1 downto 0), muxR1, regfiler1);

217 | M3 : mux generic map(2) port map(diout(4 downto 3), instr1(1 downto 0), regdst, regfilewr);

218 | M4 : mux generic map(8) port map(aluout, mdrdata, memtoreg, regfilewd);

219 |

220 | PCAdd : adder port map (pcout, "0000000000001", nextlinepc);

221 | jumppc <= pcout(12 downto 8)&mdrdata;

222 | M5 : mux generic map(13) port map(nextlinepc, jumppc, pcsrc, pcin);

223 |

224 | M6 : mux generic map(8) port map(accj, mdrdata, alusrc2, aluin2);

225 |

226 | myALU : alu port map(acci, aluin2, cznout(2), aluop, aluout, Z, overflow, C, N);

227 | aluresult <= aluout;

228 |

229 | myDI : DI port map (clk, reset, diwrite, instr1(4 downto 0), diout);

230 |

231 | CZNin <= C&Z&N;

232 | myCZN : CZN port map(clk, cznwrite, cznin, cznout);

233 |

234 | end rtl;

235 |

236 |

--------------------------------------------------------------------------------

/IR.vhd:

--------------------------------------------------------------------------------

1 | ----------------------------------------------------------------------------------

2 | -- Company:

3 | -- Engineer:

4 | --

5 | -- Create Date: 15:54:54 06/25/2017

6 | -- Design Name:

7 | -- Module Name: IR - Behavioral

8 | -- Project Name:

9 | -- Target Devices:

10 | -- Tool versions:

11 | -- Description:

12 | --

13 | -- Dependencies:

14 | --

15 | -- Revision:

16 | -- Revision 0.01 - File Created

17 | -- Additional Comments:

18 | --

19 | ----------------------------------------------------------------------------------

20 | LIBRARY IEEE;

21 | USE IEEE.std_logic_1164.ALL;

22 | USE IEEE.numeric_std.ALL;

23 | -- use package

24 | --USE work.procmem_definitions.ALL;

25 |

26 | ENTITY IR IS

27 | generic (width : natural :=8);

28 | PORT (

29 | clk : IN STD_LOGIC; -- clock signal

30 | rst_n : IN STD_LOGIC; -- reset signal

31 | memdata : IN STD_LOGIC_VECTOR(width-1 DOWNTO 0); -- memoryData stored into the IR

32 | IRWrite : IN STD_LOGIC;

33 | instr : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

34 | );

35 | END IR;

36 |

37 | ARCHITECTURE behave OF IR IS

38 | BEGIN

39 |

40 | proc_instreg : PROCESS(clk, rst_n)

41 | BEGIN

42 | IF rst_n = '0' THEN

43 | instr <= (OTHERS => '0');

44 | ELSIF RISING_EDGE(clk) THEN

45 | -- write the output of the memory into the instruction register

46 | IF(IRWrite = '1') THEN

47 | instr <= memdata;

48 | END IF;

49 | END IF;

50 | END PROCESS;

51 |

52 | END behave;

53 |

54 |

--------------------------------------------------------------------------------

/LICENSE:

--------------------------------------------------------------------------------

1 | MIT License

2 |

3 | Copyright (c) 2018 alireza kavian

4 |

5 | Permission is hereby granted, free of charge, to any person obtaining a copy

6 | of this software and associated documentation files (the "Software"), to deal

7 | in the Software without restriction, including without limitation the rights

8 | to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

9 | copies of the Software, and to permit persons to whom the Software is

10 | furnished to do so, subject to the following conditions:

11 |

12 | The above copyright notice and this permission notice shall be included in all

13 | copies or substantial portions of the Software.

14 |

15 | THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

16 | IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

17 | FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

18 | AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

19 | LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

20 | OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE

21 | SOFTWARE.

22 |

--------------------------------------------------------------------------------

/MDR.vhd:

--------------------------------------------------------------------------------

1 | ----------------------------------------------------------------------------------

2 | -- Company:

3 | -- Engineer:

4 | --

5 | -- Create Date: 16:58:39 06/25/2017

6 | -- Design Name:

7 | -- Module Name: MDR - Behavioral

8 | -- Project Name:

9 | -- Target Devices:

10 | -- Tool versions:

11 | -- Description:

12 | --

13 | -- Dependencies:

14 | --

15 | -- Revision:

16 | -- Revision 0.01 - File Created

17 | -- Additional Comments:

18 | --

19 | ----------------------------------------------------------------------------------

20 | LIBRARY IEEE;

21 | USE IEEE.std_logic_1164.ALL;

22 | USE IEEE.numeric_std.ALL;

23 |

24 |

25 | ENTITY MDR IS

26 | generic (width : natural :=8);

27 | PORT (

28 | clk : IN STD_LOGIC; -- clock signal

29 | rst_n : IN STD_LOGIC; -- reset signal

30 | memdata : IN STD_LOGIC_VECTOR(width-1 DOWNTO 0); -- memoryData stored into the IR

31 | dataOut : OUT STD_LOGIC_VECTOR(width-1 DOWNTO 0)

32 | );

33 | END MDR;

34 |

35 | ARCHITECTURE behave OF MDR IS

36 | BEGIN

37 |

38 | proc_instreg : PROCESS(clk, rst_n)

39 | BEGIN

40 | IF rst_n = '0' THEN

41 | dataOut <= (OTHERS => '0');

42 | ELSIF RISING_EDGE(clk) THEN

43 | dataOut <= memdata;

44 | END IF;

45 | END PROCESS;

46 |

47 | END behave;

48 |

49 |

--------------------------------------------------------------------------------

/MEM.vhd:

--------------------------------------------------------------------------------

1 | ----------------------------------------------------------------------------------

2 | -- Company:

3 | -- Engineer:

4 | --

5 | -- Create Date: 14:44:30 06/25/2017

6 | -- Design Name:

7 | -- Module Name: MEM - Behavioral

8 | -- Project Name:

9 | -- Target Devices:

10 | -- Tool versions:

11 | -- Description:

12 | --

13 | -- Dependencies:

14 | --

15 | -- Revision:

16 | -- Revision 0.01 - File Created

17 | -- Additional Comments:

18 | --

19 | ----------------------------------------------------------------------------------

20 | library IEEE;

21 | use IEEE.STD_LOGIC_1164.all;

22 | use IEEE.Numeric_Std.all;

23 |

24 | entity MEM is

25 | port (

26 | clock : in std_logic;

27 | rst_n : in std_logic;

28 | we : in std_logic;

29 | address : in std_logic_vector(12 downto 0);

30 | datain : in std_logic_vector(7 downto 0);

31 | dataout : out std_logic_vector(7 downto 0)

32 | );

33 | end entity MEM;

34 |

35 | architecture behave of MEM is

36 |

37 | type ram_type is array (0 to (2**13)-1) of std_logic_vector(7 downto 0);

38 | signal ram : ram_type := (0 => "10000000", --(arithmetic opcode:4)(Acj:2)->(Aci:2); //overall 8bits

39 | 1 => "10000100",

40 | 2 => "10010100",

41 | 3 => "10110100",

42 | 4 => "10000011",

43 | 5 => "11111000",

44 |

45 | 6 => "00100000", --instr. STA (store addressed)

46 | 7 => "00001111",

47 |

48 | 8 => "01000000", --instr. ADA (add addressed)

49 | 9 => "00001111",

50 |

51 | 10 => "11000000", --instr. JMP ( here : jump to mem(8) )

52 | 11 => "00001100",

53 |

54 | 12 => "00001000", --for jumping to this address (here : pc[12:8]&"00001000")

55 |

56 | others => "10000000"

57 | );

58 | signal read_address : std_logic_vector(12 downto 0);

59 |

60 | begin

61 |

62 | RamProc: process(clock, rst_n) is

63 |

64 | begin

65 | if rising_edge(clock) then

66 | if we = '1' then

67 | ram(to_integer(unsigned(address))) <= datain;

68 | end if;

69 | end if;

70 | end process RamProc;

71 | read_address <= address;

72 | dataout <= ram(to_integer(unsigned(read_address)));

73 |

74 | end architecture behave;

75 |

76 |

77 |

78 |

79 |

80 |

81 |

82 |

--------------------------------------------------------------------------------

/Main.vhd:

--------------------------------------------------------------------------------

1 | ----------------------------------------------------------------------------------

2 | -- Company:

3 | -- Engineer:

4 | --

5 | -- Create Date: 20:18:28 06/25/2017

6 | -- Design Name:

7 | -- Module Name: Main - Behavioral

8 | -- Project Name:

9 | -- Target Devices:

10 | -- Tool versions:

11 | -- Description:

12 | --

13 | -- Dependencies:

14 | --

15 | -- Revision:

16 | -- Revision 0.01 - File Created

17 | -- Additional Comments:

18 | --

19 | ----------------------------------------------------------------------------------

20 | library IEEE;

21 | use IEEE.STD_LOGIC_1164.ALL;

22 |

23 | -- Uncomment the following library declaration if using

24 | -- arithmetic functions with Signed or Unsigned values

25 | use IEEE.NUMERIC_STD.ALL;

26 |

27 | -- Uncomment the following library declaration if instantiating

28 | -- any Xilinx primitives in this code.

29 | --library UNISIM;

30 | --use UNISIM.VComponents.all;

31 |

32 | entity Main is

33 | port( clk : in std_logic;

34 | reset : in std_logic;

35 | op : out std_logic_vector(3 downto 0);

36 | memorydata : out std_logic_vector(7 downto 0);

37 | aluResult : out std_logic_vector(7 downto 0);

38 | controlWord : out std_logic_vector(18 downto 0);

39 | nextline :out std_logic_vector(3 downto 0);

40 | carout :out std_logic_vector(3 downto 0)

41 |

42 | );

43 | end Main;

44 |

45 | architecture Behavioral of Main is

46 |

47 | component Controller is

48 | port( clk, reset: in std_logic;

49 | opcode: in std_logic_vector(3 downto 0);

50 | pcSrc, pcWrite, pcWriteCond, IorD, MemWrite, IRWrite1, IRWrite2, MUXR1,

51 | RegDST, MemToReg, RegWrite, AluSrc2, DIWrite, CZNWrite : out std_logic;

52 | AluOp : out std_logic_vector(2 downto 0);

53 | controlmemData : out std_logic_vector(18 downto 0);

54 | nxtline :out std_logic_vector(3 downto 0);

55 | cardata : out std_logic_vector(3 downto 0)

56 |

57 | );

58 | end component;

59 |

60 | component DataPath is

61 | port(

62 | clk : in std_logic;

63 | reset : in std_logic;

64 | pcSrc, pcWrite, pcWriteCond, IorD, MemWrite, IRWrite1, IRWrite2, MUXR1,

65 | RegDST, MemToReg, RegWrite, AluSrc2, DIWrite, CZNWrite : in std_logic;

66 | AluOp : in std_logic_vector(2 downto 0);

67 | opcode : out std_logic_vector(3 downto 0);

68 | memorydata : out std_logic_vector(7 downto 0);

69 | aluResult : out std_logic_vector(7 downto 0)

70 | );

71 | end component;

72 |

73 | signal opcode : std_logic_vector(3 downto 0);

74 | signal pcSrc, pcWrite, pcWriteCond, IorD, MemWrite, IRWrite1, IRWrite2, MUXR1,

75 | RegDST, MemToReg, RegWrite, AluSrc2, DIWrite, CZNWrite : std_logic;

76 | signal aluop : std_logic_vector(2 downto 0);

77 | begin

78 |

79 | DP : DataPath port map (clk, reset, pcSrc, pcWrite, pcWriteCond, IorD, MemWrite, IRWrite1, IRWrite2, MUXR1,

80 | RegDST, MemToReg, RegWrite, AluSrc2, DIWrite, CZNWrite, AluOp, opcode, memorydata, aluresult);

81 |

82 | C: Controller port map(clk, reset, opcode, pcSrc, pcWrite, pcWriteCond, IorD, MemWrite, IRWrite1, IRWrite2, MUXR1,

83 | RegDST, MemToReg, RegWrite, AluSrc2, DIWrite, CZNWrite, AluOp, controlword, nextline, carout);

84 |

85 |

86 | op <= opcode;

87 |

88 | end Behavioral;

89 |

90 |

--------------------------------------------------------------------------------

/MyCPU.pdf:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/alirezakay/RISC-CPU/19938044c979447709dcb8e72170ca0900fb8465/MyCPU.pdf

--------------------------------------------------------------------------------

/PC.vhd:

--------------------------------------------------------------------------------

1 | ----------------------------------------------------------------------------------

2 | -- Company:

3 | -- Engineer:

4 | --

5 | -- Create Date: 13:38:20 06/25/2017

6 | -- Design Name:

7 | -- Module Name: PC - Behavioral

8 | -- Project Name:

9 | -- Target Devices:

10 | -- Tool versions:

11 | -- Description:

12 | --

13 | -- Dependencies:

14 | --

15 | -- Revision:

16 | -- Revision 0.01 - File Created

17 | -- Additional Comments:

18 | --

19 | ----------------------------------------------------------------------------------

20 | LIBRARY IEEE;

21 | USE IEEE.std_logic_1164.ALL;

22 | USE IEEE.numeric_std.ALL;

23 |

24 | -- use package

25 | --USE work.procmem_definitions.ALL;

26 |

27 | ENTITY pc IS

28 | generic(width: natural := 13);

29 | PORT (

30 | clk : IN STD_LOGIC;

31 | rst_n : IN STD_LOGIC;

32 | pc_in : IN STD_LOGIC_VECTOR(width-1 DOWNTO 0);

33 | PC_en : IN STD_LOGIC;

34 | pc_out : OUT STD_LOGIC_VECTOR(width-1 DOWNTO 0)

35 | );

36 | END pc;

37 |

38 |

39 | ARCHITECTURE behave OF pc IS

40 | BEGIN

41 | proc_pc : PROCESS(clk, rst_n)

42 |

43 | VARIABLE pc_temp : STD_LOGIC_VECTOR(width-1 DOWNTO 0);

44 | BEGIN

45 |

46 | IF rst_n = '0' THEN

47 | pc_temp := (OTHERS => '0');

48 | ELSIF RISING_EDGE(clk) THEN

49 | IF PC_en = '1' THEN

50 | pc_temp := pc_in;

51 | END IF;

52 | END IF;

53 | pc_out <= pc_temp;

54 |

55 | END PROCESS;

56 |

57 | END behave;

58 |

59 |

--------------------------------------------------------------------------------

/README.md:

--------------------------------------------------------------------------------

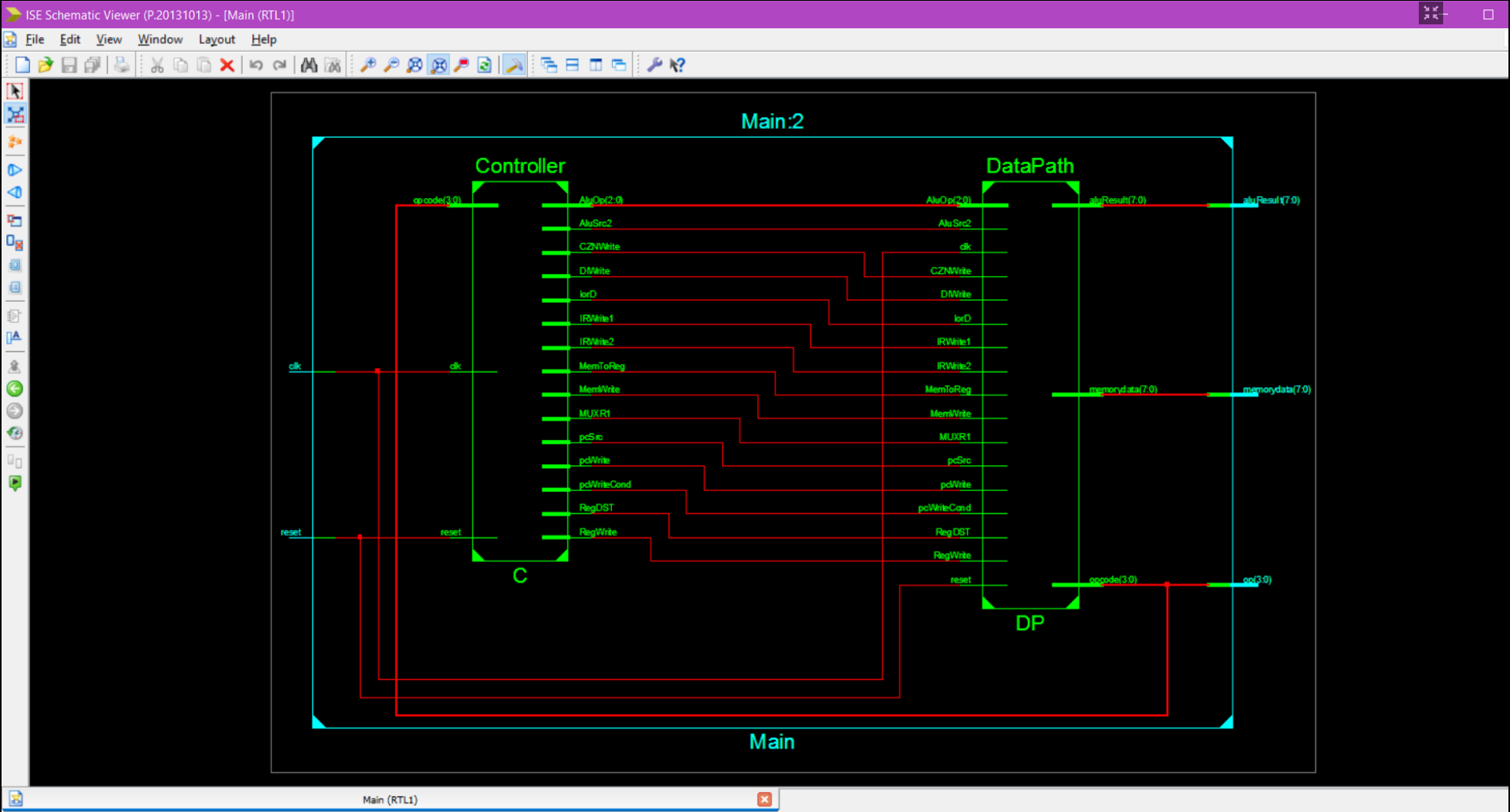

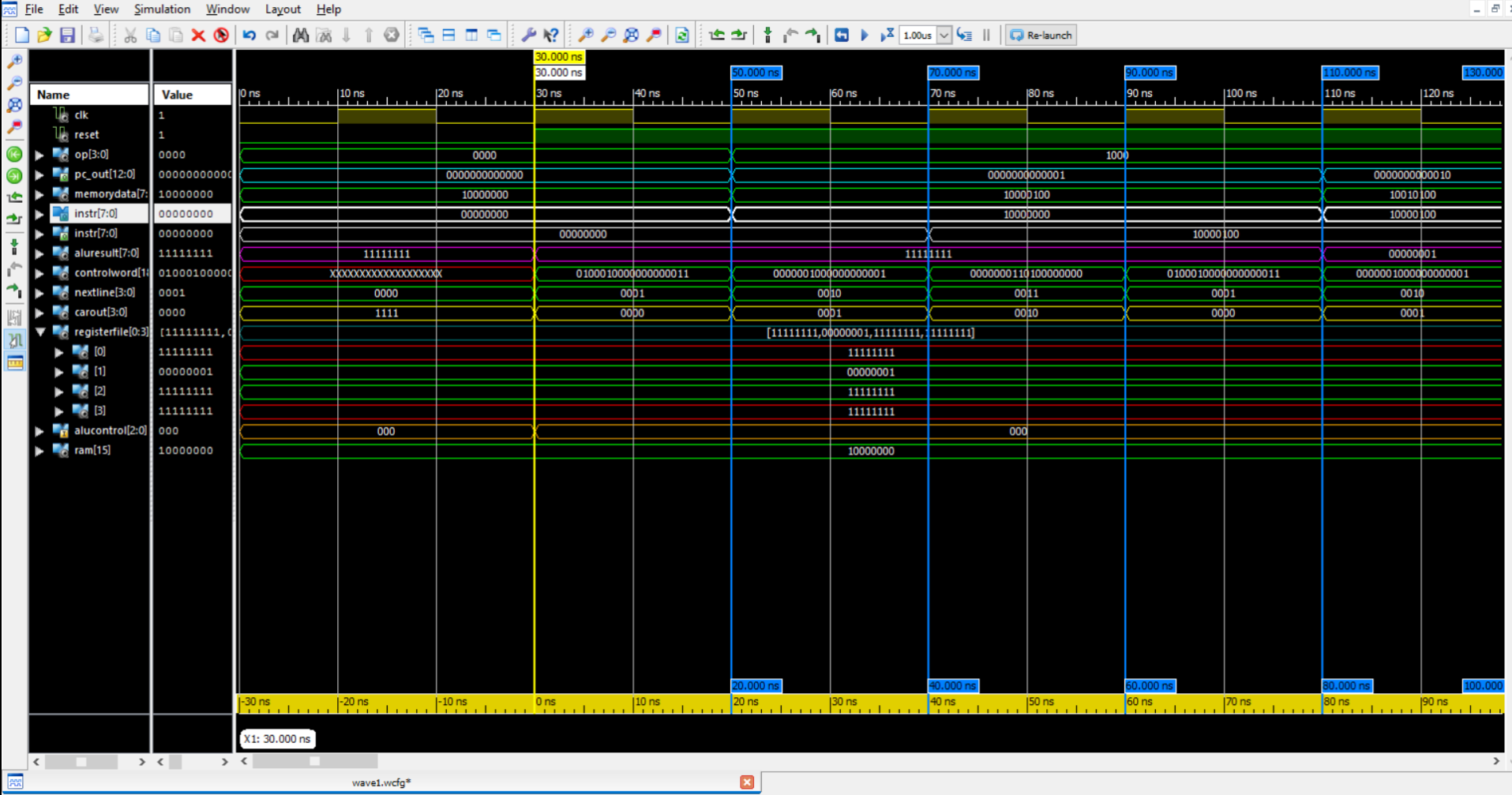

1 | # RISC-CPU

2 | > A multi-cycle RISC CPU (processor) like MIPS-CPU architecture in VHDL ( a hardware-side implementation )

3 |

4 | ## Documentation

5 | This project is implemented in `VHDL` language with `ISE` simulator software with **a particular specifications**.

6 |

7 | Relevant course for this project could be `computer architecture`.

8 |

9 | These codes here in github, are just the vhdl and wave files.

10 |

11 | If you wanna get the ***complete project codes, built with `ISE`*** go [here](https://alirezakay.github.io/showcase/y2/risc-cpu-simulation), find the project title and **download** the full one.

12 |

13 | here is a fairly complete documentaion written in **Persian** and also **English** languages: [document](./MyCPU.pdf)

14 |

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 | ## Authors

24 |

25 | [Alireza Kavian](https://alireza-kavian.github.io)

26 |

27 | ## License

28 |

29 | This project is licensed under the MIT License - see the [LICENSE](./LICENSE) file for details

30 |

31 |

--------------------------------------------------------------------------------

/ROM1.vhd:

--------------------------------------------------------------------------------

1 | ----------------------------------------------------------------------------------

2 | -- Company:

3 | -- Engineer:

4 | --

5 | -- Create Date: 20:19:48 06/25/2017

6 | -- Design Name:

7 | -- Module Name: ROM - Behavioral

8 | -- Project Name:

9 | -- Target Devices:

10 | -- Tool versions:

11 | -- Description:

12 | --

13 | -- Dependencies:

14 | --

15 | -- Revision:

16 | -- Revision 0.01 - File Created

17 | -- Additional Comments:

18 | --

19 | ----------------------------------------------------------------------------------

20 | library IEEE;

21 | use IEEE.STD_LOGIC_1164.ALL;

22 |

23 | -- Uncomment the following library declaration if using

24 | -- arithmetic functions with Signed or Unsigned values

25 | use IEEE.NUMERIC_STD.ALL;

26 |

27 | -- Uncomment the following library declaration if instantiating

28 | -- any Xilinx primitives in this code.

29 | --library UNISIM;

30 | --use UNISIM.VComponents.all;

31 |

32 | entity ROM1 is

33 | port(

34 | opcode: in std_logic_vector(3 downto 0);

35 | lineNumber: out std_logic_vector(3 downto 0)

36 | );

37 | end ROM1;

38 |

39 | architecture Behavioral of ROM1 is

40 | signal op_3_2 : std_logic_vector(1 downto 0);

41 | begin

42 |

43 | op_3_2 <= opcode(3 downto 2);

44 | process (opcode, op_3_2)

45 | begin

46 | case op_3_2 is

47 | when "10" =>

48 | case opcode(3 downto 0) is

49 | when "1000" => lineNumber <="0010";

50 | when "1001" => lineNumber <="0011";

51 | when "1010" => lineNumber <="0100";

52 | when "1011" => lineNumber <="0101";

53 | when others => lineNumber <="0000";

54 | end case;

55 | when others =>

56 | case opcode(3 downto 1) is

57 | when "111" => lineNumber <="0110";

58 | when "110" => lineNumber <="0111";

59 | when "000" => lineNumber <="0111";

60 | when "001" => lineNumber <="1010";

61 | when "010" => lineNumber <="0111";

62 | when "011" => lineNumber <="0111";

63 | when others => lineNumber <="0000";

64 | end case;

65 | end case;

66 | end process;

67 |

68 |

69 | end Behavioral;

70 |

71 |

--------------------------------------------------------------------------------

/ROM2.vhd:

--------------------------------------------------------------------------------

1 | ----------------------------------------------------------------------------------

2 | -- Company:

3 | -- Engineer:

4 | --

5 | -- Create Date: 20:19:48 06/25/2017

6 | -- Design Name:

7 | -- Module Name: ROM - Behavioral

8 | -- Project Name:

9 | -- Target Devices:

10 | -- Tool versions:

11 | -- Description:

12 | --

13 | -- Dependencies:

14 | --

15 | -- Revision:

16 | -- Revision 0.01 - File Created

17 | -- Additional Comments:

18 | --

19 | ----------------------------------------------------------------------------------

20 | library IEEE;

21 | use IEEE.STD_LOGIC_1164.ALL;

22 |

23 | -- Uncomment the following library declaration if using

24 | -- arithmetic functions with Signed or Unsigned values

25 | use IEEE.NUMERIC_STD.ALL;

26 |

27 | -- Uncomment the following library declaration if instantiating

28 | -- any Xilinx primitives in this code.

29 | --library UNISIM;

30 | --use UNISIM.VComponents.all;

31 |

32 | entity ROM2 is

33 | port(

34 | opcode: in std_logic_vector(2 downto 0);

35 | lineNumber: out std_logic_vector(3 downto 0)

36 | );

37 | end ROM2;

38 |

39 | architecture Behavioral of ROM2 is

40 |

41 | begin

42 |

43 | with opcode select lineNumber <=

44 | "1000" when "110",

45 | "1001" when "000",

46 | "1011" when "010",

47 | "1100" when "011",

48 | "0000" when others;

49 |

50 | end Behavioral;

51 |

52 |

--------------------------------------------------------------------------------

/RegFile.vhd:

--------------------------------------------------------------------------------

1 | ----------------------------------------------------------------------------------

2 | -- Company:

3 | -- Engineer:

4 | --

5 | -- Create Date: 16:41:15 06/25/2017

6 | -- Design Name:

7 | -- Module Name: RegFile - Behavioral

8 | -- Project Name:

9 | -- Target Devices:

10 | -- Tool versions:

11 | -- Description:

12 | --

13 | -- Dependencies:

14 | --

15 | -- Revision:

16 | -- Revision 0.01 - File Created

17 | -- Additional Comments:

18 | --

19 | ----------------------------------------------------------------------------------

20 | LIBRARY IEEE;

21 | USE IEEE.std_logic_1164.ALL;

22 | USE IEEE.numeric_std.ALL;

23 | -- use package

24 | --USE work.procmem_definitions.ALL;

25 |

26 |

27 | ENTITY regfile IS

28 | GENERIC ( width : natural := 8; --data width

29 | regfile_depth : positive := 4; --number of accumulator registers

30 | regfile_adrsize : positive := 2 --address size for addressing acc. registers

31 | );

32 | PORT (clk,rst_n : IN std_logic;

33 | RegWrite : IN std_logic; -- write control

34 | writeport : IN std_logic_vector(width-1 DOWNTO 0); -- register input

35 | adrwport : IN std_logic_vector(regfile_adrsize-1 DOWNTO 0);-- address write

36 | adrport0 : IN std_logic_vector(regfile_adrsize-1 DOWNTO 0);-- address port 0

37 | adrport1 : IN std_logic_vector(regfile_adrsize-1 DOWNTO 0);-- address port 1

38 | readport0 : OUT std_logic_vector(width-1 DOWNTO 0); -- output port 0

39 | readport1 : OUT std_logic_vector(width-1 DOWNTO 0) -- output port 1

40 | --r0 : OUT std_logic_vector(width-1 DOWNTO 0);

41 | --r1 : OUT std_logic_vector(width-1 DOWNTO 0);

42 | --r2 : OUT std_logic_vector(width-1 DOWNTO 0);

43 | --r3 : OUT std_logic_vector(width-1 DOWNTO 0)

44 | );

45 |

46 | END regfile;

47 |

48 |

49 | ARCHITECTURE behave OF regfile IS

50 |

51 | SUBTYPE WordT IS std_logic_vector(width-1 DOWNTO 0); -- reg word TYPE

52 | TYPE StorageT IS ARRAY(0 TO regfile_depth-1) OF WordT; -- reg array TYPE

53 | SIGNAL registerfile : StorageT; -- reg file contents

54 |

55 | BEGIN

56 | -- perform write operation

57 | PROCESS(rst_n, clk)

58 | BEGIN

59 | IF rst_n = '0' THEN

60 | FOR i IN 0 TO regfile_depth-1 LOOP

61 | registerfile(i) <= (OTHERS => '0');

62 | END LOOP;

63 | registerfile(1) <= "00000001";

64 |

65 | ELSIF rising_edge(clk) THEN

66 | IF RegWrite = '1' THEN

67 | registerfile(to_integer(unsigned(adrwport))) <= writeport;

68 | END IF;

69 | END IF;

70 | END PROCESS;

71 | -- perform reading ports

72 | readport0 <= registerfile(to_integer(unsigned(adrport0)));

73 | readport1 <= registerfile(to_integer(unsigned(adrport1)));

74 |

75 | --r0 <= registerfile(0);

76 | --r1 <= registerfile(1);

77 | --r2 <= registerfile(2);

78 | --r3 <= registerfile(3);

79 |

80 | END behave;

81 |

82 |

--------------------------------------------------------------------------------

/_config.yml:

--------------------------------------------------------------------------------

1 | plugins:

2 | - jekyll-seo-tag

3 |

--------------------------------------------------------------------------------

/adder.vhd:

--------------------------------------------------------------------------------

1 | library ieee;

2 | use ieee.std_logic_1164.all;

3 | use ieee.std_logic_unsigned.all;

4 |

5 | Entity adder is

6 | Port (A, B : in std_logic_vector(12 downto 0);

7 | Y : out std_logic_vector(12 downto 0));

8 | End;

9 |

10 | Architecture behave of adder is

11 | begin

12 | Y <= A + B;

13 | end;

14 |

--------------------------------------------------------------------------------

/alu.vhd:

--------------------------------------------------------------------------------

1 | library ieee;

2 | use ieee.std_logic_1164.all;

3 | use ieee.std_logic_unsigned.all;

4 | use ieee.std_logic_arith.all;

5 |

6 | Entity alu is

7 | Generic(W : natural := 8; Cw : natural := 3);

8 | port(SrcA : in std_logic_vector(W-1 downto 0);

9 | SrcB : in std_logic_vector(W-1 downto 0);

10 | Cin : in std_logic;

11 | AluControl : in std_logic_vector(Cw-1 downto 0);

12 | AluResult : out std_logic_vector(W-1 downto 0);

13 | Zero : out std_logic;

14 | Overflow : out std_logic;

15 | CarryOut : out std_logic;

16 | Neg : out std_logic --negative signal

17 | );

18 | End alu;

19 |

20 |

21 | Architecture RTL of alu is

22 |

23 | begin

24 | process (AluControl, srca, srcb, cin)

25 |

26 | Variable Y : std_logic_vector(W downto 0);

27 | Variable Aux : std_logic_vector(2 downto 0);

28 | Variable my_zero : std_logic_vector(W-1 downto 0);

29 | begin

30 | Y := "000000000";

31 | my_zero := "00000000";

32 | Aux := AluControl;

33 |

34 | case Aux is

35 | when "000" => Y := '0' & SrcB; -- returns the second source

36 | when "001" => Y := ('0' & SrcA) + ('0' & SrcB) + ("00000000" & Cin); -- add sources with cin

37 | when "010" => Y := ('0' & SrcA) + ('0' & SrcB); -- add sources lonely

38 | when "011" => Y := '0' & (SrcA - SrcB); -- sub

39 | when "100" => Y := '0' & (SrcA and SrcB); -- and

40 | when "101" => Y := '0' & (SrcA or SrcB); -- or

41 | when "111" =>

42 | if (SrcA < SrcB) then

43 | Y := "000000001";

44 | else

45 | Y := Y;

46 | end if;

47 | when others => NULL;

48 | end case;

49 |

50 | --Check if it was Negative

51 | if Y < 0 then

52 | Neg <= '1';

53 | else

54 | Neg <= '0';

55 | end if;

56 |

57 | -- Check if it was Zero

58 | if Y = 0 then

59 | Zero <= '1';

60 | else

61 | Zero <= '0';

62 | end if;

63 |

64 | -- Check if there was overflow

65 | if ((SrcA > my_zero AND SrcB > my_zero)

66 | AND (Y < ('0' & my_zero))) OR ((SrcA < my_zero AND SrcB < my_zero) AND (Y > ('0' & my_zero))) then

67 | Overflow <= '1';

68 | else

69 | Overflow <= '0';

70 | end if;

71 |

72 | -- Check if there was CarryOut

73 | if Y(8) = '1' then

74 | CarryOut <= '1';

75 | else

76 | CarryOut <= '0';

77 | end if;

78 |

79 | -- Final Result

80 | AluResult <= Y(7 downto 0);

81 | end process;

82 | end RTL;

83 |

--------------------------------------------------------------------------------

/mux.vhd:

--------------------------------------------------------------------------------

1 | library ieee;

2 | use ieee.std_logic_1164.all;

3 |

4 | Entity mux is

5 | Generic(W : integer);

6 | Port (D0, D1 : in std_logic_vector(W-1 downto 0);

7 | S : in std_logic;

8 | Y : out std_logic_vector(W-1 downto 0));

9 | End;

10 |

11 | Architecture behave of mux is

12 | begin

13 | y <= D0 when S = '0' else D1;

14 | end;

15 |

--------------------------------------------------------------------------------

/mux_2bits.vhd:

--------------------------------------------------------------------------------

1 | ----------------------------------------------------------------------------------

2 | -- Company:

3 | -- Engineer:

4 | --

5 | -- Create Date: 21:26:04 06/25/2017

6 | -- Design Name:

7 | -- Module Name: mux_4bits - Behavioral

8 | -- Project Name:

9 | -- Target Devices:

10 | -- Tool versions:

11 | -- Description:

12 | --

13 | -- Dependencies:

14 | --

15 | -- Revision:

16 | -- Revision 0.01 - File Created

17 | -- Additional Comments:

18 | --

19 | ----------------------------------------------------------------------------------

20 | library IEEE;

21 | use IEEE.STD_LOGIC_1164.ALL;

22 |

23 | -- Uncomment the following library declaration if using

24 | -- arithmetic functions with Signed or Unsigned values

25 | --use IEEE.NUMERIC_STD.ALL;

26 |

27 | -- Uncomment the following library declaration if instantiating

28 | -- any Xilinx primitives in this code.

29 | --library UNISIM;

30 | --use UNISIM.VComponents.all;

31 | Entity mux_2bits is

32 | Generic(W : integer);

33 | Port (D0, D1, D2, D3 : in std_logic_vector(W-1 downto 0);

34 | S : in std_logic_vector(1 downto 0);

35 | Y : out std_logic_vector(W-1 downto 0));

36 | End;

37 |

38 | Architecture behave of mux_2bits is

39 | begin

40 | y <= D0 when S = "00" else

41 | D1 when S = "01" else

42 | D2 when S = "10" else D3;

43 | end;

44 |

45 |

--------------------------------------------------------------------------------

/wave1.wcfg:

--------------------------------------------------------------------------------

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

25 |

26 |

27 |

28 |

29 |

30 |

31 |

32 |

33 |

34 |

35 | clk

36 | clk

37 | true

38 | #ffff00

39 |

40 |

41 | reset

42 | reset

43 |

44 |

45 | op[3:0]

46 | op[3:0]

47 |

48 |

49 | pc_out[12:0]

50 | pc_out[12:0]

51 | true

52 | #00ffff

53 |

54 |

55 | memorydata[7:0]

56 | memorydata[7:0]

57 |

58 |

59 | instr[7:0]

60 | instr[7:0]

61 | true

62 | #ffffff

63 |

64 |

65 | instr[7:0]

66 | instr[7:0]

67 | true

68 | #ffffff

69 |

70 |

71 | aluresult[7:0]

72 | aluresult[7:0]

73 | true

74 | #ff00ff

75 |

76 |

77 | controlword[18:0]

78 | controlword[18:0]

79 |

80 |

81 | nextline[3:0]

82 | nextline[3:0]

83 |

84 |

85 | carout[3:0]

86 | carout[3:0]

87 | true

88 | #ffff00

89 |

90 |

91 | label

92 | registerfile[0:3]

93 | registerfile[0:3]

94 | registerfile[0:3]

95 | true

96 | #008080

97 |

98 | label

99 | [0]

100 | registerfile[0]

101 | [0]

102 | true

103 | #ff0000

104 |

105 |

106 | [1]

107 | registerfile[1]

108 |

109 |

110 | [2]

111 | registerfile[2]

112 |

113 |

114 | [3]

115 | registerfile[3]

116 | true

117 | #ff0000

118 |

119 |

120 |

121 | alucontrol[2:0]

122 | alucontrol[2:0]

123 | true

124 | #ffaa00

125 |

126 |

127 | [15]

128 | ram[15]

129 |

130 |

131 |

--------------------------------------------------------------------------------