├── LICENSE

├── README.md

├── c64-rom

├── .gitignore

├── Makefile

├── bin2c.py

├── loader_rom.asm

├── loader_rom.c

├── loader_rom.h

├── raspi.bmp

├── raspi.c

├── raspi.h

├── raspi.nuf

└── raspi.xcf

├── docs

├── command-sequence.puml

├── command-sequence.svg

├── pcb.jpg

├── read-sequence.puml

├── read-sequence.svg

└── schematic.pdf

├── firmware

├── .gitignore

├── CMakeLists.txt

├── address_decoder.pio

├── c64_pico_ram_interface.c

├── command.pio

├── pico_sdk_import.cmake

└── read.pio

└── pcb

├── .gitignore

├── fp-lib-table

├── gerber

├── picocart-B_Cu.gbl

├── picocart-B_Mask.gbs

├── picocart-B_Paste.gbp

├── picocart-B_Silkscreen.gbo

├── picocart-Edge_Cuts.gm1

├── picocart-F_Cu.gtl

├── picocart-F_Mask.gts

├── picocart-F_Paste.gtp

├── picocart-F_Silkscreen.gto

├── picocart-NPTH-drl_map.gbr

├── picocart-NPTH.drl

├── picocart-PTH-drl_map.gbr

└── picocart-PTH.drl

├── logo.svg

├── picocart.dcm

├── picocart.kicad_pcb

├── picocart.kicad_prl

├── picocart.kicad_pro

├── picocart.kicad_sch

├── picocart.lib

├── picocart.pretty

├── C64ExpansionEdge.kicad_mod

├── C64ExpansionEdgeShort.kicad_mod

├── OS102011MS2Q.kicad_mod

├── RPi_Pico_SMD_TH.kicad_mod

├── RPi_Pico_TH.kicad_mod

├── SOP65P640X110-20N.kicad_mod

├── SOP65P640X120-20N.kicad_mod

├── SOT95P275X110-5N.kicad_mod

└── logo.kicad_mod

└── sym-lib-table

/LICENSE:

--------------------------------------------------------------------------------

1 | BSD 3-Clause License

2 |

3 | Copyright (c) 2022, Kevin Vance

4 |

5 | Redistribution and use in source and binary forms, with or without

6 | modification, are permitted provided that the following conditions are met:

7 |

8 | 1. Redistributions of source code must retain the above copyright notice, this

9 | list of conditions and the following disclaimer.

10 |

11 | 2. Redistributions in binary form must reproduce the above copyright notice,

12 | this list of conditions and the following disclaimer in the documentation

13 | and/or other materials provided with the distribution.

14 |

15 | 3. Neither the name of the copyright holder nor the names of its

16 | contributors may be used to endorse or promote products derived from

17 | this software without specific prior written permission.

18 |

19 | THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

20 | AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE

21 | IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE

22 | DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE

23 | FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL

24 | DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR

25 | SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER

26 | CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY,

27 | OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

28 | OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

29 |

--------------------------------------------------------------------------------

/README.md:

--------------------------------------------------------------------------------

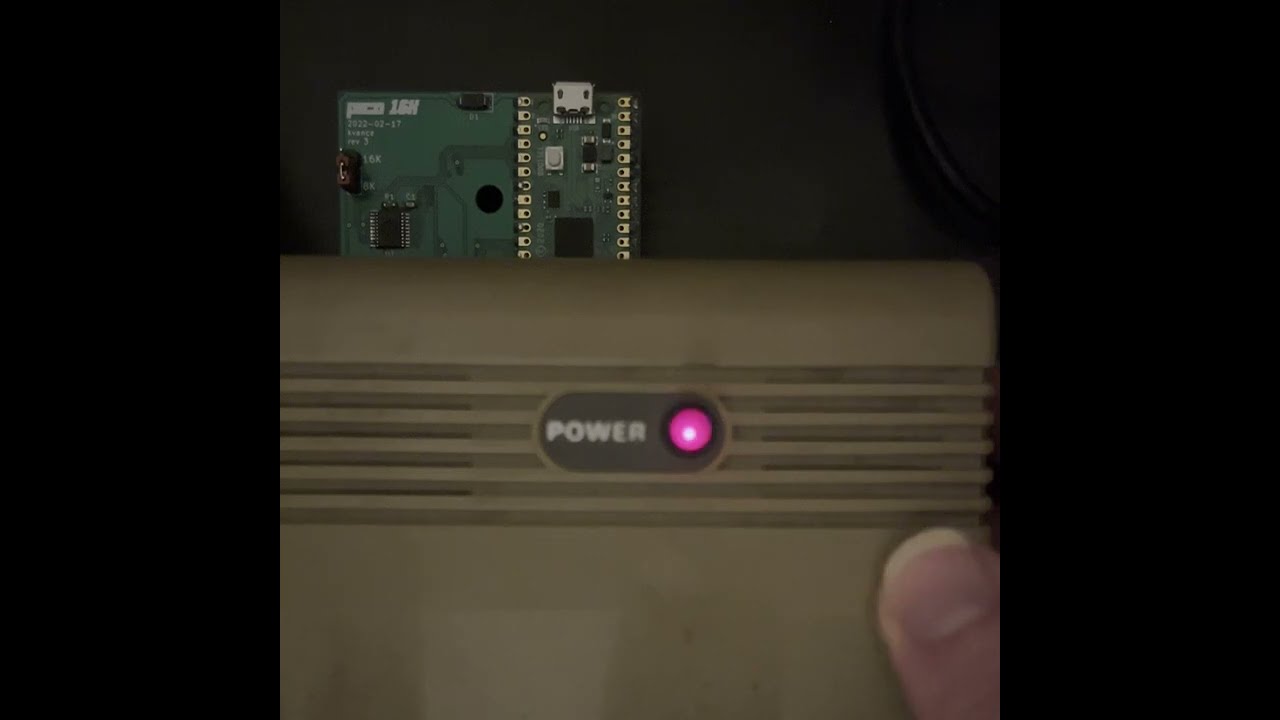

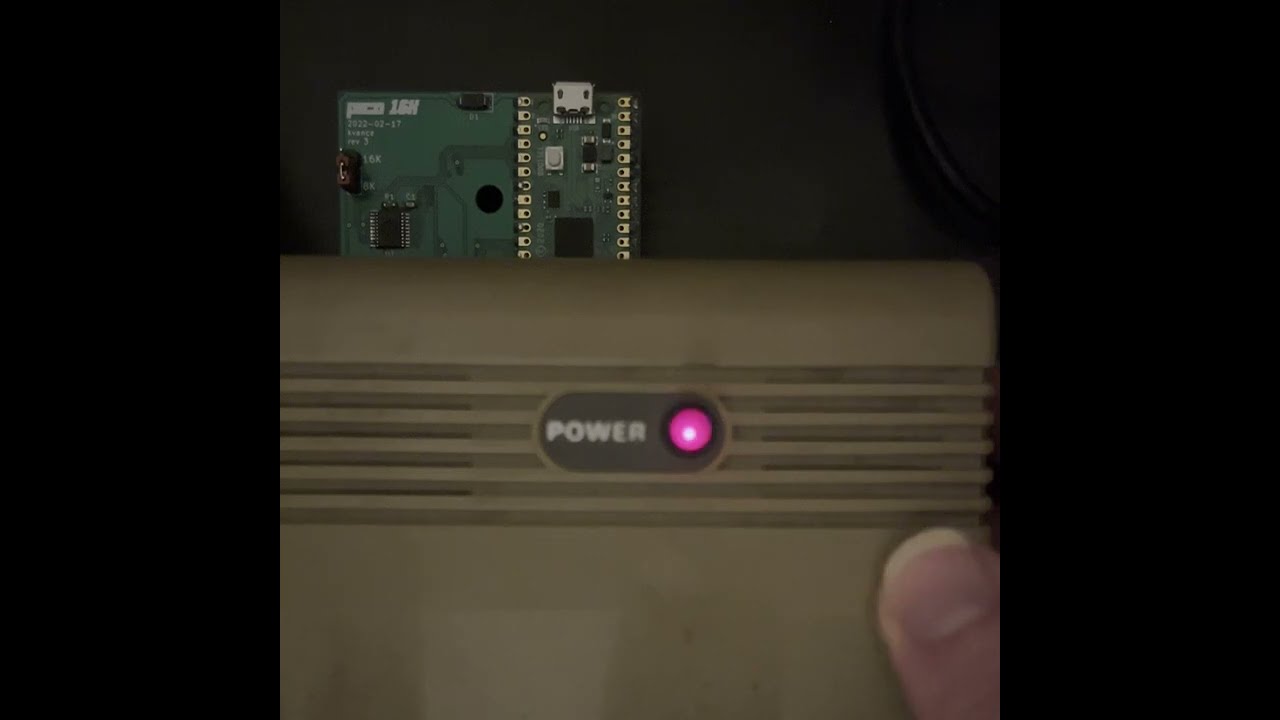

1 | # Commodore 64 to Raspberry Pi Pico RAM interface

2 |

3 | This project exposes a 16 KiB window of a Raspberry Pi Pico's RAM to a Commodore 64 via the

4 | expansion port. It includes a hardware design and software for the Pico C++ SDK.

5 |

6 |

7 | PCB image Demo video

12 |

13 | ## The hardware

14 |

15 | **[Schematic PDF](./docs/schematic.pdf)**

16 |

17 | Schematic, PCB, and project files are in KiCad 6 format.

18 |

19 | 5V power from the expansion port is used to power the Pico. As suggested in the Pico datasheet,

20 | a Schottky diode allows the Pico to be connected to powered USB at the same time.

21 |

22 | 8-bit buffers bring the 5V logic levels on the address and data bus down to 3.3V to protect

23 | the Pico's GPIO pins. This means that when the C64 reads from the Pico, it's putting a 3.3V

24 | signal on the data bus. At TTL logic levels, this should be fine.

25 |

26 | A switch allows you to toggle between an 8K ROM and a 16K ROM by pulling the /GAME line low.

27 | This loses half the address space, but lets you boot into BASIC.

28 |

29 | The tolerances on the PCB design are compatible with [JLCPCB](https://jlcpcb.com/). I ordered

30 | my prototypes from them with ENIG surface finish and gold fingers on a 1.6mm thick board. You

31 | can get them made much cheaper with HASL, but it will eventually scrape off as you reinsert

32 | the board.

33 |

34 | ## The firmware

35 |

36 | Given a 16 KiB-aligned base address on the Pico's address space, four PIO state machines and

37 | two DMA channels handle reading addresses from the C64 address bus and writing the requested

38 | data to the C64 data bus. The CPU is not needed once this is configured.

39 |

40 | To allow the C64 to communicate with the Pico, a 256 byte **command area** is reserved that

41 | will put that byte onto the RX FIFO for the CPU to consume. The CPU can put any value onto

42 | the TX FIFO to signal that it is ready for more commands.

43 |

44 | Between the GPIO pins and the RAM, there are five logical components:

45 |

46 | - **address_decoder PIO state machine:** monitors the /ROML and /ROMH lines for reads,

47 | checks if the address is for the special **command area**, and wakes up either the **read**

48 | or **command** state machines as needed. Two copies of this state machine run at the same

49 | time, monitoring /ROML and /ROMH.

50 | - **read PIO state machine:** reads the address lines, sends the address to DMA, and writes

51 | the returned data to the data bus

52 | - **command PIO state machine:** reads the low 8 bits of the address, and copies it to the

53 | RX FIFO for the CPU to handle. It writes the STATUS register back to the data bus, indicating

54 | if the CPU is busy or not. The CPU can indicate its readiness by writing any value to the TX FIFO.

55 |

56 | The special value `00` will not be sent to the CPU at all, allowing the C64 to poll the status

57 | register until the Pico is finished processing a command.

58 | - **DMA channel 1**: write the incoming address to the configuration of DMA channel 2, triggering

59 | a read

60 | - **DMA channel 2**: copy a byte at the requested RAM address to the read PIO state machine

61 |

62 |

63 |

64 |

65 |

66 | It's a Rube Goldberg machine, but the Pico's PIO controllers and DMA can do this in well under

67 | the time required by the C64's CPU.

68 |

69 |

70 | ## Further improvements

71 |

72 | ### Could this work as a 16K ROM and IO ports?

73 |

74 | Maybe, but this design is already using all the GPIO pins on the Pico. Even if you replace

75 | the "input enable" pin (you can probably get away without it), you'll also need to monitor

76 | PHI2. In my experience, the IO lines are glitchy and you need to make sure that you're actually

77 | in the right part of the clock cycle to use them.

78 |

79 | You could try using a shift register to free up a bunch of pins, but you'll waste a lot of

80 | PIO clock cycles shifting all the bits through it. It might be fast enough to only shift a

81 | couple of bits.

82 |

83 | ### Could I use all 44 KiB of the available address space?

84 |

85 | I think you're definitely in shift register territory at this point, and good luck trying to

86 | decode more than a couple of address prefixes in PIO. If you actually do this, please contact

87 | me because I want to see it!

88 |

89 |

90 | ## Legal

91 |

92 | Distribute under the terms of the BSD 3-clause license.

93 |

94 | The [KiCad-RP-Pico footprint](https://github.com/ncarandini/KiCad-RP-Pico) is by

95 | Nicolò Carandini.

96 |

--------------------------------------------------------------------------------

/c64-rom/.gitignore:

--------------------------------------------------------------------------------

1 | *.bin

2 | *.sym

3 | *.vs

4 |

--------------------------------------------------------------------------------

/c64-rom/Makefile:

--------------------------------------------------------------------------------

1 | CARTCONV = cartconv

2 | KICK_JAR = ${HOME}/opt/KickAssembler/KickAss.jar

3 |

4 | .PHONY: all clean

5 | .SUFFIXES: .asm .bin .crt

6 |

7 | all: loader_rom.c loader_rom.h raspi.c raspi.h

8 |

9 | loader_rom.c: loader_rom.bin

10 | python bin2c.py loader_rom.bin

11 | loader_rom.h: loader_rom.c loader_rom.bin

12 | python bin2c.py loader_rom.bin

13 |

14 | raspi.c: raspi.nuf

15 | python bin2c.py --skip 2 raspi.nuf

16 | raspi.h: raspi.c raspi.nuf

17 | python bin2c.py --skip 2 raspi.nuf

18 |

19 | .bin.crt:

20 | ${CARTCONV} -p -n pico16k -t normal -i $< -o $@

21 |

22 | .asm.bin:

23 | java -jar ${KICK_JAR} $< -vicesymbols

24 |

25 | clean:

26 | rm -f loader_rom.c loader_rom.h loader_rom.bin loader_rom.crt loader_rom.sym loader_rom.vs

27 |

--------------------------------------------------------------------------------

/c64-rom/bin2c.py:

--------------------------------------------------------------------------------

1 | #!/usr/bin/env python

2 | import argparse

3 | import os

4 | import re

5 | import textwrap

6 |

7 | if __name__ != '__main__':

8 | raise RuntimeError('not a module')

9 |

10 | parser = argparse.ArgumentParser(

11 | description='Given file.bin, write file.c and file.h')

12 | parser.add_argument('--skip', metavar='N', default=0, type=int,

13 | help='start N bytes into the source file')

14 | parser.add_argument('input', metavar='file.bin')

15 | args = parser.parse_args()

16 |

17 | size = os.path.getsize(args.input)

18 | basename = os.path.basename(args.input).partition('.')[0]

19 | constname = re.sub(r'[^0-9A-Za-z_]', '', basename.replace('-', '_'))

20 | with open(args.input, 'rb') as inf:

21 | inf.seek(args.skip)

22 | with open(f'{basename}.c', 'wt') as outf:

23 | outf.write(textwrap.dedent(f"""\

24 | #include

25 |

26 | const uint8_t {constname}[{size}] = {{

27 | """))

28 | while True:

29 | data = inf.read(8)

30 | if not data:

31 | break

32 | outf.write('\t')

33 | outf.write(', '.join(f'0x{n:02X}' for n in data))

34 | outf.write(',\n')

35 | outf.write('};\n')

36 |

37 | with open(f'{basename}.h', 'wt') as outf:

38 | outf.write(textwrap.dedent(f"""\

39 | #pragma once

40 |

41 | extern const uint8_t {constname}[{size}];

42 | """))

43 |

--------------------------------------------------------------------------------

/c64-rom/loader_rom.asm:

--------------------------------------------------------------------------------

1 | .file [name="loader_rom.bin", type="bin", segments="Code,CopySource,CommandArea"]

2 |

3 | .label nufli_dest = $2000 // NUFLI destination start

4 | .label nufli_exec = $3000 // NUFLI displayer entry point

5 | .const NUFLI_SIZE = $5a00 // unpacked NUFLI size (size of raspi.bin)

6 | .const NUM_1K_NUFLI_BLOX = floor(NUFLI_SIZE/1024) // number of full 1K NUFLI blocks

7 | // (remainder is not counted)

8 |

9 | //

10 | // Zero-page pointers (used to copy to different offsets into nufli_dest)

11 | //

12 | .label dest_ptr1 = $f8

13 | .label dest_ptr2 = $fa

14 | .label dest_ptr3 = $fc

15 | .label dest_ptr4 = $fe

16 |

17 | //

18 | // 1k window to copy NUFLI from

19 | //

20 | .segmentdef CopySource [min=$8400, max=$87ff]

21 | .label copy_source = $8400

22 |

23 |

24 | //

25 | // 256 byte window to send commands by reading from

26 | //

27 | .segmentdef CommandArea [min=$9e00, max=$9eff]

28 | .label command_area = $9e00

29 | .const CMD_GET_STATUS = 0

30 | .const CMD_NEXT_PAGE = 1

31 |

32 |

33 | .segment Code [start=$8000]

34 |

35 | *=$8000 // cartridge header

36 | .word start // start address

37 | .word start // NMI ISR address

38 | .encoding "petscii_mixed"

39 | .text "CBM80" // cartridge signature

40 | .encoding "screencode_upper"

41 |

42 | start: jsr $ff81 // kernal: initialize VIC-II

43 | jsr $ff84 // kernal: initialize CIA

44 |

45 | // show a black screen while we load the NUFLI data

46 | lda #0

47 | sta $d020 // black border

48 | sta $d021 // black background

49 | lda #' ' // clear with spaces

50 | ldx #0

51 | clear: sta $0400, x

52 | sta $0500, x

53 | sta $0600, x

54 | sta $0700, x

55 | dex

56 | bne clear

57 |

58 | ldx #NUM_1K_NUFLI_BLOX // copy the NUFLI 1 KB at a time

59 | lda #nufli_dest

65 | sta dest_ptr1 + 1

66 | lda #>(nufli_dest + $100)

67 | sta dest_ptr2 + 1

68 | lda #>(nufli_dest + $200)

69 | sta dest_ptr3 + 1

70 | lda #>(nufli_dest + $300)

71 | sta dest_ptr4 + 1

72 |

73 | ldy #0

74 | copy1k: lda command_area + CMD_GET_STATUS

75 | sta $d020 // flash border if the pico's cpu is busy

76 | bne copy1k // loop until status is not busy

77 | lda copy_source, y

78 | sta (dest_ptr1), y

79 | lda copy_source + $100, y

80 | sta (dest_ptr2), y

81 | lda copy_source + $200, y

82 | sta (dest_ptr3), y

83 | lda copy_source + $300, y

84 | sta (dest_ptr4), y

85 | iny

86 | bne copy1k

87 |

88 | lda command_area + CMD_NEXT_PAGE // advance the source window by 1 KB

89 | clc

90 | lda #4 // advance the dest addrs by 1 KB (high byte of #$400)

91 | adc dest_ptr1 + 1

92 | sta dest_ptr1 + 1

93 | lda #4

94 | adc dest_ptr2 + 1

95 | sta dest_ptr2 + 1

96 | lda #4

97 | adc dest_ptr3 + 1

98 | sta dest_ptr3 + 1

99 | lda #4

100 | adc dest_ptr4 + 1

101 | sta dest_ptr4 + 1

102 |

103 | dex // loop copying whole KBs

104 | bne copy1k

105 |

106 | // copy the remaining data 256 bytes at a time

107 | // (could be optimized by trying 768 at a time, then 512, then up to 256)

108 | ldx #0

109 | .const BYTES_LEFT = NUFLI_SIZE & $03ff

110 | .for(var i = 0; i < BYTES_LEFT; i += 256) {

111 | .if (BYTES_LEFT - i < 256) {

112 | ldx #(BYTES_LEFT - i)

113 | }

114 | copy: lda copy_source + i, x

115 | sta nufli_dest + NUM_1K_NUFLI_BLOX*1024 + i, x

116 | inx

117 | bne copy

118 | }

119 | jmp nufli_exec // Finished copying! Execute!

120 |

--------------------------------------------------------------------------------

/c64-rom/loader_rom.c:

--------------------------------------------------------------------------------

1 | #include

2 |

3 | const uint8_t loader_rom[157] = {

4 | 0x09, 0x80, 0x09, 0x80, 0xC3, 0xC2, 0xCD, 0x38,

5 | 0x30, 0x20, 0x81, 0xFF, 0x20, 0x84, 0xFF, 0xA9,

6 | 0x00, 0x8D, 0x20, 0xD0, 0x8D, 0x21, 0xD0, 0xA9,

7 | 0x20, 0xA2, 0x00, 0x9D, 0x00, 0x04, 0x9D, 0x00,

8 | 0x05, 0x9D, 0x00, 0x06, 0x9D, 0x00, 0x07, 0xCA,

9 | 0xD0, 0xF1, 0xA2, 0x16, 0xA9, 0x00, 0x85, 0xF8,

10 | 0x85, 0xFA, 0x85, 0xFC, 0x85, 0xFE, 0xA9, 0x20,

11 | 0x85, 0xF9, 0xA9, 0x21, 0x85, 0xFB, 0xA9, 0x22,

12 | 0x85, 0xFD, 0xA9, 0x23, 0x85, 0xFF, 0xA0, 0x00,

13 | 0xAD, 0x00, 0x9E, 0x8D, 0x20, 0xD0, 0xD0, 0xF8,

14 | 0xB9, 0x00, 0x84, 0x91, 0xF8, 0xB9, 0x00, 0x85,

15 | 0x91, 0xFA, 0xB9, 0x00, 0x86, 0x91, 0xFC, 0xB9,

16 | 0x00, 0x87, 0x91, 0xFE, 0xC8, 0xD0, 0xE1, 0xAD,

17 | 0x01, 0x9E, 0x18, 0xA9, 0x04, 0x65, 0xF9, 0x85,

18 | 0xF9, 0xA9, 0x04, 0x65, 0xFB, 0x85, 0xFB, 0xA9,

19 | 0x04, 0x65, 0xFD, 0x85, 0xFD, 0xA9, 0x04, 0x65,

20 | 0xFF, 0x85, 0xFF, 0xCA, 0xD0, 0xC2, 0xA2, 0x00,

21 | 0xBD, 0x00, 0x84, 0x9D, 0x00, 0x78, 0xE8, 0xD0,

22 | 0xF7, 0xBD, 0x00, 0x85, 0x9D, 0x00, 0x79, 0xE8,

23 | 0xD0, 0xF7, 0x4C, 0x00, 0x30,

24 | };

25 |

--------------------------------------------------------------------------------

/c64-rom/loader_rom.h:

--------------------------------------------------------------------------------

1 | #pragma once

2 |

3 | extern const uint8_t loader_rom[157];

4 |

--------------------------------------------------------------------------------

/c64-rom/raspi.bmp:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/cknave/c64-pico-ram-interface/c3c7f13a8c635f3e2ce99bbe791d3eede2769408/c64-rom/raspi.bmp

--------------------------------------------------------------------------------

/c64-rom/raspi.h:

--------------------------------------------------------------------------------

1 | #pragma once

2 |

3 | extern const uint8_t raspi[23042];

4 |

--------------------------------------------------------------------------------

/c64-rom/raspi.nuf:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/cknave/c64-pico-ram-interface/c3c7f13a8c635f3e2ce99bbe791d3eede2769408/c64-rom/raspi.nuf

--------------------------------------------------------------------------------

/c64-rom/raspi.xcf:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/cknave/c64-pico-ram-interface/c3c7f13a8c635f3e2ce99bbe791d3eede2769408/c64-rom/raspi.xcf

--------------------------------------------------------------------------------

/docs/command-sequence.puml:

--------------------------------------------------------------------------------

1 | @startuml

2 | autonumber

3 |

4 | participant "Pico CPU" as P

5 | participant "GPIO pins" as G

6 | queue "command sm\nTX FIFO" as TX

7 | queue "command sm\nRX FIFO" as RX

8 | participant "address decoder PIO\nstate machine" as AD

9 | participant "command PIO\nstate machine" as CSM

10 |

11 | title Handling a command

12 |

13 | P -> TX: Put a value on the TX FIFO\nto indicate ready for commands

14 |

15 | P -> RX: Wait for a command

16 |

17 | == The C64 reads from the command area ==

18 |

19 | G -> AD: Wait for ROM read to start\n(ROML or ROMH low)

20 |

21 | AD -> CSM: Trigger by IRQ

22 |

23 | G -> CSM: Read the low 8-bit address from address bus

24 |

25 | opt if the address is not 00

26 |

27 | CSM -> RX: put 8-bit address \non RX FIFO

28 |

29 | TX -> CSM: consume the value from the TX FIFO\nto indicate the CPU is busy

30 |

31 | end

32 |

33 | CSM -> G: Write the STATUS register to data\nbus and set "output enable" low

34 |

35 | G -> AD: Wait for ROM read to end\n(ROML or ROMH high)

36 |

37 | AD -> G: Set "output enable" high

38 |

39 | P <- RX: Pico receives the command\nfrom the RX FIFO

40 |

41 | == The Pico handles the command ==

42 |

43 | P -> TX: Put a value on the TX FIFO\nto indicate ready for commands

44 |

45 | @enduml

46 |

--------------------------------------------------------------------------------

/docs/command-sequence.svg:

--------------------------------------------------------------------------------

1 | Handling a command Pico CPU Pico CPU GPIO pins GPIO pins command sm TX FIFO command sm TX FIFO command sm RX FIFO command sm RX FIFO address decoder PIO state machine address decoder PIO state machine command PIO state machine command PIO state machine 1 Put a value on the TX FIFO to indicate ready for commands 2 Wait for a command The C64 reads from the command area 3 Wait for ROM read to start (ROML or ROMH low) 4 Trigger by IRQ 5 Read the low 8-bit address from address bus opt [if the address is not 00] 6 put 8-bit address on RX FIFO 7 consume the value from the TX FIFO to indicate the CPU is busy 8 Write the STATUS register to data bus and set "output enable" low 9 Wait for ROM read to end (ROML or ROMH high) 10 Set "output enable" high 11 Pico receives the command from the RX FIFO The Pico handles the command 12 Put a value on the TX FIFO to indicate ready for commands 14-bit address from address bus

20 |

21 | RSM -> RSM: Combine 14-bit address \nwith 18-bit base address

22 |

23 | RSM -> RX: Put 32-bit address \non RX FIFO

24 |

25 | RX -> D1: Trigger by FIFO

26 |

27 | D1 -> D2: Write 32-bit address to\nDMA 2 configuration and\ntrigger DMA 2

28 |

29 | D2 -> RAM: Read 8-bit data \nfrom 32-bit address

30 | autonumber stop

31 | RAM -> D2

32 | autonumber resume

33 |

34 | D2 -> TX: Put 8-bit data on TX FIFO

35 |

36 | TX -> RSM: Wait for 8-bit data on TX FIFO

37 |

38 | RSM -> G: Write 8-bit data to data bus\nand set "output enable" low

39 |

40 | G -> AD: Wait for ROM read to end\n(ROML or ROMH high)

41 |

42 | AD -> G: Set "output enable" high

43 |

44 | @enduml

45 |

--------------------------------------------------------------------------------

/docs/read-sequence.svg:

--------------------------------------------------------------------------------

1 | Reading the "ROM" GPIO pins GPIO pins address decoder PIO state machine address decoder PIO state machine read PIO state machine read PIO state machine read sm RX FIFO read sm RX FIFO read sm TX FIFO read sm TX FIFO DMA channel 1 DMA channel 1 DMA channel 2 DMA channel 2 Pico RAM Pico RAM 1 Wait for ROM read to start (ROML or ROMH low) 2 Trigger by IRQ 3 Read 14-bit address from address bus 4 Combine 14-bit address with 18-bit base address 5 Put 32-bit address on RX FIFO 6 Trigger by FIFO 7 Write 32-bit address to DMA 2 configuration and trigger DMA 2 8 Read 8-bit data from 32-bit address 9 Put 8-bit data on TX FIFO 10 Wait for 8-bit data on TX FIFO 11 Write 8-bit data to data bus and set "output enable" low 12 Wait for ROM read to end (ROML or ROMH high) 13 Set "output enable" high

3 | #include

4 | #include

5 |

6 | #include "hardware/dma.h"

7 | #include "hardware/irq.h"

8 | #include "hardware/pio.h"

9 | #include "pico/binary_info.h"

10 | #include "pico/stdlib.h"

11 |

12 | #include "address_decoder.pio.h"

13 | #include "command.pio.h"

14 | #include "loader_rom.h"

15 | #include "raspi.h"

16 | #include "read.pio.h"

17 |

18 | // Blink error codes

19 | const uint ERR_ADD_DECODER_PROGRAM = 1;

20 | const uint ERR_DECODER_PROGRAM_SM = 2;

21 | const uint ERR_ADD_READ_PROGRAM = 3;

22 | const uint ERR_READ_PROGRAM_SM = 4;

23 | const uint ERR_ADD_COMMAND_PROGRAM = 5;

24 | const uint ERR_COMMAND_PROGRAM_SM = 6;

25 |

26 | // Pin assignments

27 | // Note: PIO programs assume the pins are in this order!

28 | const uint PIN_D0 = 0;

29 | const uint PIN_D1 = 1;

30 | const uint PIN_D2 = 2;

31 | const uint PIN_D3 = 3;

32 | const uint PIN_D4 = 4;

33 | const uint PIN_D5 = 5;

34 | const uint PIN_D6 = 6;

35 | const uint PIN_D7 = 7;

36 | const uint PIN_A0 = 8;

37 | const uint PIN_A1 = 9;

38 | const uint PIN_A2 = 10;

39 | const uint PIN_A3 = 11;

40 | const uint PIN_A4 = 12;

41 | const uint PIN_A5 = 13;

42 | const uint PIN_A6 = 14;

43 | const uint PIN_A7 = 15;

44 | const uint PIN_A8 = 16;

45 | const uint PIN_A9 = 17;

46 | const uint PIN_A10 = 18;

47 | const uint PIN_A11 = 19;

48 | const uint PIN_A12 = 20;

49 | const uint PIN_A13 = 21;

50 | const uint PIN_ROML = 22;

51 | const uint PIN_ROMH = 26;

52 | const uint PIN_IE = 27;

53 | const uint PIN_OE = 28;

54 |

55 | // PIO IRQ bits

56 | const uint PIO_IRQ_ON_READ = 1;

57 |

58 | // NUFLI offset in our ROM area

59 | const uint NUFLI_OFFSET = 0x400;

60 | const uint NUFLI_WINDOW_SIZE = 0x400;

61 |

62 |

63 | typedef enum {

64 | CMD_NEXT_PAGE = 0x01, // Advance the NUFLI window to the next 1K

65 | CMD_SLEEP = 0x02, // Test a slow command that sleeps for 5 seconds

66 | } command_t;

67 |

68 | const uint BLINK_MS = 100;

69 |

70 |

71 | void on_pio_irq();

72 | void do_a_blink();

73 | void read_dma_init(PIO pio, uint sm, char *base_address);

74 | void errorblink(int code) __attribute__((noreturn));

75 | static inline void init_output_pin(uint pin, bool value);

76 |

77 |

78 | #pragma clang diagnostic push

79 | #pragma ide diagnostic ignored "EndlessLoop"

80 |

81 | int main() {

82 | bi_decl(bi_1pin_with_name(PIN_D0, "data output pin 0 (U3 pin 2)"))

83 | bi_decl(bi_1pin_with_name(PIN_D1, "data output pin 1 (U3 pin 4)"))

84 | bi_decl(bi_1pin_with_name(PIN_D2, "data output pin 2 (U3 pin 6)"))

85 | bi_decl(bi_1pin_with_name(PIN_D3, "data output pin 3 (U3 pin 8)"))

86 | bi_decl(bi_1pin_with_name(PIN_D4, "data output pin 4 (U3 pin 11)"))

87 | bi_decl(bi_1pin_with_name(PIN_D5, "data output pin 5 (U3 pin 13)"))

88 | bi_decl(bi_1pin_with_name(PIN_D6, "data output pin 6 (U3 pin 15)"))

89 | bi_decl(bi_1pin_with_name(PIN_D7, "data output pin 7 (U3 pin 17)"))

90 | bi_decl(bi_1pin_with_name(PIN_A0, "address input pin 0 (U2 pin 18)"))

91 | bi_decl(bi_1pin_with_name(PIN_A1, "address input pin 1 (U2 pin 16)"))

92 | bi_decl(bi_1pin_with_name(PIN_A2, "address input pin 2 (U2 pin 14)"))

93 | bi_decl(bi_1pin_with_name(PIN_A3, "address input pin 3 (U2 pin 12)"))

94 | bi_decl(bi_1pin_with_name(PIN_A4, "address input pin 4 (U2 pin 9)"))

95 | bi_decl(bi_1pin_with_name(PIN_A5, "address input pin 5 (U2 pin 7)"))

96 | bi_decl(bi_1pin_with_name(PIN_A6, "address input pin 6 (U2 pin 5)"))

97 | bi_decl(bi_1pin_with_name(PIN_A7, "address input pin 7 (U2 pin 3)"))

98 | bi_decl(bi_1pin_with_name(PIN_A8, "address input pin 8 (U1 pin 3)"))

99 | bi_decl(bi_1pin_with_name(PIN_A9, "address input pin 9 (U1 pin 5)"))

100 | bi_decl(bi_1pin_with_name(PIN_A10, "address input pin 10 (U1 pin 7)"))

101 | bi_decl(bi_1pin_with_name(PIN_A11, "address input pin 11 (U1 pin 9)"))

102 | bi_decl(bi_1pin_with_name(PIN_A12, "address input pin 12 (U1 pin 12)"))

103 | bi_decl(bi_1pin_with_name(PIN_A13, "address input pin 13 (U1 pin 14)"))

104 | bi_decl(bi_1pin_with_name(PIN_ROML, "ROML input pin (U1 pin 16)"))

105 | bi_decl(bi_1pin_with_name(PIN_ROMH, "ROMH input pin (U1 pin 18)"))

106 | bi_decl(bi_1pin_with_name(PIN_OE, "\"input enable\" output pin (U1 and U2, pins 1 and 19)"))

107 | bi_decl(bi_1pin_with_name(PIN_OE, "\"output enable\" output pin (U3 pins 1 and 19)"))

108 |

109 | // Start with I/O to the C64 disabled

110 | init_output_pin(PIN_OE, true); // high = disabled

111 | init_output_pin(PIN_IE, true); // high = disabled

112 |

113 | stdio_usb_init();

114 | printf("\n\n\n");

115 | printf("C64 pico ram interface %s\n", PICO_PROGRAM_VERSION_STRING);

116 |

117 | // Data exposed by the ROM window must be aligned by 16 kbytes so we can use the least

118 | // significant bits of its address for A0-A13

119 | const int rom_size = 16384;

120 | char *rom_data = memalign(rom_size, rom_size);

121 |

122 | // Initialize the ROM area with our loader ROM

123 | memcpy(rom_data, loader_rom, sizeof(loader_rom));

124 |

125 | // Initialize the NUFLI area of our ROM with the first 1KB

126 | int raspi_offset = 0;

127 | memcpy(rom_data + NUFLI_OFFSET, raspi, NUFLI_WINDOW_SIZE);

128 |

129 | PIO pio = pio0;

130 |

131 | // Address decoder: waits for ROMH/ROML line to be set low, and determines whether the address

132 | // to read is a command or a normal ROM read. Each state machine monitors one ROM line.

133 | if(!pio_can_add_program(pio, &address_decoder_program)) {

134 | errorblink(ERR_ADD_DECODER_PROGRAM);

135 | }

136 | uint address_decoder_offset = pio_add_program(pio, &address_decoder_program);

137 | uint address_decoder_sm[2];

138 | const uint rom_pins[2] = {PIN_ROMH, PIN_ROML};

139 | for(int i = 0; i < 2; i++) {

140 | address_decoder_sm[i] = pio_claim_unused_sm(pio, true);

141 | if(address_decoder_sm[i] == -1) {

142 | errorblink(ERR_DECODER_PROGRAM_SM + i);

143 | }

144 | address_decoder_program_init(

145 | pio,

146 | address_decoder_sm[i],

147 | address_decoder_offset,

148 | PIN_A8,

149 | rom_pins[i],

150 | PIN_OE);

151 | }

152 |

153 | // Read handler: send rom_data value over D0..D7 when the C64 reads from ROML or ROMH

154 | if(!pio_can_add_program(pio, &read_program)) {

155 | errorblink(ERR_ADD_READ_PROGRAM);

156 | }

157 | uint read_offset = pio_add_program(pio, &read_program);

158 | uint read_sm = pio_claim_unused_sm(pio, true);

159 | if(read_sm == -1) {

160 | errorblink(ERR_READ_PROGRAM_SM);

161 | }

162 | read_program_init(

163 | pio,

164 | read_sm,

165 | read_offset,

166 | PIN_D0,

167 | PIN_A0,

168 | PIN_OE,

169 | rom_data);

170 | read_dma_init(pio, read_sm, rom_data);

171 |

172 | // Command handler: put command NN on the FIFO when the CPU reads from address $BFNN

173 | if(!pio_can_add_program(pio, &command_program)) {

174 | errorblink(ERR_ADD_COMMAND_PROGRAM);

175 | }

176 | uint command_offset = pio_add_program(pio, &command_program);

177 | uint command_sm = pio_claim_unused_sm(pio, true);

178 | if(command_sm == -1) {

179 | errorblink(ERR_COMMAND_PROGRAM_SM);

180 | }

181 | command_program_init(

182 | pio,

183 | command_sm,

184 | command_offset,

185 | PIN_A0,

186 | PIN_D0,

187 | PIN_OE);

188 |

189 | // Set up blinkenlight pin

190 | gpio_init(PICO_DEFAULT_LED_PIN);

191 | gpio_set_dir(PICO_DEFAULT_LED_PIN, GPIO_OUT);

192 | gpio_put(PICO_DEFAULT_LED_PIN, 0);

193 |

194 | // Install IRQ handler for blinkenlights on read

195 | // Per the RP2040 datasheet (PIO: IRQ0_INTE Register, p. 399)

196 | // state machine enable flags start at bit 8

197 | pio->inte0 = 1 << (8 + address_decoder_sm[0]);

198 | irq_set_exclusive_handler(PIO0_IRQ_0, on_pio_irq);

199 | irq_set_enabled(PIO0_IRQ_0, true);

200 |

201 | // READY! Open the floodgates!

202 | gpio_put(PIN_IE, false); // low = enabled

203 |

204 | printf("Address decoder ROMH sm: %d\n", address_decoder_sm[0]);

205 | printf("Address decoder ROML sm: %d\n", address_decoder_sm[1]);

206 | printf("Read sm: %d\n", read_sm);

207 | printf("Command sm: %d\n", command_sm);

208 | printf("Pico RAM window start: 0x%08X\n", (uint)rom_data);

209 | printf("First 8 bytes of ROM: %02X %02X %02X %02X %02X %02X %02X %02X\n",

210 | rom_data[0], rom_data[1], rom_data[2], rom_data[3], rom_data[4], rom_data[5],

211 | rom_data[6], rom_data[7]);

212 | printf("First 8 bytes of NUFLI: %02X %02X %02X %02X %02X %02X %02X %02X\n",

213 | ((char *)(rom_data + NUFLI_OFFSET))[0], ((char *)(rom_data + NUFLI_OFFSET))[1],

214 | ((char *)(rom_data + NUFLI_OFFSET))[2], ((char *)(rom_data + NUFLI_OFFSET))[3],

215 | ((char *)(rom_data + NUFLI_OFFSET))[4], ((char *)(rom_data + NUFLI_OFFSET))[5],

216 | ((char *)(rom_data + NUFLI_OFFSET))[6], ((char *)(rom_data + NUFLI_OFFSET))[7]);

217 | printf("ROM address: $8000\n");

218 | printf("Command address prefix: $%04X\n", 0x8000 + (address_decoder_COMMAND_PREFIX << 8));

219 |

220 | const char spinner[] = {'|', '/', '-', '\\'};

221 | while(true) {

222 | pio_sm_put(pio, command_sm, 1); // tell the command program we're ready

223 | printf("\nReady for command %c", spinner[0]);

224 |

225 | uint64_t last_hb = time_us_64();

226 | uint spinner_pos = 0;

227 | do {

228 | uint64_t now = time_us_64();

229 | if(now - last_hb >= 1000000 / sizeof(spinner)) {

230 | printf("\b%c", spinner[spinner_pos]);

231 | spinner_pos++;

232 | if(spinner_pos == sizeof(spinner)) {

233 | spinner_pos = 0;

234 | }

235 | last_hb = now;

236 | }

237 | } while(pio_sm_is_rx_fifo_empty(pio, command_sm));

238 | printf("\b \n");

239 |

240 | uint command = pio_sm_get_blocking(pio, command_sm);

241 | printf("Got command %08X\n", command);

242 |

243 | switch(command) {

244 | case CMD_NEXT_PAGE:

245 | raspi_offset += NUFLI_WINDOW_SIZE;

246 | if(raspi_offset >= sizeof(raspi)) {

247 | raspi_offset = 0;

248 | }

249 | printf("NUFLI start is now %02X\n", (uint)raspi_offset);

250 | memcpy(rom_data + NUFLI_OFFSET, raspi + raspi_offset, NUFLI_WINDOW_SIZE);

251 | printf("First 8 bytes: %02X %02X %02X %02X %02X %02X %02X %02X\n", ((char *)(rom_data + NUFLI_OFFSET))[0], ((char *)(rom_data + NUFLI_OFFSET))[1], ((char *)(rom_data + NUFLI_OFFSET))[2], ((char *)(rom_data + NUFLI_OFFSET))[3], ((char *)(rom_data + NUFLI_OFFSET))[4], ((char *)(rom_data + NUFLI_OFFSET))[5], ((char *)(rom_data + NUFLI_OFFSET))[6], ((char *)(rom_data + NUFLI_OFFSET))[7]);

252 | break;

253 |

254 | case CMD_SLEEP:

255 | printf("Sleeping\n");

256 | sleep_ms(5000);

257 | printf("Done\n");

258 | break;

259 | }

260 | }

261 | }

262 |

263 | #pragma clang diagnostic pop

264 |

265 |

266 | // Set up DMA channels for handling reads

267 | void read_dma_init(PIO pio, uint sm, char *base_address) {

268 | // Read channel: copy requested byte to TX fifo (source address set by write channel below)

269 | uint read_channel = 0;

270 | dma_channel_claim(read_channel);

271 |

272 | dma_channel_config read_config = dma_channel_get_default_config(read_channel);

273 | channel_config_set_read_increment(&read_config, false);

274 | channel_config_set_write_increment(&read_config, false);

275 | channel_config_set_dreq(&read_config, pio_get_dreq(pio, sm, true));

276 | channel_config_set_transfer_data_size(&read_config, DMA_SIZE_8);

277 |

278 | dma_channel_configure(read_channel,

279 | &read_config,

280 | &pio->txf[sm], // write to TX fifo

281 | base_address, // read from base address (overwritten by write channel)

282 | 1, // transfer count

283 | false); // start later

284 |

285 | // Write channel: copy address from RX fifo to the read channel's READ_ADDR_TRIGGER

286 | uint write_channel = 1;

287 | dma_channel_claim(write_channel);

288 | dma_channel_config write_config = dma_channel_get_default_config(write_channel);

289 | channel_config_set_read_increment(&write_config, false);

290 | channel_config_set_write_increment(&write_config, false);

291 | channel_config_set_dreq(&write_config, pio_get_dreq(pio, sm, false));

292 | channel_config_set_transfer_data_size(&write_config, DMA_SIZE_32);

293 |

294 | volatile void *read_channel_addr = &dma_channel_hw_addr(read_channel)->al3_read_addr_trig;

295 | dma_channel_configure(write_channel,

296 | &write_config,

297 | read_channel_addr, // write to read_channel READ_ADDR_TRIGGER

298 | &pio->rxf[sm], // read from RX fifo

299 | 0xffffffff, // do many transfers

300 | true); // start now

301 | }

302 |

303 | // Timer for on_clear

304 | alarm_id_t clear_read_alarm = -1;

305 |

306 | // Clear the LED after it's blunk

307 | int64_t on_clear_led(alarm_id_t alarm_id, void *user_data) {

308 | gpio_put(PICO_DEFAULT_LED_PIN, 0);

309 | clear_read_alarm = -1;

310 | return 0;

311 | }

312 |

313 | // On IRQ0 (command received), blink the LED

314 | void on_pio_irq() {

315 | PIO pio = pio0;

316 | if(pio->irq & PIO_IRQ_ON_READ) {

317 | hw_clear_bits(&pio->irq, PIO_IRQ_ON_READ);

318 | do_a_blink();

319 | }

320 | }

321 |

322 | void do_a_blink() {

323 | // Turn on the LED

324 | gpio_put(PICO_DEFAULT_LED_PIN, 1);

325 |

326 | // If we already had a timer to turn it off, cancel it

327 | if(clear_read_alarm > 0) {

328 | cancel_alarm(clear_read_alarm);

329 | }

330 |

331 | // Turn off the LED later

332 | clear_read_alarm = add_alarm_in_ms(BLINK_MS, on_clear_led, NULL, true);

333 | }

334 |

335 | // Repeat a series of blinks forever

336 | void errorblink(int code) {

337 | gpio_init(PICO_DEFAULT_LED_PIN);

338 | gpio_set_dir(PICO_DEFAULT_LED_PIN, GPIO_OUT);

339 | while(true) {

340 | for(int i = 0; i < code; i++) {

341 | gpio_put(PICO_DEFAULT_LED_PIN, 1);

342 | sleep_ms(333);

343 | gpio_put(PICO_DEFAULT_LED_PIN, 0);

344 | sleep_ms(333);

345 | }

346 | sleep_ms(667);

347 | }

348 | }

349 |

350 | // Initialize an output GPIO pin and set its value

351 | void init_output_pin(uint pin, bool value) {

352 | gpio_init(pin);

353 | gpio_set_dir(pin, true); // output direction

354 | gpio_put(pin, value);

355 | }

356 |

--------------------------------------------------------------------------------

/firmware/command.pio:

--------------------------------------------------------------------------------

1 | .program command

2 | .side_set 1 opt

3 |

4 | ; Handle a read from the C64 by putting the lower 8 bits of the address on the RX FIFO. This

5 | ; is used to allow the C64 to "write" a byte to the command queue by reading from a specific

6 | ; block of 256 bytes.

7 | ;

8 | ; It expects to be woken up with IRQ 5 from the address_decoder program when it detects ROMH

9 | ; or ROML is active with the high 6 bits of the address set to the command prefix (configured

10 | ; by address_decoder_program_init).

11 | ;

12 | ; Commands can be queued up to the size of the RX FIFO. This program will always write one

13 | ; of these values to the data bus:

14 | ;

15 | ; | Value | Description |

16 | ; | 0x00 | CPU was ready when this command was received |

17 | ; | 0xff | CPU was busy with another command |

18 | ;

19 | ; The command 0x00 is used to check this status, and will not be sent to the CPU.

20 | ;

21 | ; All other commands will set the busy flag and put the low 8 bits of the address on the RX

22 | ; FIFO.

23 | ;

24 | ; To clear the busy flag, the CPU should put any value on the TX FIFO before waiting for a

25 | ; command. The value will be consumed when a command (other than 0x00) is received.

26 | ;

27 | ; Input pins:

28 | ; - A0..A13

29 | ; Output pins:

30 | ; - D0..D7

31 | ; Side-set pins:

32 | ; - OE

33 | ; Interrupts:

34 | ; - Waits on IRQ 5

35 | ; - Sets IRQ 0 when a command is received

36 |

37 | start:

38 | wait 1 irq 5 ; wait for address_decoder to detect a read

39 | in pins, 8 ; shift the low 8 bits of the address (the command) into ISR

40 | mov x, isr ; copy the command to X for comparison

41 |

42 | jmp !x, dont_push ; if the command is 0, don't send it to the CPU

43 | push noblock ; push the command from ISR onto the RX FIFO

44 | irq set 0 ; tell the CPU to blink the LED

45 | dont_push:

46 |

47 | mov pins, status side 0 ; put STATUS on the data bus (0xff if the TX FIFO is empty,

48 | ; i.e. busy) and enable output

49 |

50 | jmp !x, start ; if the command is 0, don't consume the ready indicator

51 | pull noblock ; consume the ready indicator, making the TX FIFO empty

52 |

53 |

54 | % c-sdk {

55 | static inline void command_program_init(

56 | PIO pio,

57 | uint sm,

58 | uint offset,

59 | uint a0_pin,

60 | uint d0_pin,

61 | uint oe_pin) {

62 | pio_sm_config c = command_program_get_default_config(offset);

63 |

64 | // Use A0..A13 as input pins

65 | sm_config_set_in_pins(&c, a0_pin);

66 | for(int i = 0; i < 14; i++) {

67 | pio_gpio_init(pio, a0_pin + i);

68 | }

69 | pio_sm_set_consecutive_pindirs(pio, sm, a0_pin, 14, GPIO_IN);

70 |

71 | // Use D0..D7 as output pins

72 | sm_config_set_out_pins(&c, d0_pin, 8);

73 | for(int i = 0; i < 8; i++) {

74 | pio_gpio_init(pio, d0_pin + i);

75 | }

76 | pio_sm_set_consecutive_pindirs(pio, sm, d0_pin, 8, GPIO_OUT);

77 |

78 | // Use OE as the side-set pin

79 | sm_config_set_sideset_pins(&c, oe_pin);

80 | pio_gpio_init(pio, oe_pin);

81 | pio_sm_set_consecutive_pindirs(pio, sm, oe_pin, 1, GPIO_OUT);

82 |

83 | // Configure the STATUS bits to be set if the TX FIFO is empty. The CPU can push to

84 | // the TX FIFO to signal that it's ready to process a command.

85 | sm_config_set_mov_status(&c, STATUS_TX_LESSTHAN, 1);

86 |

87 | // Shift in leftwards so we only fill the low 8 bits of the word (the command)

88 | sm_config_set_in_shift(&c,

89 | false, // don't shift right

90 | false, // don't autopush

91 | 32); // push threshold (doesn't matter)

92 |

93 | // Load our configuration, and jump to the start of the program

94 | pio_sm_init(pio, sm, offset, &c);

95 | // Set the state machine running

96 | pio_sm_set_enabled(pio, sm, true);

97 | }

98 |

99 | %}

100 |

--------------------------------------------------------------------------------

/firmware/pico_sdk_import.cmake:

--------------------------------------------------------------------------------

1 | # This is a copy of /external/pico_sdk_import.cmake

2 |

3 | # This can be dropped into an external project to help locate this SDK

4 | # It should be include()ed prior to project()

5 |

6 | if (DEFINED ENV{PICO_SDK_PATH} AND (NOT PICO_SDK_PATH))

7 | set(PICO_SDK_PATH $ENV{PICO_SDK_PATH})

8 | message("Using PICO_SDK_PATH from environment ('${PICO_SDK_PATH}')")

9 | endif ()

10 |

11 | if (DEFINED ENV{PICO_SDK_FETCH_FROM_GIT} AND (NOT PICO_SDK_FETCH_FROM_GIT))

12 | set(PICO_SDK_FETCH_FROM_GIT $ENV{PICO_SDK_FETCH_FROM_GIT})

13 | message("Using PICO_SDK_FETCH_FROM_GIT from environment ('${PICO_SDK_FETCH_FROM_GIT}')")

14 | endif ()

15 |

16 | if (DEFINED ENV{PICO_SDK_FETCH_FROM_GIT_PATH} AND (NOT PICO_SDK_FETCH_FROM_GIT_PATH))

17 | set(PICO_SDK_FETCH_FROM_GIT_PATH $ENV{PICO_SDK_FETCH_FROM_GIT_PATH})

18 | message("Using PICO_SDK_FETCH_FROM_GIT_PATH from environment ('${PICO_SDK_FETCH_FROM_GIT_PATH}')")

19 | endif ()

20 |

21 | set(PICO_SDK_PATH "${PICO_SDK_PATH}" CACHE PATH "Path to the Raspberry Pi Pico SDK")

22 | set(PICO_SDK_FETCH_FROM_GIT "${PICO_SDK_FETCH_FROM_GIT}" CACHE BOOL "Set to ON to fetch copy of SDK from git if not otherwise locatable")

23 | set(PICO_SDK_FETCH_FROM_GIT_PATH "${PICO_SDK_FETCH_FROM_GIT_PATH}" CACHE FILEPATH "location to download SDK")

24 |

25 | if (NOT PICO_SDK_PATH)

26 | if (PICO_SDK_FETCH_FROM_GIT)

27 | include(FetchContent)

28 | set(FETCHCONTENT_BASE_DIR_SAVE ${FETCHCONTENT_BASE_DIR})

29 | if (PICO_SDK_FETCH_FROM_GIT_PATH)

30 | get_filename_component(FETCHCONTENT_BASE_DIR "${PICO_SDK_FETCH_FROM_GIT_PATH}" REALPATH BASE_DIR "${CMAKE_SOURCE_DIR}")

31 | endif ()

32 | FetchContent_Declare(

33 | pico_sdk

34 | GIT_REPOSITORY https://github.com/raspberrypi/pico-sdk

35 | GIT_TAG master

36 | )

37 | if (NOT pico_sdk)

38 | message("Downloading Raspberry Pi Pico SDK")

39 | FetchContent_Populate(pico_sdk)

40 | set(PICO_SDK_PATH ${pico_sdk_SOURCE_DIR})

41 | endif ()

42 | set(FETCHCONTENT_BASE_DIR ${FETCHCONTENT_BASE_DIR_SAVE})

43 | else ()

44 | message(FATAL_ERROR

45 | "SDK location was not specified. Please set PICO_SDK_PATH or set PICO_SDK_FETCH_FROM_GIT to on to fetch from git."

46 | )

47 | endif ()

48 | endif ()

49 |

50 | get_filename_component(PICO_SDK_PATH "${PICO_SDK_PATH}" REALPATH BASE_DIR "${CMAKE_BINARY_DIR}")

51 | if (NOT EXISTS ${PICO_SDK_PATH})

52 | message(FATAL_ERROR "Directory '${PICO_SDK_PATH}' not found")

53 | endif ()

54 |

55 | set(PICO_SDK_INIT_CMAKE_FILE ${PICO_SDK_PATH}/pico_sdk_init.cmake)

56 | if (NOT EXISTS ${PICO_SDK_INIT_CMAKE_FILE})

57 | message(FATAL_ERROR "Directory '${PICO_SDK_PATH}' does not appear to contain the Raspberry Pi Pico SDK")

58 | endif ()

59 |

60 | set(PICO_SDK_PATH ${PICO_SDK_PATH} CACHE PATH "Path to the Raspberry Pi Pico SDK" FORCE)

61 |

62 | include(${PICO_SDK_INIT_CMAKE_FILE})

63 |

--------------------------------------------------------------------------------

/firmware/read.pio:

--------------------------------------------------------------------------------

1 | .program read

2 | .side_set 1 opt

3 |

4 | ; Handle a read from the C64 by sending a byte from the TX fifo on the D0..D7 lines.

5 | ;

6 | ; The address is put on the RX fifo, which is DMA'd to a second DMA's configuration, and that

7 | ; DMA puts the data on the TX fifo. That data is output to the data lines.

8 | ;

9 | ; The lower 18 bits of the Y register must be initialized with the upper 18 bits of the address

10 | ; to read from.

11 | ;

12 | ; Input pins:

13 | ; - A0..A13

14 | ; Output pins:

15 | ; - D0..D7

16 | ; Side-set pins:

17 | ; - OE

18 | ; Interrupts:

19 | ; - Waits on IRQ 4

20 |

21 |

22 | ;

23 | ; Initialization:

24 | ; (need to block before the program starts, otherwise we don't seem to wake up to get our address)

25 | ;

26 | pull block ; save the base address of the pico's RAM to Y

27 | mov y, osr ; (should be sent by read_program_init)

28 |

29 | ;

30 | ; Main loop:

31 | ;

32 | .wrap_target

33 | wait 1 irq 4 ; wait for address_decoder to detect a read

34 | in pins, 14 ; read low address bits into ISR

35 | in y, 18 ; shift high address bits into ISR to form a complete address

36 | push noblock ; push the address onto the RX fifo

37 | pull block ; stall until we load data from the TX fifo into OSR

38 | out pins, 8 side 0 ; write 8 bit value from OSR to the data bus and enable output

39 | .wrap

40 |

41 | % c-sdk {

42 | static inline void read_program_init(

43 | PIO pio,

44 | uint sm,

45 | uint offset,

46 | uint d0_pin,

47 | uint a0_pin,

48 | uint oe_pin,

49 | char *base_address) {

50 | pio_sm_config c = read_program_get_default_config(offset);

51 |

52 | // Use A0..A13 as input pins

53 | sm_config_set_in_pins(&c, a0_pin);

54 | for(int i = 0; i < 14; i++) {

55 | pio_gpio_init(pio, a0_pin + i);

56 | }

57 | pio_sm_set_consecutive_pindirs(pio, sm, a0_pin, 14, GPIO_IN);

58 |

59 | // Use D0..D7 as output pins

60 | sm_config_set_out_pins(&c, d0_pin, 8);

61 | for(int i = 0; i < 8; i++) {

62 | pio_gpio_init(pio, d0_pin + i);

63 | }

64 | pio_sm_set_consecutive_pindirs(pio, sm, d0_pin, 8, GPIO_OUT);

65 |

66 | // Use OE as the side-set pin

67 | sm_config_set_sideset_pins(&c, oe_pin);

68 | pio_gpio_init(pio, oe_pin);

69 | pio_sm_set_consecutive_pindirs(pio, sm, oe_pin, 1, GPIO_OUT);

70 |

71 | // Load our configuration, and jump to the start of the program

72 | pio_sm_init(pio, sm, offset, &c);

73 | // Set the state machine running

74 | pio_sm_set_enabled(pio, sm, true);

75 |

76 | // Initialization is waiting to pull the high 18 bits of the base address

77 | pio_sm_put(pio, sm, ((uint32_t)base_address) >> 14);

78 | }

79 |

80 | %}

81 |

--------------------------------------------------------------------------------

/pcb/.gitignore:

--------------------------------------------------------------------------------

1 | _autosave*

2 | *-backups

3 | *-bak

4 | *.bck

5 | *-cache

6 | *-cache.lib

7 |

--------------------------------------------------------------------------------

/pcb/fp-lib-table:

--------------------------------------------------------------------------------

1 | (fp_lib_table

2 | (lib (name picocart)(type KiCad)(uri ${KIPRJMOD}/picocart.pretty)(options "")(descr ""))

3 | )

4 |

--------------------------------------------------------------------------------

/pcb/gerber/picocart-B_Mask.gbs:

--------------------------------------------------------------------------------

1 | %TF.GenerationSoftware,KiCad,Pcbnew,6.0.0*%

2 | %TF.CreationDate,2022-02-18T00:32:39-05:00*%

3 | %TF.ProjectId,picocart,7069636f-6361-4727-942e-6b696361645f,rev?*%

4 | %TF.SameCoordinates,Original*%

5 | %TF.FileFunction,Soldermask,Bot*%

6 | %TF.FilePolarity,Negative*%

7 | %FSLAX46Y46*%

8 | G04 Gerber Fmt 4.6, Leading zero omitted, Abs format (unit mm)*

9 | G04 Created by KiCad (PCBNEW 6.0.0) date 2022-02-18 00:32:39*

10 | %MOMM*%

11 | %LPD*%

12 | G01*

13 | G04 APERTURE LIST*

14 | %ADD10O,1.700000X1.700000*%

15 | %ADD11R,1.700000X1.700000*%

16 | %ADD12C,5.000000*%

17 | %ADD13R,1.524000X8.316000*%

18 | G04 APERTURE END LIST*

19 | %TO.C,J1*%

20 | G36*

21 | X175318000Y-107354200D02*

22 | G01*

23 | X118306000Y-107354200D01*

24 | X118306000Y-98819800D01*

25 | X175318000Y-98819800D01*

26 | X175318000Y-107354200D01*

27 | G37*

28 | %TD*%

29 | D10*

30 | %TO.C,SW1*%

31 | X121412000Y-62992000D03*

32 | X121412000Y-60452000D03*

33 | D11*

34 | X121412000Y-57912000D03*

35 | %TD*%

36 | D10*

37 | %TO.C,J2*%

38 | X171958000Y-47470000D03*

39 | X171958000Y-50010000D03*

40 | D11*

41 | X171958000Y-52550000D03*

42 | D10*

43 | X171958000Y-55090000D03*

44 | X171958000Y-57630000D03*

45 | X171958000Y-60170000D03*

46 | X171958000Y-62710000D03*

47 | D11*

48 | X171958000Y-65250000D03*

49 | D10*

50 | X171958000Y-67790000D03*

51 | X171958000Y-70330000D03*

52 | X171958000Y-72870000D03*

53 | X171958000Y-75410000D03*

54 | D11*

55 | X171958000Y-77950000D03*

56 | D10*

57 | X171958000Y-80490000D03*

58 | X171958000Y-83030000D03*

59 | X171958000Y-85570000D03*

60 | X171958000Y-88110000D03*

61 | D11*

62 | X171958000Y-90650000D03*

63 | D10*

64 | X171958000Y-93190000D03*

65 | X171958000Y-95730000D03*

66 | X154178000Y-95730000D03*

67 | X154178000Y-93190000D03*

68 | D11*

69 | X154178000Y-90650000D03*

70 | D10*

71 | X154178000Y-88110000D03*

72 | X154178000Y-85570000D03*

73 | X154178000Y-83030000D03*

74 | X154178000Y-80490000D03*

75 | D11*

76 | X154178000Y-77950000D03*

77 | D10*

78 | X154178000Y-75410000D03*

79 | X154178000Y-72870000D03*

80 | X154178000Y-70330000D03*

81 | X154178000Y-67790000D03*

82 | D11*

83 | X154178000Y-65250000D03*

84 | D10*

85 | X154178000Y-62710000D03*

86 | X154178000Y-60170000D03*

87 | X154178000Y-57630000D03*

88 | X154178000Y-55090000D03*

89 | D11*

90 | X154178000Y-52550000D03*

91 | D10*

92 | X154178000Y-50010000D03*

93 | X154178000Y-47470000D03*

94 | %TD*%

95 | D12*

96 | %TO.C,REF\u002A\u002A*%

97 | X146810000Y-65040000D03*

98 | %TD*%

99 | D13*

100 | %TO.C,J1*%

101 | X120142000Y-102977800D03*

102 | X122682000Y-102977800D03*

103 | X125222000Y-102977800D03*

104 | X127762000Y-102977800D03*

105 | X130302000Y-102977800D03*

106 | X132842000Y-102977800D03*

107 | X135382000Y-102977800D03*

108 | X137922000Y-102977800D03*

109 | X140462000Y-102977800D03*

110 | X143002000Y-102977800D03*

111 | X145542000Y-102977800D03*

112 | X148082000Y-102977800D03*

113 | X150622000Y-102977800D03*

114 | X153162000Y-102977800D03*

115 | X155702000Y-102977800D03*

116 | X158242000Y-102977800D03*

117 | X160782000Y-102977800D03*

118 | X163322000Y-102977800D03*

119 | X165862000Y-102977800D03*

120 | X168402000Y-102977800D03*

121 | X170942000Y-102977800D03*

122 | X173482000Y-102977800D03*

123 | %TD*%

124 | M02*

125 |

--------------------------------------------------------------------------------

/pcb/gerber/picocart-B_Paste.gbp:

--------------------------------------------------------------------------------

1 | %TF.GenerationSoftware,KiCad,Pcbnew,6.0.0*%

2 | %TF.CreationDate,2022-02-18T00:32:39-05:00*%

3 | %TF.ProjectId,picocart,7069636f-6361-4727-942e-6b696361645f,rev?*%

4 | %TF.SameCoordinates,Original*%

5 | %TF.FileFunction,Paste,Bot*%

6 | %TF.FilePolarity,Positive*%

7 | %FSLAX46Y46*%

8 | G04 Gerber Fmt 4.6, Leading zero omitted, Abs format (unit mm)*

9 | G04 Created by KiCad (PCBNEW 6.0.0) date 2022-02-18 00:32:39*

10 | %MOMM*%

11 | %LPD*%

12 | G01*

13 | G04 APERTURE LIST*

14 | G04 APERTURE END LIST*

15 | M02*

16 |

--------------------------------------------------------------------------------

/pcb/gerber/picocart-B_Silkscreen.gbo:

--------------------------------------------------------------------------------

1 | %TF.GenerationSoftware,KiCad,Pcbnew,6.0.0*%

2 | %TF.CreationDate,2022-02-18T00:32:39-05:00*%

3 | %TF.ProjectId,picocart,7069636f-6361-4727-942e-6b696361645f,rev?*%

4 | %TF.SameCoordinates,Original*%

5 | %TF.FileFunction,Legend,Bot*%

6 | %TF.FilePolarity,Positive*%

7 | %FSLAX46Y46*%

8 | G04 Gerber Fmt 4.6, Leading zero omitted, Abs format (unit mm)*

9 | G04 Created by KiCad (PCBNEW 6.0.0) date 2022-02-18 00:32:39*

10 | %MOMM*%

11 | %LPD*%

12 | G01*

13 | G04 APERTURE LIST*

14 | %ADD10O,1.700000X1.700000*%

15 | %ADD11R,1.700000X1.700000*%

16 | %ADD12C,5.000000*%

17 | %ADD13R,1.524000X8.316000*%

18 | G04 APERTURE END LIST*

19 | %LPC*%

20 | %TO.C,J1*%

21 | G36*

22 | X175318000Y-107354200D02*

23 | G01*

24 | X118306000Y-107354200D01*

25 | X118306000Y-98819800D01*

26 | X175318000Y-98819800D01*

27 | X175318000Y-107354200D01*

28 | G37*

29 | %TD*%

30 | D10*

31 | %TO.C,SW1*%

32 | X121412000Y-62992000D03*

33 | X121412000Y-60452000D03*

34 | D11*

35 | X121412000Y-57912000D03*

36 | %TD*%

37 | D10*

38 | %TO.C,J2*%

39 | X171958000Y-47470000D03*

40 | X171958000Y-50010000D03*

41 | D11*

42 | X171958000Y-52550000D03*

43 | D10*

44 | X171958000Y-55090000D03*

45 | X171958000Y-57630000D03*

46 | X171958000Y-60170000D03*

47 | X171958000Y-62710000D03*

48 | D11*

49 | X171958000Y-65250000D03*

50 | D10*

51 | X171958000Y-67790000D03*

52 | X171958000Y-70330000D03*

53 | X171958000Y-72870000D03*

54 | X171958000Y-75410000D03*

55 | D11*

56 | X171958000Y-77950000D03*

57 | D10*

58 | X171958000Y-80490000D03*

59 | X171958000Y-83030000D03*

60 | X171958000Y-85570000D03*

61 | X171958000Y-88110000D03*

62 | D11*

63 | X171958000Y-90650000D03*

64 | D10*

65 | X171958000Y-93190000D03*

66 | X171958000Y-95730000D03*

67 | X154178000Y-95730000D03*

68 | X154178000Y-93190000D03*

69 | D11*

70 | X154178000Y-90650000D03*

71 | D10*

72 | X154178000Y-88110000D03*

73 | X154178000Y-85570000D03*

74 | X154178000Y-83030000D03*

75 | X154178000Y-80490000D03*

76 | D11*

77 | X154178000Y-77950000D03*

78 | D10*

79 | X154178000Y-75410000D03*

80 | X154178000Y-72870000D03*

81 | X154178000Y-70330000D03*

82 | X154178000Y-67790000D03*

83 | D11*

84 | X154178000Y-65250000D03*

85 | D10*

86 | X154178000Y-62710000D03*

87 | X154178000Y-60170000D03*

88 | X154178000Y-57630000D03*

89 | X154178000Y-55090000D03*

90 | D11*

91 | X154178000Y-52550000D03*

92 | D10*

93 | X154178000Y-50010000D03*

94 | X154178000Y-47470000D03*

95 | %TD*%

96 | D12*

97 | %TO.C,REF\u002A\u002A*%

98 | X146810000Y-65040000D03*

99 | %TD*%

100 | D13*

101 | %TO.C,J1*%

102 | X120142000Y-102977800D03*

103 | X122682000Y-102977800D03*

104 | X125222000Y-102977800D03*

105 | X127762000Y-102977800D03*

106 | X130302000Y-102977800D03*

107 | X132842000Y-102977800D03*

108 | X135382000Y-102977800D03*

109 | X137922000Y-102977800D03*

110 | X140462000Y-102977800D03*

111 | X143002000Y-102977800D03*

112 | X145542000Y-102977800D03*

113 | X148082000Y-102977800D03*

114 | X150622000Y-102977800D03*

115 | X153162000Y-102977800D03*

116 | X155702000Y-102977800D03*

117 | X158242000Y-102977800D03*

118 | X160782000Y-102977800D03*

119 | X163322000Y-102977800D03*

120 | X165862000Y-102977800D03*

121 | X168402000Y-102977800D03*

122 | X170942000Y-102977800D03*

123 | X173482000Y-102977800D03*

124 | %TD*%

125 | M02*

126 |

--------------------------------------------------------------------------------

/pcb/gerber/picocart-Edge_Cuts.gm1:

--------------------------------------------------------------------------------

1 | %TF.GenerationSoftware,KiCad,Pcbnew,6.0.0*%

2 | %TF.CreationDate,2022-02-18T00:32:39-05:00*%

3 | %TF.ProjectId,picocart,7069636f-6361-4727-942e-6b696361645f,rev?*%

4 | %TF.SameCoordinates,Original*%

5 | %TF.FileFunction,Profile,NP*%

6 | %FSLAX46Y46*%

7 | G04 Gerber Fmt 4.6, Leading zero omitted, Abs format (unit mm)*

8 | G04 Created by KiCad (PCBNEW 6.0.0) date 2022-02-18 00:32:39*

9 | %MOMM*%

10 | %LPD*%

11 | G01*

12 | G04 APERTURE LIST*

13 | %TA.AperFunction,Profile*%

14 | %ADD10C,0.050000*%

15 | %TD*%

16 | G04 APERTURE END LIST*

17 | D10*

18 | X175312000Y-107336000D02*

19 | X118312000Y-107336000D01*

20 | X118312000Y-107336000D02*

21 | X118312000Y-45336000D01*

22 | X118312000Y-45336000D02*

23 | X175312000Y-45336000D01*

24 | X175312000Y-45336000D02*

25 | X175312000Y-107336000D01*

26 | M02*

27 |

--------------------------------------------------------------------------------

/pcb/gerber/picocart-F_Mask.gts:

--------------------------------------------------------------------------------

1 | %TF.GenerationSoftware,KiCad,Pcbnew,6.0.0*%

2 | %TF.CreationDate,2022-02-18T00:32:39-05:00*%

3 | %TF.ProjectId,picocart,7069636f-6361-4727-942e-6b696361645f,rev?*%

4 | %TF.SameCoordinates,Original*%

5 | %TF.FileFunction,Soldermask,Top*%

6 | %TF.FilePolarity,Negative*%

7 | %FSLAX46Y46*%

8 | G04 Gerber Fmt 4.6, Leading zero omitted, Abs format (unit mm)*

9 | G04 Created by KiCad (PCBNEW 6.0.0) date 2022-02-18 00:32:39*

10 | %MOMM*%

11 | %LPD*%

12 | G01*

13 | G04 APERTURE LIST*

14 | G04 Aperture macros list*

15 | %AMRoundRect*

16 | 0 Rectangle with rounded corners*

17 | 0 $1 Rounding radius*

18 | 0 $2 $3 $4 $5 $6 $7 $8 $9 X,Y pos of 4 corners*

19 | 0 Add a 4 corners polygon primitive as box body*

20 | 4,1,4,$2,$3,$4,$5,$6,$7,$8,$9,$2,$3,0*

21 | 0 Add four circle primitives for the rounded corners*

22 | 1,1,$1+$1,$2,$3*

23 | 1,1,$1+$1,$4,$5*

24 | 1,1,$1+$1,$6,$7*

25 | 1,1,$1+$1,$8,$9*

26 | 0 Add four rect primitives between the rounded corners*

27 | 20,1,$1+$1,$2,$3,$4,$5,0*

28 | 20,1,$1+$1,$4,$5,$6,$7,0*

29 | 20,1,$1+$1,$6,$7,$8,$9,0*

30 | 20,1,$1+$1,$8,$9,$2,$3,0*%

31 | G04 Aperture macros list end*

32 | %ADD10O,1.700000X1.700000*%

33 | %ADD11R,1.700000X1.700000*%

34 | %ADD12R,2.500000X1.800000*%

35 | %ADD13R,3.500000X1.700000*%

36 | %ADD14C,5.000000*%

37 | %ADD15RoundRect,0.237500X-0.250000X-0.237500X0.250000X-0.237500X0.250000X0.237500X-0.250000X0.237500X0*%

38 | %ADD16RoundRect,0.237500X0.300000X0.237500X-0.300000X0.237500X-0.300000X-0.237500X0.300000X-0.237500X0*%

39 | %ADD17R,1.475000X0.450000*%

40 | %ADD18RoundRect,0.237500X0.250000X0.237500X-0.250000X0.237500X-0.250000X-0.237500X0.250000X-0.237500X0*%

41 | %ADD19R,1.524000X8.316000*%

42 | G04 APERTURE END LIST*

43 | %TO.C,J1*%

44 | G36*

45 | X175314000Y-107354200D02*

46 | G01*

47 | X118312000Y-107354200D01*

48 | X118312000Y-98819800D01*

49 | X175314000Y-98819800D01*

50 | X175314000Y-107354200D01*

51 | G37*

52 | %TD*%

53 | D10*

54 | %TO.C,SW1*%

55 | X121412000Y-62992000D03*

56 | X121412000Y-60452000D03*

57 | D11*

58 | X121412000Y-57912000D03*

59 | %TD*%

60 | D12*

61 | %TO.C,D1*%

62 | X142018000Y-47498000D03*

63 | X146018000Y-47498000D03*

64 | %TD*%

65 | D10*

66 | %TO.C,J2*%

67 | X171958000Y-47470000D03*

68 | D13*

69 | X172858000Y-47470000D03*

70 | X172858000Y-50010000D03*

71 | D10*

72 | X171958000Y-50010000D03*

73 | D11*

74 | X171958000Y-52550000D03*

75 | D13*

76 | X172858000Y-52550000D03*

77 | D10*

78 | X171958000Y-55090000D03*

79 | D13*

80 | X172858000Y-55090000D03*

81 | X172858000Y-57630000D03*

82 | D10*

83 | X171958000Y-57630000D03*

84 | X171958000Y-60170000D03*

85 | D13*

86 | X172858000Y-60170000D03*

87 | X172858000Y-62710000D03*

88 | D10*

89 | X171958000Y-62710000D03*

90 | D11*

91 | X171958000Y-65250000D03*

92 | D13*

93 | X172858000Y-65250000D03*

94 | D10*

95 | X171958000Y-67790000D03*

96 | D13*

97 | X172858000Y-67790000D03*

98 | D10*

99 | X171958000Y-70330000D03*

100 | D13*

101 | X172858000Y-70330000D03*

102 | X172858000Y-72870000D03*

103 | D10*

104 | X171958000Y-72870000D03*

105 | D13*

106 | X172858000Y-75410000D03*

107 | D10*

108 | X171958000Y-75410000D03*

109 | D13*

110 | X172858000Y-77950000D03*

111 | D11*

112 | X171958000Y-77950000D03*

113 | D10*

114 | X171958000Y-80490000D03*

115 | D13*

116 | X172858000Y-80490000D03*

117 | D10*

118 | X171958000Y-83030000D03*

119 | D13*

120 | X172858000Y-83030000D03*

121 | X172858000Y-85570000D03*

122 | D10*

123 | X171958000Y-85570000D03*

124 | X171958000Y-88110000D03*

125 | D13*

126 | X172858000Y-88110000D03*

127 | X172858000Y-90650000D03*

128 | D11*

129 | X171958000Y-90650000D03*

130 | D13*

131 | X172858000Y-93190000D03*

132 | D10*

133 | X171958000Y-93190000D03*

134 | D13*

135 | X172858000Y-95730000D03*

136 | D10*

137 | X171958000Y-95730000D03*

138 | D13*

139 | X153278000Y-95730000D03*

140 | D10*

141 | X154178000Y-95730000D03*

142 | X154178000Y-93190000D03*

143 | D13*

144 | X153278000Y-93190000D03*

145 | X153278000Y-90650000D03*

146 | D11*

147 | X154178000Y-90650000D03*

148 | D13*

149 | X153278000Y-88110000D03*

150 | D10*

151 | X154178000Y-88110000D03*

152 | X154178000Y-85570000D03*

153 | D13*

154 | X153278000Y-85570000D03*

155 | X153278000Y-83030000D03*

156 | D10*

157 | X154178000Y-83030000D03*

158 | D13*

159 | X153278000Y-80490000D03*

160 | D10*

161 | X154178000Y-80490000D03*

162 | D13*

163 | X153278000Y-77950000D03*

164 | D11*

165 | X154178000Y-77950000D03*

166 | D13*

167 | X153278000Y-75410000D03*

168 | D10*

169 | X154178000Y-75410000D03*

170 | D13*

171 | X153278000Y-72870000D03*

172 | D10*

173 | X154178000Y-72870000D03*

174 | D13*

175 | X153278000Y-70330000D03*

176 | D10*

177 | X154178000Y-70330000D03*

178 | D13*

179 | X153278000Y-67790000D03*

180 | D10*

181 | X154178000Y-67790000D03*

182 | D13*

183 | X153278000Y-65250000D03*

184 | D11*

185 | X154178000Y-65250000D03*

186 | D10*

187 | X154178000Y-62710000D03*

188 | D13*

189 | X153278000Y-62710000D03*

190 | X153278000Y-60170000D03*

191 | D10*

192 | X154178000Y-60170000D03*

193 | D13*

194 | X153278000Y-57630000D03*

195 | D10*

196 | X154178000Y-57630000D03*

197 | X154178000Y-55090000D03*

198 | D13*

199 | X153278000Y-55090000D03*

200 | D11*

201 | X154178000Y-52550000D03*

202 | D13*

203 | X153278000Y-52550000D03*

204 | D10*

205 | X154178000Y-50010000D03*

206 | D13*

207 | X153278000Y-50010000D03*

208 | X153278000Y-47470000D03*

209 | D10*

210 | X154178000Y-47470000D03*

211 | %TD*%

212 | D14*

213 | %TO.C,REF\u002A\u002A*%

214 | X146810000Y-65040000D03*

215 | %TD*%

216 | D15*

217 | %TO.C,R2*%

218 | X141073500Y-82042000D03*

219 | X142898500Y-82042000D03*

220 | %TD*%

221 | D16*

222 | %TO.C,C2*%

223 | X132942500Y-82042000D03*

224 | X131217500Y-82042000D03*

225 | %TD*%

226 | D17*

227 | %TO.C,U3*%

228 | X138921000Y-83689000D03*

229 | X138921000Y-84339000D03*

230 | X138921000Y-84989000D03*

231 | X138921000Y-85639000D03*

232 | X138921000Y-86289000D03*

233 | X138921000Y-86939000D03*

234 | X138921000Y-87589000D03*

235 | X138921000Y-88239000D03*

236 | X138921000Y-88889000D03*

237 | X138921000Y-89539000D03*

238 | X144797000Y-89539000D03*

239 | X144797000Y-88889000D03*

240 | X144797000Y-88239000D03*

241 | X144797000Y-87589000D03*

242 | X144797000Y-86939000D03*

243 | X144797000Y-86289000D03*

244 | X144797000Y-85639000D03*

245 | X144797000Y-84989000D03*

246 | X144797000Y-84339000D03*

247 | X144797000Y-83689000D03*

248 | %TD*%

249 | D16*

250 | %TO.C,C1*%

251 | X132942500Y-66294000D03*

252 | X131217500Y-66294000D03*

253 | %TD*%

254 | D17*

255 | %TO.C,U2*%

256 | X125078000Y-83689000D03*

257 | X125078000Y-84339000D03*

258 | X125078000Y-84989000D03*

259 | X125078000Y-85639000D03*

260 | X125078000Y-86289000D03*

261 | X125078000Y-86939000D03*

262 | X125078000Y-87589000D03*

263 | X125078000Y-88239000D03*

264 | X125078000Y-88889000D03*

265 | X125078000Y-89539000D03*

266 | X130954000Y-89539000D03*

267 | X130954000Y-88889000D03*

268 | X130954000Y-88239000D03*

269 | X130954000Y-87589000D03*

270 | X130954000Y-86939000D03*

271 | X130954000Y-86289000D03*

272 | X130954000Y-85639000D03*

273 | X130954000Y-84989000D03*

274 | X130954000Y-84339000D03*

275 | X130954000Y-83689000D03*

276 | %TD*%

277 | D18*

278 | %TO.C,R1*%

279 | X128928500Y-66294000D03*

280 | X127103500Y-66294000D03*

281 | %TD*%

282 | D19*

283 | %TO.C,J1*%

284 | X120142000Y-102977800D03*

285 | X122682000Y-102977800D03*

286 | X125222000Y-102977800D03*

287 | X127762000Y-102977800D03*

288 | X130302000Y-102977800D03*

289 | X132842000Y-102977800D03*

290 | X135382000Y-102977800D03*

291 | X137922000Y-102977800D03*

292 | X140462000Y-102977800D03*

293 | X143002000Y-102977800D03*

294 | X145542000Y-102977800D03*

295 | X148082000Y-102977800D03*

296 | X150622000Y-102977800D03*

297 | X153162000Y-102977800D03*

298 | X155702000Y-102977800D03*

299 | X158242000Y-102977800D03*

300 | X160782000Y-102977800D03*

301 | X163322000Y-102977800D03*

302 | X165862000Y-102977800D03*

303 | X168402000Y-102977800D03*

304 | X170942000Y-102977800D03*

305 | X173482000Y-102977800D03*

306 | %TD*%

307 | D16*

308 | %TO.C,C3*%

309 | X146912500Y-82042000D03*

310 | X145187500Y-82042000D03*

311 | %TD*%

312 | D17*

313 | %TO.C,U1*%

314 | X125078000Y-67941000D03*

315 | X125078000Y-68591000D03*

316 | X125078000Y-69241000D03*

317 | X125078000Y-69891000D03*

318 | X125078000Y-70541000D03*

319 | X125078000Y-71191000D03*

320 | X125078000Y-71841000D03*

321 | X125078000Y-72491000D03*

322 | X125078000Y-73141000D03*

323 | X125078000Y-73791000D03*

324 | X130954000Y-73791000D03*

325 | X130954000Y-73141000D03*

326 | X130954000Y-72491000D03*

327 | X130954000Y-71841000D03*

328 | X130954000Y-71191000D03*

329 | X130954000Y-70541000D03*

330 | X130954000Y-69891000D03*

331 | X130954000Y-69241000D03*

332 | X130954000Y-68591000D03*

333 | X130954000Y-67941000D03*

334 | %TD*%

335 | M02*

336 |

--------------------------------------------------------------------------------

/pcb/gerber/picocart-F_Paste.gtp:

--------------------------------------------------------------------------------

1 | %TF.GenerationSoftware,KiCad,Pcbnew,6.0.0*%

2 | %TF.CreationDate,2022-02-18T00:32:38-05:00*%

3 | %TF.ProjectId,picocart,7069636f-6361-4727-942e-6b696361645f,rev?*%

4 | %TF.SameCoordinates,Original*%

5 | %TF.FileFunction,Paste,Top*%

6 | %TF.FilePolarity,Positive*%

7 | %FSLAX46Y46*%

8 | G04 Gerber Fmt 4.6, Leading zero omitted, Abs format (unit mm)*

9 | G04 Created by KiCad (PCBNEW 6.0.0) date 2022-02-18 00:32:38*

10 | %MOMM*%

11 | %LPD*%

12 | G01*

13 | G04 APERTURE LIST*

14 | G04 Aperture macros list*

15 | %AMRoundRect*

16 | 0 Rectangle with rounded corners*

17 | 0 $1 Rounding radius*

18 | 0 $2 $3 $4 $5 $6 $7 $8 $9 X,Y pos of 4 corners*

19 | 0 Add a 4 corners polygon primitive as box body*

20 | 4,1,4,$2,$3,$4,$5,$6,$7,$8,$9,$2,$3,0*

21 | 0 Add four circle primitives for the rounded corners*

22 | 1,1,$1+$1,$2,$3*

23 | 1,1,$1+$1,$4,$5*

24 | 1,1,$1+$1,$6,$7*

25 | 1,1,$1+$1,$8,$9*

26 | 0 Add four rect primitives between the rounded corners*

27 | 20,1,$1+$1,$2,$3,$4,$5,0*

28 | 20,1,$1+$1,$4,$5,$6,$7,0*

29 | 20,1,$1+$1,$6,$7,$8,$9,0*

30 | 20,1,$1+$1,$8,$9,$2,$3,0*%

31 | G04 Aperture macros list end*

32 | %ADD10R,2.500000X1.800000*%

33 | %ADD11RoundRect,0.237500X-0.250000X-0.237500X0.250000X-0.237500X0.250000X0.237500X-0.250000X0.237500X0*%

34 | %ADD12RoundRect,0.237500X0.300000X0.237500X-0.300000X0.237500X-0.300000X-0.237500X0.300000X-0.237500X0*%

35 | %ADD13R,1.475000X0.450000*%

36 | %ADD14RoundRect,0.237500X0.250000X0.237500X-0.250000X0.237500X-0.250000X-0.237500X0.250000X-0.237500X0*%

37 | G04 APERTURE END LIST*

38 | D10*

39 | %TO.C,D1*%

40 | X142018000Y-47498000D03*

41 | X146018000Y-47498000D03*

42 | %TD*%

43 | D11*

44 | %TO.C,R2*%

45 | X141073500Y-82042000D03*

46 | X142898500Y-82042000D03*

47 | %TD*%

48 | D12*

49 | %TO.C,C2*%

50 | X132942500Y-82042000D03*

51 | X131217500Y-82042000D03*

52 | %TD*%

53 | D13*

54 | %TO.C,U3*%

55 | X138921000Y-83689000D03*

56 | X138921000Y-84339000D03*

57 | X138921000Y-84989000D03*

58 | X138921000Y-85639000D03*

59 | X138921000Y-86289000D03*

60 | X138921000Y-86939000D03*

61 | X138921000Y-87589000D03*

62 | X138921000Y-88239000D03*

63 | X138921000Y-88889000D03*

64 | X138921000Y-89539000D03*

65 | X144797000Y-89539000D03*

66 | X144797000Y-88889000D03*

67 | X144797000Y-88239000D03*

68 | X144797000Y-87589000D03*

69 | X144797000Y-86939000D03*

70 | X144797000Y-86289000D03*

71 | X144797000Y-85639000D03*

72 | X144797000Y-84989000D03*

73 | X144797000Y-84339000D03*

74 | X144797000Y-83689000D03*

75 | %TD*%

76 | D12*

77 | %TO.C,C1*%

78 | X132942500Y-66294000D03*

79 | X131217500Y-66294000D03*

80 | %TD*%

81 | D13*

82 | %TO.C,U2*%

83 | X125078000Y-83689000D03*

84 | X125078000Y-84339000D03*

85 | X125078000Y-84989000D03*

86 | X125078000Y-85639000D03*

87 | X125078000Y-86289000D03*

88 | X125078000Y-86939000D03*

89 | X125078000Y-87589000D03*

90 | X125078000Y-88239000D03*

91 | X125078000Y-88889000D03*

92 | X125078000Y-89539000D03*

93 | X130954000Y-89539000D03*

94 | X130954000Y-88889000D03*

95 | X130954000Y-88239000D03*

96 | X130954000Y-87589000D03*

97 | X130954000Y-86939000D03*

98 | X130954000Y-86289000D03*

99 | X130954000Y-85639000D03*

100 | X130954000Y-84989000D03*

101 | X130954000Y-84339000D03*

102 | X130954000Y-83689000D03*

103 | %TD*%

104 | D14*

105 | %TO.C,R1*%

106 | X128928500Y-66294000D03*

107 | X127103500Y-66294000D03*

108 | %TD*%

109 | D12*

110 | %TO.C,C3*%

111 | X146912500Y-82042000D03*

112 | X145187500Y-82042000D03*

113 | %TD*%

114 | D13*

115 | %TO.C,U1*%

116 | X125078000Y-67941000D03*

117 | X125078000Y-68591000D03*

118 | X125078000Y-69241000D03*

119 | X125078000Y-69891000D03*

120 | X125078000Y-70541000D03*

121 | X125078000Y-71191000D03*

122 | X125078000Y-71841000D03*

123 | X125078000Y-72491000D03*

124 | X125078000Y-73141000D03*

125 | X125078000Y-73791000D03*

126 | X130954000Y-73791000D03*

127 | X130954000Y-73141000D03*

128 | X130954000Y-72491000D03*

129 | X130954000Y-71841000D03*

130 | X130954000Y-71191000D03*

131 | X130954000Y-70541000D03*

132 | X130954000Y-69891000D03*

133 | X130954000Y-69241000D03*

134 | X130954000Y-68591000D03*

135 | X130954000Y-67941000D03*

136 | %TD*%

137 | M02*

138 |

--------------------------------------------------------------------------------

/pcb/gerber/picocart-NPTH-drl_map.gbr:

--------------------------------------------------------------------------------

1 | %FSLAX45Y45*%

2 | G04 Gerber Fmt 4.5, Leading zero omitted, Abs format (unit mm)*

3 | G04 Created by KiCad (PCBNEW 6.0.0) date 2022-02-18 00:33:37*

4 | %MOMM*%

5 | %LPD*%

6 | G01*

7 | G04 APERTURE LIST*

8 | %TA.AperFunction,Profile*%

9 | %ADD10C,0.050000*%

10 | %TD*%

11 | %ADD11C,0.200000*%

12 | %ADD12C,0.500000*%

13 | G04 APERTURE END LIST*

14 | D10*

15 | X17531200Y-10733600D02*

16 | X11831200Y-10733600D01*

17 | X11831200Y-10733600D02*

18 | X11831200Y-4533600D01*

19 | X11831200Y-4533600D02*

20 | X17531200Y-4533600D01*

21 | X17531200Y-4533600D02*

22 | X17531200Y-10733600D01*

23 | D11*

24 | D12*

25 | X14431000Y-6254000D02*

26 | X14931000Y-6754000D01*

27 | X14931000Y-6254000D02*

28 | X14431000Y-6754000D01*

29 | D11*

30 | X12086319Y-11046576D02*

31 | X12086319Y-10846576D01*

32 | X12133938Y-10846576D01*

33 | X12162509Y-10856100D01*

34 | X12181557Y-10875148D01*

35 | X12191081Y-10894195D01*

36 | X12200605Y-10932290D01*

37 | X12200605Y-10960862D01*

38 | X12191081Y-10998957D01*

39 | X12181557Y-11018005D01*