├── LICENSE

├── README.md

├── images

├── banner.png

├── image1.jpg

├── image2.jpg

├── image3.jpg

├── image4.jpg

├── image5.jpg

├── image6.jpg

├── image7.jpg

└── pci2nano.gif

├── pci2nano-cache.lib

├── pci2nano.kicad_pcb

├── pci2nano.net

├── pci2nano.pro

├── pci2nano.qpf

├── pci2nano.qsf

├── pci2nano.sch

└── pci2nano.v

/LICENSE:

--------------------------------------------------------------------------------

1 | Attribution-ShareAlike 4.0 International

2 |

3 | =======================================================================

4 |

5 | Creative Commons Corporation ("Creative Commons") is not a law firm and

6 | does not provide legal services or legal advice. Distribution of

7 | Creative Commons public licenses does not create a lawyer-client or

8 | other relationship. Creative Commons makes its licenses and related

9 | information available on an "as-is" basis. Creative Commons gives no

10 | warranties regarding its licenses, any material licensed under their

11 | terms and conditions, or any related information. Creative Commons

12 | disclaims all liability for damages resulting from their use to the

13 | fullest extent possible.

14 |

15 | Using Creative Commons Public Licenses

16 |

17 | Creative Commons public licenses provide a standard set of terms and

18 | conditions that creators and other rights holders may use to share

19 | original works of authorship and other material subject to copyright

20 | and certain other rights specified in the public license below. The

21 | following considerations are for informational purposes only, are not

22 | exhaustive, and do not form part of our licenses.

23 |

24 | Considerations for licensors: Our public licenses are

25 | intended for use by those authorized to give the public

26 | permission to use material in ways otherwise restricted by

27 | copyright and certain other rights. Our licenses are

28 | irrevocable. Licensors should read and understand the terms

29 | and conditions of the license they choose before applying it.

30 | Licensors should also secure all rights necessary before

31 | applying our licenses so that the public can reuse the

32 | material as expected. Licensors should clearly mark any

33 | material not subject to the license. This includes other CC-

34 | licensed material, or material used under an exception or

35 | limitation to copyright. More considerations for licensors:

36 | wiki.creativecommons.org/Considerations_for_licensors

37 |

38 | Considerations for the public: By using one of our public

39 | licenses, a licensor grants the public permission to use the

40 | licensed material under specified terms and conditions. If

41 | the licensor's permission is not necessary for any reason--for

42 | example, because of any applicable exception or limitation to

43 | copyright--then that use is not regulated by the license. Our

44 | licenses grant only permissions under copyright and certain

45 | other rights that a licensor has authority to grant. Use of

46 | the licensed material may still be restricted for other

47 | reasons, including because others have copyright or other

48 | rights in the material. A licensor may make special requests,

49 | such as asking that all changes be marked or described.

50 | Although not required by our licenses, you are encouraged to

51 | respect those requests where reasonable. More considerations

52 | for the public:

53 | wiki.creativecommons.org/Considerations_for_licensees

54 |

55 | =======================================================================

56 |

57 | Creative Commons Attribution-ShareAlike 4.0 International Public

58 | License

59 |

60 | By exercising the Licensed Rights (defined below), You accept and agree

61 | to be bound by the terms and conditions of this Creative Commons

62 | Attribution-ShareAlike 4.0 International Public License ("Public

63 | License"). To the extent this Public License may be interpreted as a

64 | contract, You are granted the Licensed Rights in consideration of Your

65 | acceptance of these terms and conditions, and the Licensor grants You

66 | such rights in consideration of benefits the Licensor receives from

67 | making the Licensed Material available under these terms and

68 | conditions.

69 |

70 |

71 | Section 1 -- Definitions.

72 |

73 | a. Adapted Material means material subject to Copyright and Similar

74 | Rights that is derived from or based upon the Licensed Material

75 | and in which the Licensed Material is translated, altered,

76 | arranged, transformed, or otherwise modified in a manner requiring

77 | permission under the Copyright and Similar Rights held by the

78 | Licensor. For purposes of this Public License, where the Licensed

79 | Material is a musical work, performance, or sound recording,

80 | Adapted Material is always produced where the Licensed Material is

81 | synched in timed relation with a moving image.

82 |

83 | b. Adapter's License means the license You apply to Your Copyright

84 | and Similar Rights in Your contributions to Adapted Material in

85 | accordance with the terms and conditions of this Public License.

86 |

87 | c. BY-SA Compatible License means a license listed at

88 | creativecommons.org/compatiblelicenses, approved by Creative

89 | Commons as essentially the equivalent of this Public License.

90 |

91 | d. Copyright and Similar Rights means copyright and/or similar rights

92 | closely related to copyright including, without limitation,

93 | performance, broadcast, sound recording, and Sui Generis Database

94 | Rights, without regard to how the rights are labeled or

95 | categorized. For purposes of this Public License, the rights

96 | specified in Section 2(b)(1)-(2) are not Copyright and Similar

97 | Rights.

98 |

99 | e. Effective Technological Measures means those measures that, in the

100 | absence of proper authority, may not be circumvented under laws

101 | fulfilling obligations under Article 11 of the WIPO Copyright

102 | Treaty adopted on December 20, 1996, and/or similar international

103 | agreements.

104 |

105 | f. Exceptions and Limitations means fair use, fair dealing, and/or

106 | any other exception or limitation to Copyright and Similar Rights

107 | that applies to Your use of the Licensed Material.

108 |

109 | g. License Elements means the license attributes listed in the name

110 | of a Creative Commons Public License. The License Elements of this

111 | Public License are Attribution and ShareAlike.

112 |

113 | h. Licensed Material means the artistic or literary work, database,

114 | or other material to which the Licensor applied this Public

115 | License.

116 |

117 | i. Licensed Rights means the rights granted to You subject to the

118 | terms and conditions of this Public License, which are limited to

119 | all Copyright and Similar Rights that apply to Your use of the

120 | Licensed Material and that the Licensor has authority to license.

121 |

122 | j. Licensor means the individual(s) or entity(ies) granting rights

123 | under this Public License.

124 |

125 | k. Share means to provide material to the public by any means or

126 | process that requires permission under the Licensed Rights, such

127 | as reproduction, public display, public performance, distribution,

128 | dissemination, communication, or importation, and to make material

129 | available to the public including in ways that members of the

130 | public may access the material from a place and at a time

131 | individually chosen by them.

132 |

133 | l. Sui Generis Database Rights means rights other than copyright

134 | resulting from Directive 96/9/EC of the European Parliament and of

135 | the Council of 11 March 1996 on the legal protection of databases,

136 | as amended and/or succeeded, as well as other essentially

137 | equivalent rights anywhere in the world.

138 |

139 | m. You means the individual or entity exercising the Licensed Rights

140 | under this Public License. Your has a corresponding meaning.

141 |

142 |

143 | Section 2 -- Scope.

144 |

145 | a. License grant.

146 |

147 | 1. Subject to the terms and conditions of this Public License,

148 | the Licensor hereby grants You a worldwide, royalty-free,

149 | non-sublicensable, non-exclusive, irrevocable license to

150 | exercise the Licensed Rights in the Licensed Material to:

151 |

152 | a. reproduce and Share the Licensed Material, in whole or

153 | in part; and

154 |

155 | b. produce, reproduce, and Share Adapted Material.

156 |

157 | 2. Exceptions and Limitations. For the avoidance of doubt, where

158 | Exceptions and Limitations apply to Your use, this Public

159 | License does not apply, and You do not need to comply with

160 | its terms and conditions.

161 |

162 | 3. Term. The term of this Public License is specified in Section

163 | 6(a).

164 |

165 | 4. Media and formats; technical modifications allowed. The

166 | Licensor authorizes You to exercise the Licensed Rights in

167 | all media and formats whether now known or hereafter created,

168 | and to make technical modifications necessary to do so. The

169 | Licensor waives and/or agrees not to assert any right or

170 | authority to forbid You from making technical modifications

171 | necessary to exercise the Licensed Rights, including

172 | technical modifications necessary to circumvent Effective

173 | Technological Measures. For purposes of this Public License,

174 | simply making modifications authorized by this Section 2(a)

175 | (4) never produces Adapted Material.

176 |

177 | 5. Downstream recipients.

178 |

179 | a. Offer from the Licensor -- Licensed Material. Every

180 | recipient of the Licensed Material automatically

181 | receives an offer from the Licensor to exercise the

182 | Licensed Rights under the terms and conditions of this

183 | Public License.

184 |

185 | b. Additional offer from the Licensor -- Adapted Material.

186 | Every recipient of Adapted Material from You

187 | automatically receives an offer from the Licensor to

188 | exercise the Licensed Rights in the Adapted Material

189 | under the conditions of the Adapter's License You apply.

190 |

191 | c. No downstream restrictions. You may not offer or impose

192 | any additional or different terms or conditions on, or

193 | apply any Effective Technological Measures to, the

194 | Licensed Material if doing so restricts exercise of the

195 | Licensed Rights by any recipient of the Licensed

196 | Material.

197 |

198 | 6. No endorsement. Nothing in this Public License constitutes or

199 | may be construed as permission to assert or imply that You

200 | are, or that Your use of the Licensed Material is, connected

201 | with, or sponsored, endorsed, or granted official status by,

202 | the Licensor or others designated to receive attribution as

203 | provided in Section 3(a)(1)(A)(i).

204 |

205 | b. Other rights.

206 |

207 | 1. Moral rights, such as the right of integrity, are not

208 | licensed under this Public License, nor are publicity,

209 | privacy, and/or other similar personality rights; however, to

210 | the extent possible, the Licensor waives and/or agrees not to

211 | assert any such rights held by the Licensor to the limited

212 | extent necessary to allow You to exercise the Licensed

213 | Rights, but not otherwise.

214 |

215 | 2. Patent and trademark rights are not licensed under this

216 | Public License.

217 |

218 | 3. To the extent possible, the Licensor waives any right to

219 | collect royalties from You for the exercise of the Licensed

220 | Rights, whether directly or through a collecting society

221 | under any voluntary or waivable statutory or compulsory

222 | licensing scheme. In all other cases the Licensor expressly

223 | reserves any right to collect such royalties.

224 |

225 |

226 | Section 3 -- License Conditions.

227 |

228 | Your exercise of the Licensed Rights is expressly made subject to the

229 | following conditions.

230 |

231 | a. Attribution.

232 |

233 | 1. If You Share the Licensed Material (including in modified

234 | form), You must:

235 |

236 | a. retain the following if it is supplied by the Licensor

237 | with the Licensed Material:

238 |

239 | i. identification of the creator(s) of the Licensed

240 | Material and any others designated to receive

241 | attribution, in any reasonable manner requested by

242 | the Licensor (including by pseudonym if

243 | designated);

244 |

245 | ii. a copyright notice;

246 |

247 | iii. a notice that refers to this Public License;

248 |

249 | iv. a notice that refers to the disclaimer of

250 | warranties;

251 |

252 | v. a URI or hyperlink to the Licensed Material to the

253 | extent reasonably practicable;

254 |

255 | b. indicate if You modified the Licensed Material and

256 | retain an indication of any previous modifications; and

257 |

258 | c. indicate the Licensed Material is licensed under this

259 | Public License, and include the text of, or the URI or

260 | hyperlink to, this Public License.

261 |

262 | 2. You may satisfy the conditions in Section 3(a)(1) in any

263 | reasonable manner based on the medium, means, and context in

264 | which You Share the Licensed Material. For example, it may be

265 | reasonable to satisfy the conditions by providing a URI or

266 | hyperlink to a resource that includes the required

267 | information.

268 |

269 | 3. If requested by the Licensor, You must remove any of the

270 | information required by Section 3(a)(1)(A) to the extent

271 | reasonably practicable.

272 |

273 | b. ShareAlike.

274 |

275 | In addition to the conditions in Section 3(a), if You Share

276 | Adapted Material You produce, the following conditions also apply.

277 |

278 | 1. The Adapter's License You apply must be a Creative Commons

279 | license with the same License Elements, this version or

280 | later, or a BY-SA Compatible License.

281 |

282 | 2. You must include the text of, or the URI or hyperlink to, the

283 | Adapter's License You apply. You may satisfy this condition

284 | in any reasonable manner based on the medium, means, and

285 | context in which You Share Adapted Material.

286 |

287 | 3. You may not offer or impose any additional or different terms

288 | or conditions on, or apply any Effective Technological

289 | Measures to, Adapted Material that restrict exercise of the

290 | rights granted under the Adapter's License You apply.

291 |

292 |

293 | Section 4 -- Sui Generis Database Rights.

294 |

295 | Where the Licensed Rights include Sui Generis Database Rights that

296 | apply to Your use of the Licensed Material:

297 |

298 | a. for the avoidance of doubt, Section 2(a)(1) grants You the right

299 | to extract, reuse, reproduce, and Share all or a substantial

300 | portion of the contents of the database;

301 |

302 | b. if You include all or a substantial portion of the database

303 | contents in a database in which You have Sui Generis Database

304 | Rights, then the database in which You have Sui Generis Database

305 | Rights (but not its individual contents) is Adapted Material,

306 |

307 | including for purposes of Section 3(b); and

308 | c. You must comply with the conditions in Section 3(a) if You Share

309 | all or a substantial portion of the contents of the database.

310 |

311 | For the avoidance of doubt, this Section 4 supplements and does not

312 | replace Your obligations under this Public License where the Licensed

313 | Rights include other Copyright and Similar Rights.

314 |

315 |

316 | Section 5 -- Disclaimer of Warranties and Limitation of Liability.

317 |

318 | a. UNLESS OTHERWISE SEPARATELY UNDERTAKEN BY THE LICENSOR, TO THE

319 | EXTENT POSSIBLE, THE LICENSOR OFFERS THE LICENSED MATERIAL AS-IS

320 | AND AS-AVAILABLE, AND MAKES NO REPRESENTATIONS OR WARRANTIES OF

321 | ANY KIND CONCERNING THE LICENSED MATERIAL, WHETHER EXPRESS,

322 | IMPLIED, STATUTORY, OR OTHER. THIS INCLUDES, WITHOUT LIMITATION,

323 | WARRANTIES OF TITLE, MERCHANTABILITY, FITNESS FOR A PARTICULAR

324 | PURPOSE, NON-INFRINGEMENT, ABSENCE OF LATENT OR OTHER DEFECTS,

325 | ACCURACY, OR THE PRESENCE OR ABSENCE OF ERRORS, WHETHER OR NOT

326 | KNOWN OR DISCOVERABLE. WHERE DISCLAIMERS OF WARRANTIES ARE NOT

327 | ALLOWED IN FULL OR IN PART, THIS DISCLAIMER MAY NOT APPLY TO YOU.

328 |

329 | b. TO THE EXTENT POSSIBLE, IN NO EVENT WILL THE LICENSOR BE LIABLE

330 | TO YOU ON ANY LEGAL THEORY (INCLUDING, WITHOUT LIMITATION,

331 | NEGLIGENCE) OR OTHERWISE FOR ANY DIRECT, SPECIAL, INDIRECT,

332 | INCIDENTAL, CONSEQUENTIAL, PUNITIVE, EXEMPLARY, OR OTHER LOSSES,

333 | COSTS, EXPENSES, OR DAMAGES ARISING OUT OF THIS PUBLIC LICENSE OR

334 | USE OF THE LICENSED MATERIAL, EVEN IF THE LICENSOR HAS BEEN

335 | ADVISED OF THE POSSIBILITY OF SUCH LOSSES, COSTS, EXPENSES, OR

336 | DAMAGES. WHERE A LIMITATION OF LIABILITY IS NOT ALLOWED IN FULL OR

337 | IN PART, THIS LIMITATION MAY NOT APPLY TO YOU.

338 |

339 | c. The disclaimer of warranties and limitation of liability provided

340 | above shall be interpreted in a manner that, to the extent

341 | possible, most closely approximates an absolute disclaimer and

342 | waiver of all liability.

343 |

344 |

345 | Section 6 -- Term and Termination.

346 |

347 | a. This Public License applies for the term of the Copyright and

348 | Similar Rights licensed here. However, if You fail to comply with

349 | this Public License, then Your rights under this Public License

350 | terminate automatically.

351 |

352 | b. Where Your right to use the Licensed Material has terminated under

353 | Section 6(a), it reinstates:

354 |

355 | 1. automatically as of the date the violation is cured, provided

356 | it is cured within 30 days of Your discovery of the

357 | violation; or

358 |

359 | 2. upon express reinstatement by the Licensor.

360 |

361 | For the avoidance of doubt, this Section 6(b) does not affect any

362 | right the Licensor may have to seek remedies for Your violations

363 | of this Public License.

364 |

365 | c. For the avoidance of doubt, the Licensor may also offer the

366 | Licensed Material under separate terms or conditions or stop

367 | distributing the Licensed Material at any time; however, doing so

368 | will not terminate this Public License.

369 |

370 | d. Sections 1, 5, 6, 7, and 8 survive termination of this Public

371 | License.

372 |

373 |

374 | Section 7 -- Other Terms and Conditions.

375 |

376 | a. The Licensor shall not be bound by any additional or different

377 | terms or conditions communicated by You unless expressly agreed.

378 |

379 | b. Any arrangements, understandings, or agreements regarding the

380 | Licensed Material not stated herein are separate from and

381 | independent of the terms and conditions of this Public License.

382 |

383 |

384 | Section 8 -- Interpretation.

385 |

386 | a. For the avoidance of doubt, this Public License does not, and

387 | shall not be interpreted to, reduce, limit, restrict, or impose

388 | conditions on any use of the Licensed Material that could lawfully

389 | be made without permission under this Public License.

390 |

391 | b. To the extent possible, if any provision of this Public License is

392 | deemed unenforceable, it shall be automatically reformed to the

393 | minimum extent necessary to make it enforceable. If the provision

394 | cannot be reformed, it shall be severed from this Public License

395 | without affecting the enforceability of the remaining terms and

396 | conditions.

397 |

398 | c. No term or condition of this Public License will be waived and no

399 | failure to comply consented to unless expressly agreed to by the

400 | Licensor.

401 |

402 | d. Nothing in this Public License constitutes or may be interpreted

403 | as a limitation upon, or waiver of, any privileges and immunities

404 | that apply to the Licensor or You, including from the legal

405 | processes of any jurisdiction or authority.

406 |

407 |

408 | =======================================================================

409 |

410 | Creative Commons is not a party to its public

411 | licenses. Notwithstanding, Creative Commons may elect to apply one of

412 | its public licenses to material it publishes and in those instances

413 | will be considered the “Licensor.” The text of the Creative Commons

414 | public licenses is dedicated to the public domain under the CC0 Public

415 | Domain Dedication. Except for the limited purpose of indicating that

416 | material is shared under a Creative Commons public license or as

417 | otherwise permitted by the Creative Commons policies published at

418 | creativecommons.org/policies, Creative Commons does not authorize the

419 | use of the trademark "Creative Commons" or any other trademark or logo

420 | of Creative Commons without its prior written consent including,

421 | without limitation, in connection with any unauthorized modifications

422 | to any of its public licenses or any other arrangements,

423 | understandings, or agreements concerning use of licensed material. For

424 | the avoidance of doubt, this paragraph does not form part of the

425 | public licenses.

426 |

427 | Creative Commons may be contacted at creativecommons.org.

428 |

--------------------------------------------------------------------------------

/README.md:

--------------------------------------------------------------------------------

1 | # PCI2Nano Reference Platform

2 |

3 |  4 |

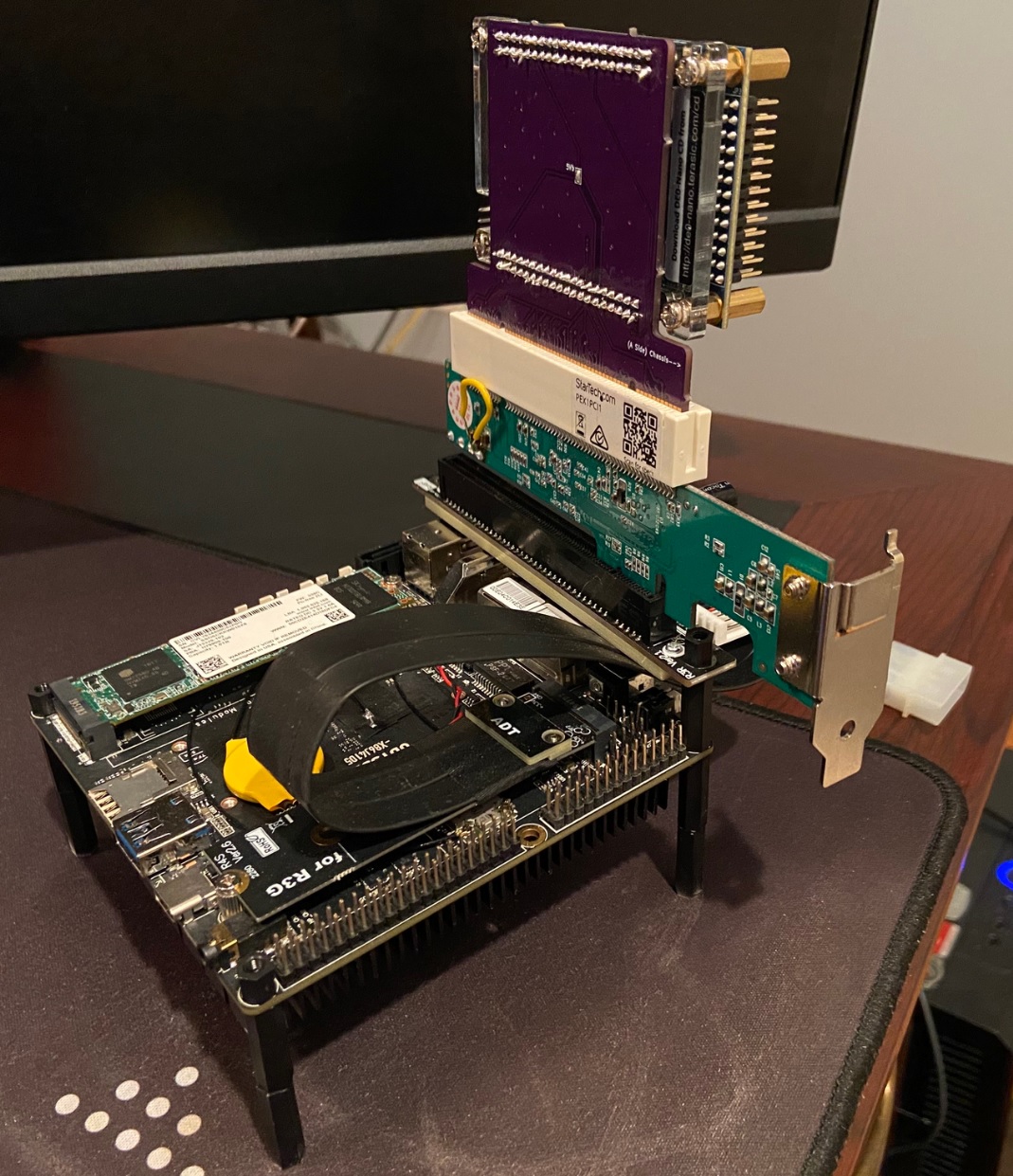

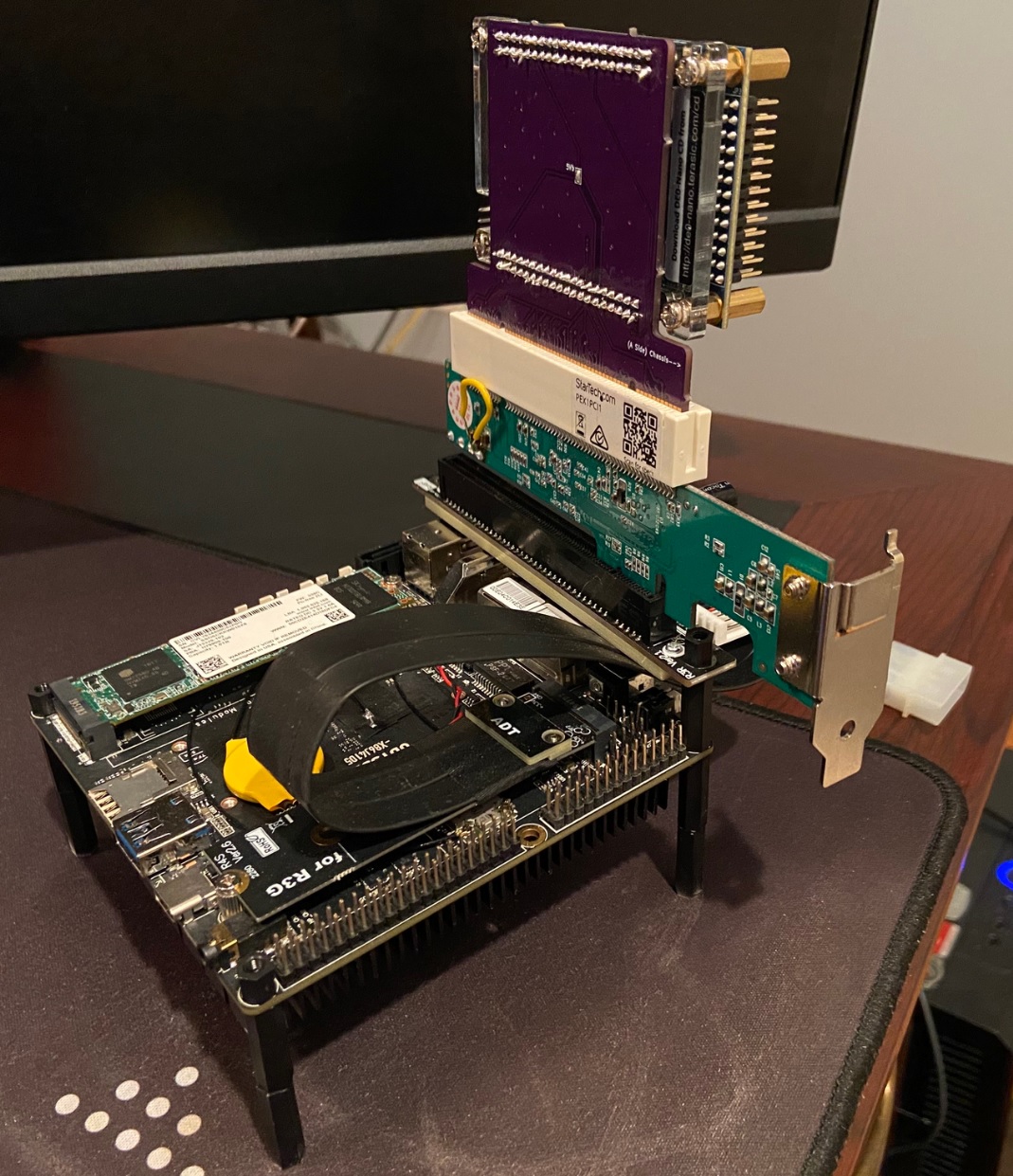

5 | Welcome to the PCI2Nano Reference Platform repo. In this repo you'll find an inexpensive suggested Reference Platform for designing and testing PCI functions on a DE0-Nano FPGA to an x86 host. I have personally built/connected/tested every single one of these components and can confirm they work for fast iterative PCI development.

6 |

7 | The design collateral that is included with this repo are the kicad design files for the PCI2Nano breakout board and a Quartus project that contains all the correct PCI pinout constraints for the PCI2Nano breakout board. This repo does not contain an actual PCI core written in verilog. For an example PCI core implementation with a UART check out the PCI2Nano-RTL repo here: https://github.com/defparam/PCI2Nano-RTL/

8 |

9 |

4 |

5 | Welcome to the PCI2Nano Reference Platform repo. In this repo you'll find an inexpensive suggested Reference Platform for designing and testing PCI functions on a DE0-Nano FPGA to an x86 host. I have personally built/connected/tested every single one of these components and can confirm they work for fast iterative PCI development.

6 |

7 | The design collateral that is included with this repo are the kicad design files for the PCI2Nano breakout board and a Quartus project that contains all the correct PCI pinout constraints for the PCI2Nano breakout board. This repo does not contain an actual PCI core written in verilog. For an example PCI core implementation with a UART check out the PCI2Nano-RTL repo here: https://github.com/defparam/PCI2Nano-RTL/

8 |

9 |

This work is licensed under a Creative Commons Attribution-ShareAlike 4.0 International License.

10 |

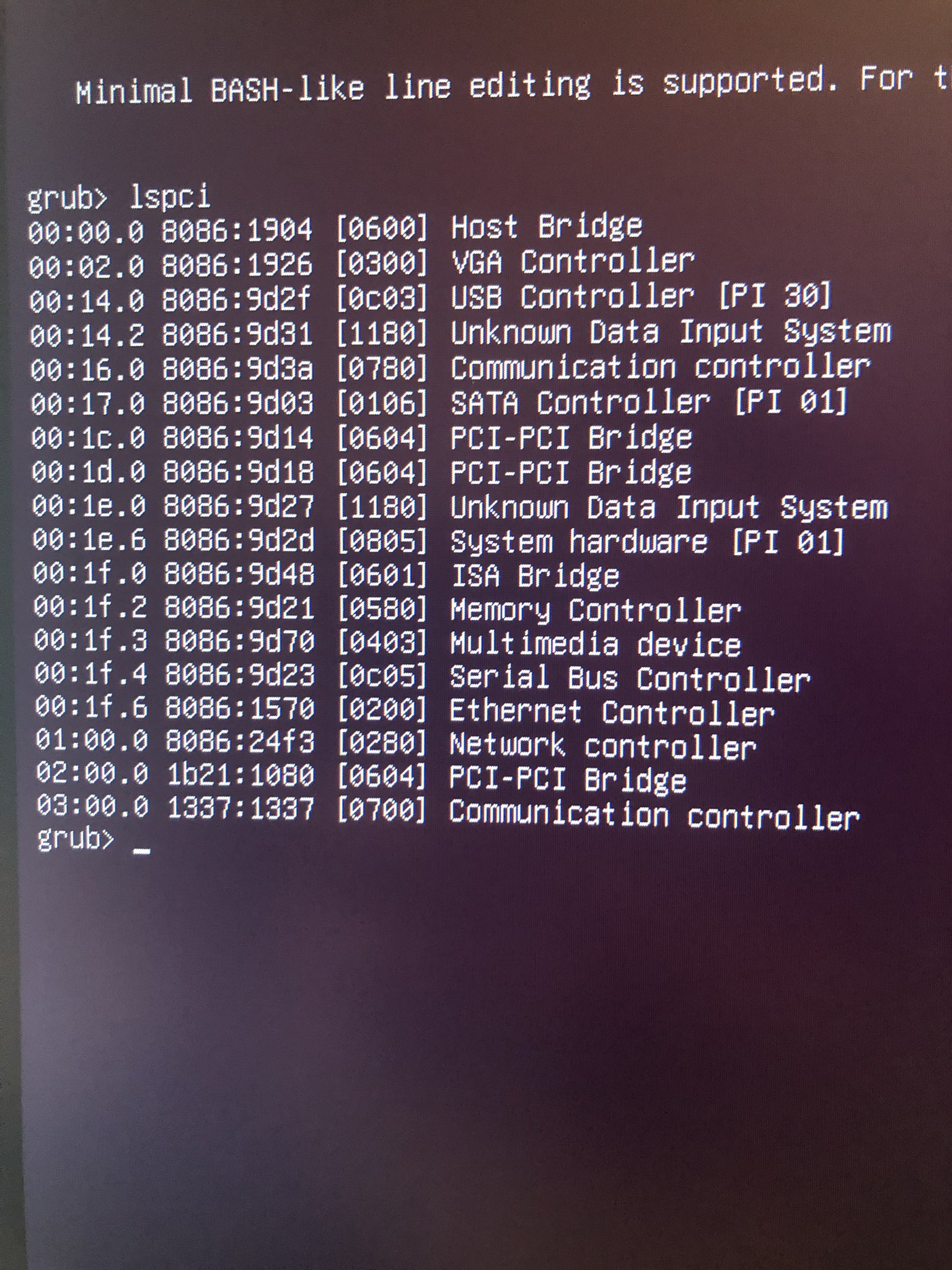

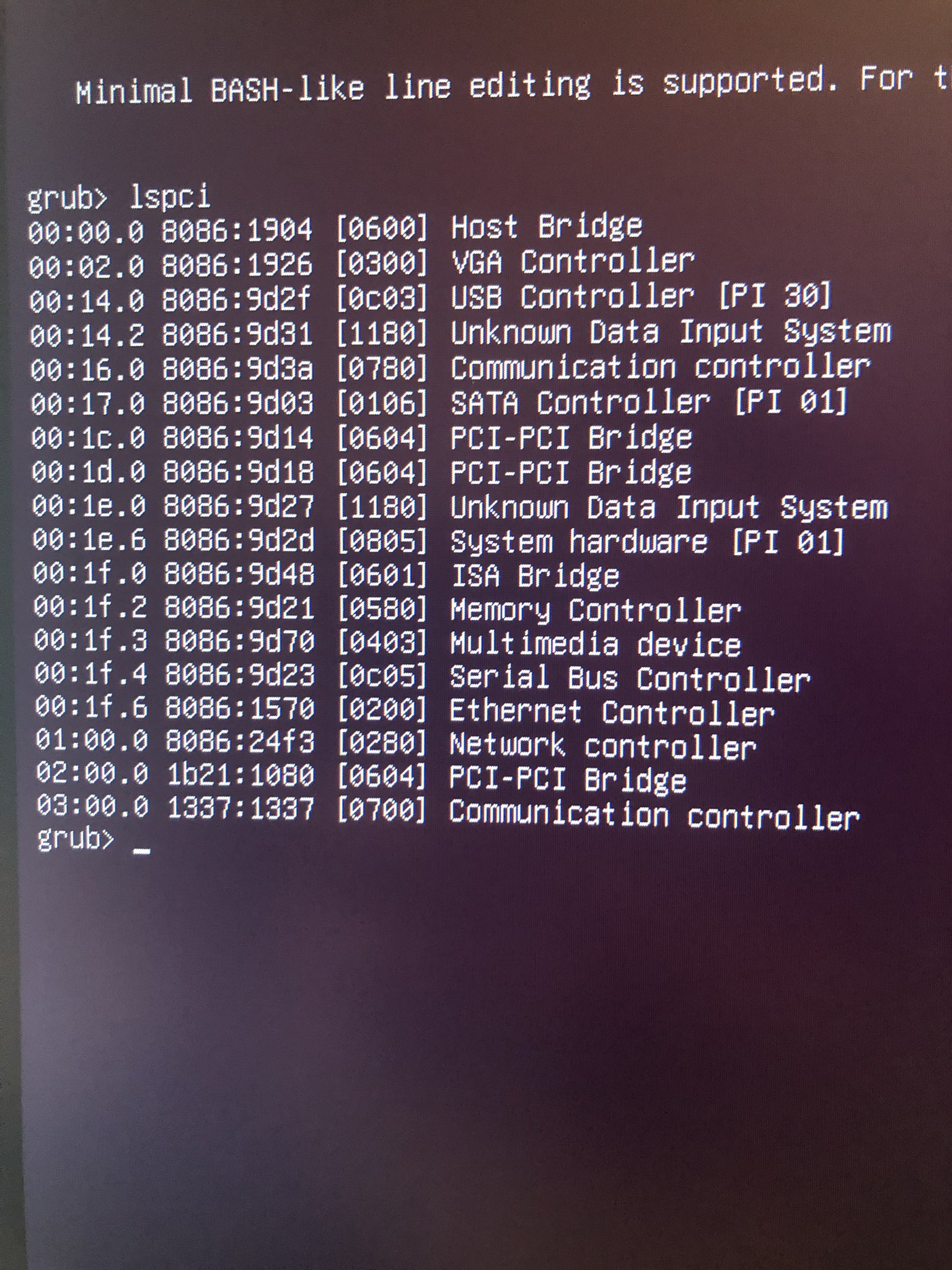

11 | # Demo

12 | My l337-Communication Controller

13 |

14 |  15 |

16 | # Reference Platform Parts List

17 | | Part | Description| Price |

18 | |--|--|--|

19 | | DE0-Nano | FPGA Board|~$100.00

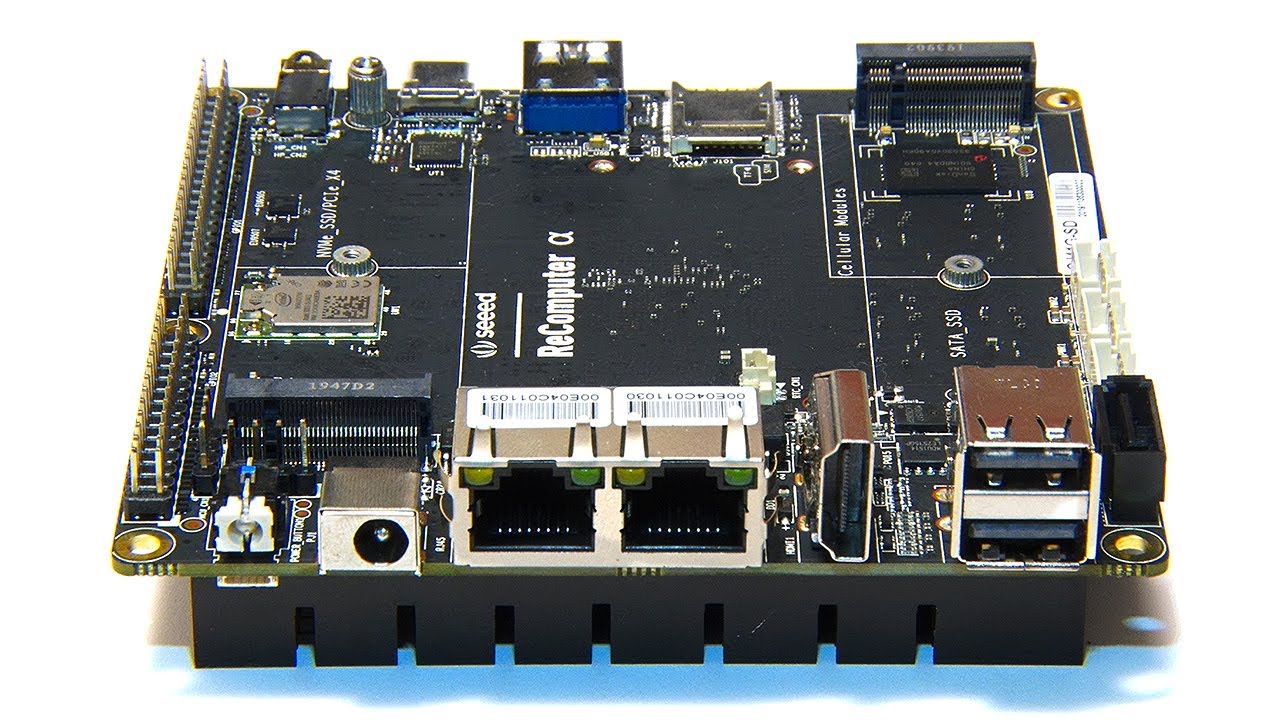

20 | | Seeed Odyssey X86J4105 SBC | SIngle Board Computer | ~$185.00

21 | |PCI2Nano Breakout PCB|Coverts PCI to DE0-Nano GPIO | ~$45 (OSHPark for 3)

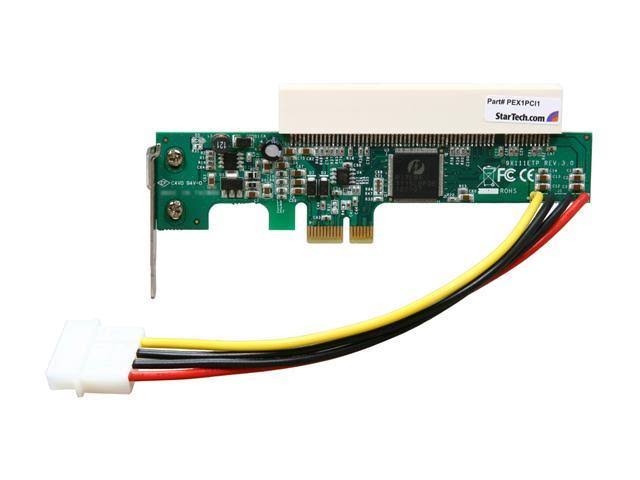

22 | |Startech PEX1PCI1| Converts PCIe to PCI | ~$40

23 | |M.2 Key M Extender PCIE x16 | Break out M.2 to PCIe x16 | ~$32

24 | 2x 100mil 40-pin IDC sockets| Soldered to the PCB| ~$1-$2

25 |

26 | # Directions

27 | 1) Mount the Extender cable into the Odyssey M.2 M Key slot. If you have standoffs you can affix the x16 connector of the extender to the SBC as shown in the picture above.

28 | 2) Mount the PEX1PCI1 onto the x16 connector. Supplying the molex power I believe is not required since it is used to power the 5V rails of a mounted PCI device, the PCI2Nano doesn't use this 5V rail (unless you bridge it to the Nano's 5V GPIO power pin via the board shunt). However it is best to power the nano through its USB cable

29 | 3) Connect the PCI2Nano breakout board to the DE0-Nano, make sure that the USB of the nano points in the correct direction as specified by the silkscreen

30 | 4) Connect the PCI side of the PCI2Nano onto the PEX1PCI1, make sure it is connected in the orientation as indicated by the silk screen. The arrow indicating the chassis side should be pointed to the externel side of the PEX1PCI1

31 |

32 | # PCB board

33 | There is a small amount of soldering involved with the PCB board to connect the 100mil IDC socket to the PCB board.

34 |

35 | # Parts

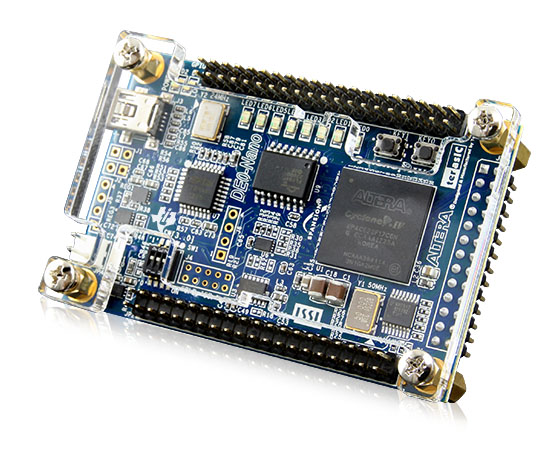

36 | The DE0-Nano:

37 |

38 |

15 |

16 | # Reference Platform Parts List

17 | | Part | Description| Price |

18 | |--|--|--|

19 | | DE0-Nano | FPGA Board|~$100.00

20 | | Seeed Odyssey X86J4105 SBC | SIngle Board Computer | ~$185.00

21 | |PCI2Nano Breakout PCB|Coverts PCI to DE0-Nano GPIO | ~$45 (OSHPark for 3)

22 | |Startech PEX1PCI1| Converts PCIe to PCI | ~$40

23 | |M.2 Key M Extender PCIE x16 | Break out M.2 to PCIe x16 | ~$32

24 | 2x 100mil 40-pin IDC sockets| Soldered to the PCB| ~$1-$2

25 |

26 | # Directions

27 | 1) Mount the Extender cable into the Odyssey M.2 M Key slot. If you have standoffs you can affix the x16 connector of the extender to the SBC as shown in the picture above.

28 | 2) Mount the PEX1PCI1 onto the x16 connector. Supplying the molex power I believe is not required since it is used to power the 5V rails of a mounted PCI device, the PCI2Nano doesn't use this 5V rail (unless you bridge it to the Nano's 5V GPIO power pin via the board shunt). However it is best to power the nano through its USB cable

29 | 3) Connect the PCI2Nano breakout board to the DE0-Nano, make sure that the USB of the nano points in the correct direction as specified by the silkscreen

30 | 4) Connect the PCI side of the PCI2Nano onto the PEX1PCI1, make sure it is connected in the orientation as indicated by the silk screen. The arrow indicating the chassis side should be pointed to the externel side of the PEX1PCI1

31 |

32 | # PCB board

33 | There is a small amount of soldering involved with the PCB board to connect the 100mil IDC socket to the PCB board.

34 |

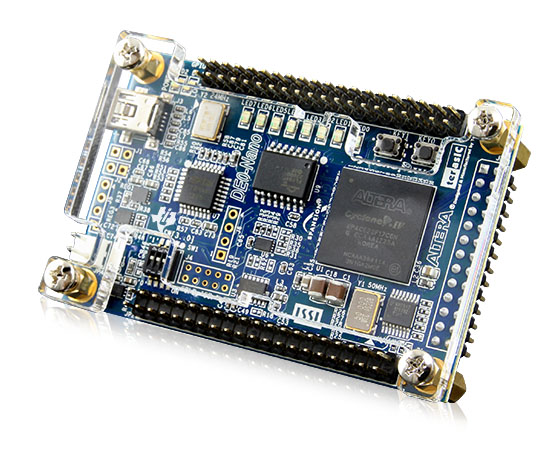

35 | # Parts

36 | The DE0-Nano:

37 |

38 |  39 |

40 | The PCI2Nano PCB:

41 |

42 |

39 |

40 | The PCI2Nano PCB:

41 |

42 |  43 |

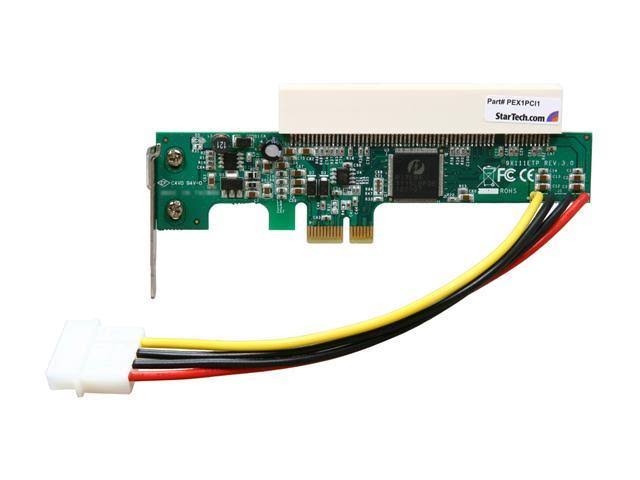

44 | The PEX1PCI1 PCIe-2-PCI Bridge:

45 |

46 |

43 |

44 | The PEX1PCI1 PCIe-2-PCI Bridge:

45 |

46 |  47 |

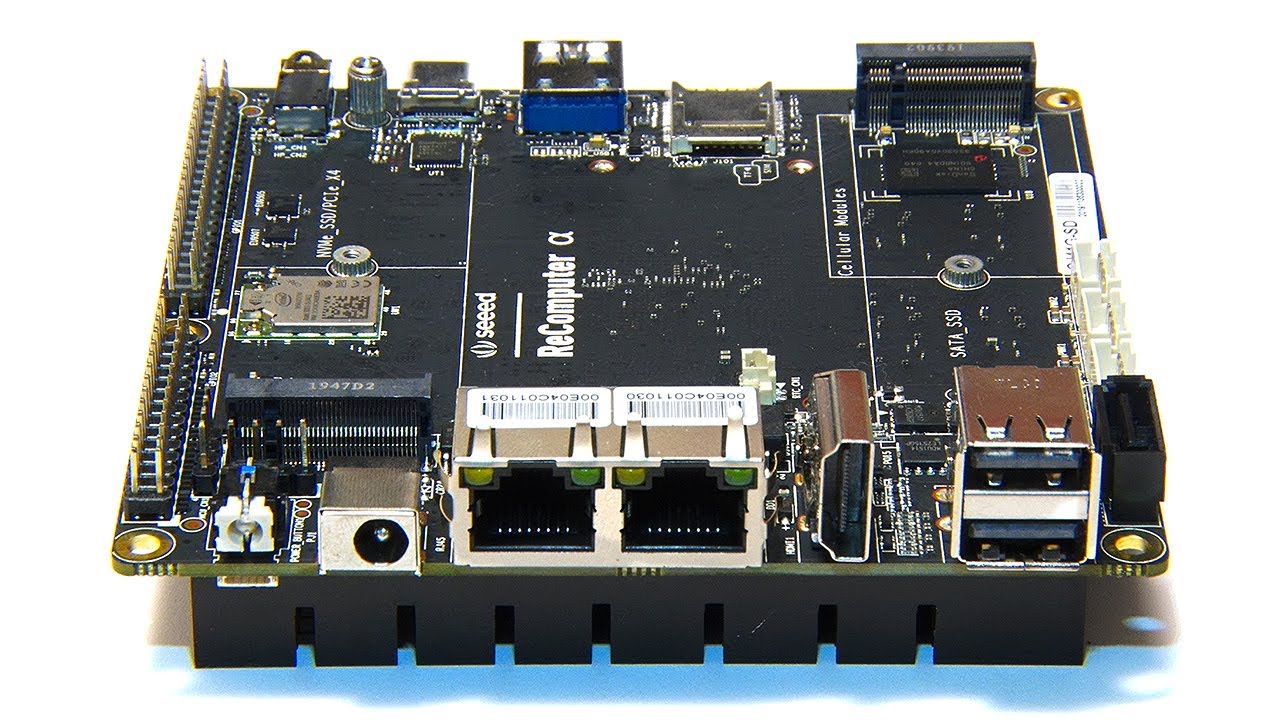

48 | The Seeed Odyssey X86J4105 SBC:

49 |

50 |

47 |

48 | The Seeed Odyssey X86J4105 SBC:

49 |

50 |  51 |

52 | The M.2 Key M Extender PCIE x16:

53 |

54 |

51 |

52 | The M.2 Key M Extender PCIE x16:

53 |

54 |  55 |

--------------------------------------------------------------------------------

/images/banner.png:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/defparam/PCI2Nano-PCB/c89a77f80c4dcbdea98dd997ebcd0e0f8f43258a/images/banner.png

--------------------------------------------------------------------------------

/images/image1.jpg:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/defparam/PCI2Nano-PCB/c89a77f80c4dcbdea98dd997ebcd0e0f8f43258a/images/image1.jpg

--------------------------------------------------------------------------------

/images/image2.jpg:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/defparam/PCI2Nano-PCB/c89a77f80c4dcbdea98dd997ebcd0e0f8f43258a/images/image2.jpg

--------------------------------------------------------------------------------

/images/image3.jpg:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/defparam/PCI2Nano-PCB/c89a77f80c4dcbdea98dd997ebcd0e0f8f43258a/images/image3.jpg

--------------------------------------------------------------------------------

/images/image4.jpg:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/defparam/PCI2Nano-PCB/c89a77f80c4dcbdea98dd997ebcd0e0f8f43258a/images/image4.jpg

--------------------------------------------------------------------------------

/images/image5.jpg:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/defparam/PCI2Nano-PCB/c89a77f80c4dcbdea98dd997ebcd0e0f8f43258a/images/image5.jpg

--------------------------------------------------------------------------------

/images/image6.jpg:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/defparam/PCI2Nano-PCB/c89a77f80c4dcbdea98dd997ebcd0e0f8f43258a/images/image6.jpg

--------------------------------------------------------------------------------

/images/image7.jpg:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/defparam/PCI2Nano-PCB/c89a77f80c4dcbdea98dd997ebcd0e0f8f43258a/images/image7.jpg

--------------------------------------------------------------------------------

/images/pci2nano.gif:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/defparam/PCI2Nano-PCB/c89a77f80c4dcbdea98dd997ebcd0e0f8f43258a/images/pci2nano.gif

--------------------------------------------------------------------------------

/pci2nano-cache.lib:

--------------------------------------------------------------------------------

1 | EESchema-LIBRARY Version 2.4

2 | #encoding utf-8

3 | #

4 | # Connector_Bus_PCI_32bit_Universal

5 | #

6 | DEF Connector_Bus_PCI_32bit_Universal J 0 20 Y Y 1 F N

7 | F0 "J" 0 3150 50 H V C CNN

8 | F1 "Connector_Bus_PCI_32bit_Universal" 0 -3250 50 H V C CNN

9 | F2 "" 0 -50 50 H I C CNN

10 | F3 "" 0 -50 50 H I C CNN

11 | DRAW

12 | S -750 3100 750 -3200 0 1 10 f

13 | X ~TRST# A1 900 3000 150 L 50 50 1 1 O

14 | X VIO A10 900 2100 150 L 50 50 1 1 W

15 | X RESERVED A11 900 2000 150 L 50 50 1 1 P

16 | X 3.3VAUX A14 900 1700 150 L 50 50 1 1 P

17 | X ~RST# A15 900 1600 150 L 50 50 1 1 O

18 | X VIO A16 900 1500 150 L 50 50 1 1 W

19 | X ~GNT# A17 900 1400 150 L 50 50 1 1 B

20 | X GND A18 900 1300 150 L 50 50 1 1 W

21 | X PME# A19 900 1200 150 L 50 50 1 1 P

22 | X +12V A2 900 2900 150 L 50 50 1 1 W

23 | X AD[30] A20 900 1100 150 L 50 50 1 1 B

24 | X +3.3V A21 900 1000 150 L 50 50 1 1 W

25 | X AD[28] A22 900 900 150 L 50 50 1 1 B

26 | X AD[26] A23 900 800 150 L 50 50 1 1 B

27 | X GND A24 900 700 150 L 50 50 1 1 W

28 | X AD[24] A25 900 600 150 L 50 50 1 1 B

29 | X IDSEL A26 900 500 150 L 50 50 1 1 O

30 | X +3.3V A27 900 400 150 L 50 50 1 1 W

31 | X AD[22] A28 900 300 150 L 50 50 1 1 B

32 | X AD[20] A29 900 200 150 L 50 50 1 1 B

33 | X TMS A3 900 2800 150 L 50 50 1 1 O

34 | X GND A30 900 100 150 L 50 50 1 1 W

35 | X AD[18] A31 900 0 150 L 50 50 1 1 B

36 | X AD[16] A32 900 -100 150 L 50 50 1 1 B

37 | X +3.3V A33 900 -200 150 L 50 50 1 1 W

38 | X ~FRAME# A34 900 -300 150 L 50 50 1 1 B

39 | X GND A35 900 -400 150 L 50 50 1 1 W

40 | X ~TRDY# A36 900 -500 150 L 50 50 1 1 B

41 | X GND A37 900 -600 150 L 50 50 1 1 W

42 | X ~STOP# A38 900 -700 150 L 50 50 1 1 B

43 | X +3.3V A39 900 -800 150 L 50 50 1 1 W

44 | X TDI A4 900 2700 150 L 50 50 1 1 O

45 | X RESERVED A40 900 -900 150 L 50 50 1 1 B

46 | X RESERVED A41 900 -1000 150 L 50 50 1 1 B

47 | X GND A42 900 -1100 150 L 50 50 1 1 W

48 | X PAR A43 900 -1200 150 L 50 50 1 1 B

49 | X AD[15] A44 900 -1300 150 L 50 50 1 1 B

50 | X +3.3V A45 900 -1400 150 L 50 50 1 1 W

51 | X AD[13] A46 900 -1500 150 L 50 50 1 1 B

52 | X AD[11] A47 900 -1600 150 L 50 50 1 1 B

53 | X GND A48 900 -1700 150 L 50 50 1 1 W

54 | X AD[09] A49 900 -1800 150 L 50 50 1 1 B

55 | X +5V A5 900 2600 150 L 50 50 1 1 W

56 | X ~C/BE#[0] A52 900 -2100 150 L 50 50 1 1 B

57 | X +3.3V A53 900 -2200 150 L 50 50 1 1 W

58 | X AD[06] A54 900 -2300 150 L 50 50 1 1 B

59 | X AD[04] A55 900 -2400 150 L 50 50 1 1 B

60 | X GND A56 900 -2500 150 L 50 50 1 1 W

61 | X AD[02] A57 900 -2600 150 L 50 50 1 1 B

62 | X AD[00] A58 900 -2700 150 L 50 50 1 1 B

63 | X VIO A59 900 -2800 150 L 50 50 1 1 W

64 | X ~INTA# A6 900 2500 150 L 50 50 1 1 I

65 | X ~REQ64# A60 900 -2900 150 L 50 50 1 1 B

66 | X +5V A61 900 -3000 150 L 50 50 1 1 W

67 | X +5V A62 900 -3100 150 L 50 50 1 1 W

68 | X ~INTC# A7 900 2400 150 L 50 50 1 1 I

69 | X +5V A8 900 2300 150 L 50 50 1 1 W

70 | X RESERVED A9 900 2200 150 L 50 50 1 1 P

71 | X -12V B1 -900 3000 150 R 50 50 1 1 W

72 | X RESERVED B10 -900 2100 150 R 50 50 1 1 P

73 | X ~PRSNT2# B11 -900 2000 150 R 50 50 1 1 I

74 | X RESERVED B14 -900 1700 150 R 50 50 1 1 P

75 | X GND B15 -900 1600 150 R 50 50 1 1 W

76 | X CLK B16 -900 1500 150 R 50 50 1 1 O

77 | X GND B17 -900 1400 150 R 50 50 1 1 W

78 | X ~REQ# B18 -900 1300 150 R 50 50 1 1 B

79 | X VIO B19 -900 1200 150 R 50 50 1 1 W

80 | X TCK B2 -900 2900 150 R 50 50 1 1 O

81 | X AD[31] B20 -900 1100 150 R 50 50 1 1 B

82 | X AD[29] B21 -900 1000 150 R 50 50 1 1 B

83 | X GND B22 -900 900 150 R 50 50 1 1 W

84 | X AD[27] B23 -900 800 150 R 50 50 1 1 B

85 | X AD[25] B24 -900 700 150 R 50 50 1 1 B

86 | X +3.3V B25 -900 600 150 R 50 50 1 1 W

87 | X C/BE#[3] B26 -900 500 150 R 50 50 1 1 B

88 | X AD[23] B27 -900 400 150 R 50 50 1 1 B

89 | X GND B28 -900 300 150 R 50 50 1 1 W

90 | X AD[21] B29 -900 200 150 R 50 50 1 1 B

91 | X GND B3 -900 2800 150 R 50 50 1 1 W

92 | X AD[19] B30 -900 100 150 R 50 50 1 1 B

93 | X +3.3V B31 -900 0 150 R 50 50 1 1 W

94 | X AD[17] B32 -900 -100 150 R 50 50 1 1 B

95 | X ~C/BE#[2] B33 -900 -200 150 R 50 50 1 1 B

96 | X GND B34 -900 -300 150 R 50 50 1 1 W

97 | X ~IRDY# B35 -900 -400 150 R 50 50 1 1 B

98 | X +3.3V B36 -900 -500 150 R 50 50 1 1 W

99 | X ~DEVSEL# B37 -900 -600 150 R 50 50 1 1 B

100 | X GND B38 -900 -700 150 R 50 50 1 1 W

101 | X ~LOCK# B39 -900 -800 150 R 50 50 1 1 B

102 | X TDO B4 -900 2700 150 R 50 50 1 1 I

103 | X ~PERR# B40 -900 -900 150 R 50 50 1 1 B

104 | X +3.3V B41 -900 -1000 150 R 50 50 1 1 W

105 | X ~SERR# B42 -900 -1100 150 R 50 50 1 1 I

106 | X +3.3V B43 -900 -1200 150 R 50 50 1 1 W

107 | X ~C/BE#[1] B44 -900 -1300 150 R 50 50 1 1 B

108 | X AD[14] B45 -900 -1400 150 R 50 50 1 1 B

109 | X GND B46 -900 -1500 150 R 50 50 1 1 W

110 | X AD[12] B47 -900 -1600 150 R 50 50 1 1 B

111 | X AD[10] B48 -900 -1700 150 R 50 50 1 1 B

112 | X M66EN B49 -900 -1800 150 R 50 50 1 1 W

113 | X +5V B5 -900 2600 150 R 50 50 1 1 W

114 | X AD[08] B52 -900 -2100 150 R 50 50 1 1 B

115 | X AD[07] B53 -900 -2200 150 R 50 50 1 1 B

116 | X +3.3V B54 -900 -2300 150 R 50 50 1 1 I

117 | X AD[05] B55 -900 -2400 150 R 50 50 1 1 B

118 | X AD[03] B56 -900 -2500 150 R 50 50 1 1 B

119 | X GND B57 -900 -2600 150 R 50 50 1 1 W

120 | X AD[01] B58 -900 -2700 150 R 50 50 1 1 B

121 | X VIO B59 -900 -2800 150 R 50 50 1 1 W

122 | X +5V B6 -900 2500 150 R 50 50 1 1 W

123 | X ~ACK64# B60 -900 -2900 150 R 50 50 1 1 B

124 | X +5V B61 -900 -3000 150 R 50 50 1 1 W

125 | X +5V B62 -900 -3100 150 R 50 50 1 1 W

126 | X ~INTB# B7 -900 2400 150 R 50 50 1 1 I

127 | X ~INTD# B8 -900 2300 150 R 50 50 1 1 I

128 | X ~PRSNT1# B9 -900 2200 150 R 50 50 1 1 I

129 | ENDDRAW

130 | ENDDEF

131 | #

132 | # Connector_Generic_Conn_02x20_Odd_Even

133 | #

134 | DEF Connector_Generic_Conn_02x20_Odd_Even J 0 40 Y N 1 F N

135 | F0 "J" 50 1000 50 H V C CNN

136 | F1 "Connector_Generic_Conn_02x20_Odd_Even" 50 -1100 50 H V C CNN

137 | F2 "" 0 0 50 H I C CNN

138 | F3 "" 0 0 50 H I C CNN

139 | $FPLIST

140 | Connector*:*_2x??_*

141 | $ENDFPLIST

142 | DRAW

143 | S -50 -995 0 -1005 1 1 6 N

144 | S -50 -895 0 -905 1 1 6 N

145 | S -50 -795 0 -805 1 1 6 N

146 | S -50 -695 0 -705 1 1 6 N

147 | S -50 -595 0 -605 1 1 6 N

148 | S -50 -495 0 -505 1 1 6 N

149 | S -50 -395 0 -405 1 1 6 N

150 | S -50 -295 0 -305 1 1 6 N

151 | S -50 -195 0 -205 1 1 6 N

152 | S -50 -95 0 -105 1 1 6 N

153 | S -50 5 0 -5 1 1 6 N

154 | S -50 105 0 95 1 1 6 N

155 | S -50 205 0 195 1 1 6 N

156 | S -50 305 0 295 1 1 6 N

157 | S -50 405 0 395 1 1 6 N

158 | S -50 505 0 495 1 1 6 N

159 | S -50 605 0 595 1 1 6 N

160 | S -50 705 0 695 1 1 6 N

161 | S -50 805 0 795 1 1 6 N

162 | S -50 905 0 895 1 1 6 N

163 | S -50 950 150 -1050 1 1 10 f

164 | S 150 -995 100 -1005 1 1 6 N

165 | S 150 -895 100 -905 1 1 6 N

166 | S 150 -795 100 -805 1 1 6 N

167 | S 150 -695 100 -705 1 1 6 N

168 | S 150 -595 100 -605 1 1 6 N

169 | S 150 -495 100 -505 1 1 6 N

170 | S 150 -395 100 -405 1 1 6 N

171 | S 150 -295 100 -305 1 1 6 N

172 | S 150 -195 100 -205 1 1 6 N

173 | S 150 -95 100 -105 1 1 6 N

174 | S 150 5 100 -5 1 1 6 N

175 | S 150 105 100 95 1 1 6 N

176 | S 150 205 100 195 1 1 6 N

177 | S 150 305 100 295 1 1 6 N

178 | S 150 405 100 395 1 1 6 N

179 | S 150 505 100 495 1 1 6 N

180 | S 150 605 100 595 1 1 6 N

181 | S 150 705 100 695 1 1 6 N

182 | S 150 805 100 795 1 1 6 N

183 | S 150 905 100 895 1 1 6 N

184 | X Pin_1 1 -200 900 150 R 50 50 1 1 P

185 | X Pin_10 10 300 500 150 L 50 50 1 1 P

186 | X Pin_11 11 -200 400 150 R 50 50 1 1 P

187 | X Pin_12 12 300 400 150 L 50 50 1 1 P

188 | X Pin_13 13 -200 300 150 R 50 50 1 1 P

189 | X Pin_14 14 300 300 150 L 50 50 1 1 P

190 | X Pin_15 15 -200 200 150 R 50 50 1 1 P

191 | X Pin_16 16 300 200 150 L 50 50 1 1 P

192 | X Pin_17 17 -200 100 150 R 50 50 1 1 P

193 | X Pin_18 18 300 100 150 L 50 50 1 1 P

194 | X Pin_19 19 -200 0 150 R 50 50 1 1 P

195 | X Pin_2 2 300 900 150 L 50 50 1 1 P

196 | X Pin_20 20 300 0 150 L 50 50 1 1 P

197 | X Pin_21 21 -200 -100 150 R 50 50 1 1 P

198 | X Pin_22 22 300 -100 150 L 50 50 1 1 P

199 | X Pin_23 23 -200 -200 150 R 50 50 1 1 P

200 | X Pin_24 24 300 -200 150 L 50 50 1 1 P

201 | X Pin_25 25 -200 -300 150 R 50 50 1 1 P

202 | X Pin_26 26 300 -300 150 L 50 50 1 1 P

203 | X Pin_27 27 -200 -400 150 R 50 50 1 1 P

204 | X Pin_28 28 300 -400 150 L 50 50 1 1 P

205 | X Pin_29 29 -200 -500 150 R 50 50 1 1 P

206 | X Pin_3 3 -200 800 150 R 50 50 1 1 P

207 | X Pin_30 30 300 -500 150 L 50 50 1 1 P

208 | X Pin_31 31 -200 -600 150 R 50 50 1 1 P

209 | X Pin_32 32 300 -600 150 L 50 50 1 1 P

210 | X Pin_33 33 -200 -700 150 R 50 50 1 1 P

211 | X Pin_34 34 300 -700 150 L 50 50 1 1 P

212 | X Pin_35 35 -200 -800 150 R 50 50 1 1 P

213 | X Pin_36 36 300 -800 150 L 50 50 1 1 P

214 | X Pin_37 37 -200 -900 150 R 50 50 1 1 P

215 | X Pin_38 38 300 -900 150 L 50 50 1 1 P

216 | X Pin_39 39 -200 -1000 150 R 50 50 1 1 P

217 | X Pin_4 4 300 800 150 L 50 50 1 1 P

218 | X Pin_40 40 300 -1000 150 L 50 50 1 1 P

219 | X Pin_5 5 -200 700 150 R 50 50 1 1 P

220 | X Pin_6 6 300 700 150 L 50 50 1 1 P

221 | X Pin_7 7 -200 600 150 R 50 50 1 1 P

222 | X Pin_8 8 300 600 150 L 50 50 1 1 P

223 | X Pin_9 9 -200 500 150 R 50 50 1 1 P

224 | ENDDRAW

225 | ENDDEF

226 | #

227 | # Jumper_SolderJumper_2_Bridged

228 | #

229 | DEF Jumper_SolderJumper_2_Bridged JP 0 0 Y N 1 F N

230 | F0 "JP" 0 80 50 H V C CNN

231 | F1 "Jumper_SolderJumper_2_Bridged" 0 -100 50 H V C CNN

232 | F2 "" 0 0 50 H I C CNN

233 | F3 "" 0 0 50 H I C CNN

234 | $FPLIST

235 | SolderJumper*Bridged*

236 | $ENDFPLIST

237 | DRAW

238 | A -10 0 40 901 -901 0 1 0 N -10 40 -10 -40

239 | A -10 0 40 901 -901 0 1 0 F -10 40 -10 -40

240 | A 10 0 40 -899 899 0 1 0 N 10 -40 10 40

241 | A 10 0 40 -899 899 0 1 0 F 10 -40 10 40

242 | S -20 20 20 -20 0 1 0 F

243 | P 2 0 1 0 -10 40 -10 -40 N

244 | P 2 0 1 0 10 40 10 -40 N

245 | X A 1 -150 0 100 R 50 50 1 1 P

246 | X B 2 150 0 100 L 50 50 1 1 P

247 | ENDDRAW

248 | ENDDEF

249 | #

250 | # power_+3.3V

251 | #

252 | DEF power_+3.3V #PWR 0 0 Y Y 1 F P

253 | F0 "#PWR" 0 -150 50 H I C CNN

254 | F1 "power_+3.3V" 0 140 50 H V C CNN

255 | F2 "" 0 0 50 H I C CNN

256 | F3 "" 0 0 50 H I C CNN

257 | ALIAS +3.3V

258 | DRAW

259 | P 2 0 1 0 -30 50 0 100 N

260 | P 2 0 1 0 0 0 0 100 N

261 | P 2 0 1 0 0 100 30 50 N

262 | X +3V3 1 0 0 0 U 50 50 1 1 W N

263 | ENDDRAW

264 | ENDDEF

265 | #

266 | # power_+3.3VA

267 | #

268 | DEF power_+3.3VA #PWR 0 0 Y Y 1 F P

269 | F0 "#PWR" 0 -150 50 H I C CNN

270 | F1 "power_+3.3VA" 0 140 50 H V C CNN

271 | F2 "" 0 0 50 H I C CNN

272 | F3 "" 0 0 50 H I C CNN

273 | DRAW

274 | P 2 0 1 0 -30 50 0 100 N

275 | P 2 0 1 0 0 0 0 100 N

276 | P 2 0 1 0 0 100 30 50 N

277 | X +3.3VA 1 0 0 0 U 50 50 1 1 W N

278 | ENDDRAW

279 | ENDDEF

280 | #

281 | # power_+5V

282 | #

283 | DEF power_+5V #PWR 0 0 Y Y 1 F P

284 | F0 "#PWR" 0 -150 50 H I C CNN

285 | F1 "power_+5V" 0 140 50 H V C CNN

286 | F2 "" 0 0 50 H I C CNN

287 | F3 "" 0 0 50 H I C CNN

288 | DRAW

289 | P 2 0 1 0 -30 50 0 100 N

290 | P 2 0 1 0 0 0 0 100 N

291 | P 2 0 1 0 0 100 30 50 N

292 | X +5V 1 0 0 0 U 50 50 1 1 W N

293 | ENDDRAW

294 | ENDDEF

295 | #

296 | # power_+5VP

297 | #

298 | DEF power_+5VP #PWR 0 0 Y Y 1 F P

299 | F0 "#PWR" 0 -150 50 H I C CNN

300 | F1 "power_+5VP" 0 140 50 H V C CNN

301 | F2 "" 0 0 50 H I C CNN

302 | F3 "" 0 0 50 H I C CNN

303 | DRAW

304 | P 2 0 1 0 -30 50 0 100 N

305 | P 2 0 1 0 0 0 0 100 N

306 | P 2 0 1 0 0 100 30 50 N

307 | X +5VP 1 0 0 0 U 50 50 1 1 W N

308 | ENDDRAW

309 | ENDDEF

310 | #

311 | # power_GND

312 | #

313 | DEF power_GND #PWR 0 0 Y Y 1 F P

314 | F0 "#PWR" 0 -250 50 H I C CNN

315 | F1 "power_GND" 0 -150 50 H V C CNN

316 | F2 "" 0 0 50 H I C CNN

317 | F3 "" 0 0 50 H I C CNN

318 | DRAW

319 | P 6 0 1 0 0 0 0 -50 50 -50 0 -100 -50 -50 0 -50 N

320 | X GND 1 0 0 0 D 50 50 1 1 W N

321 | ENDDRAW

322 | ENDDEF

323 | #

324 | #End Library

325 |

--------------------------------------------------------------------------------

/pci2nano.net:

--------------------------------------------------------------------------------

1 | (export (version D)

2 | (design

3 | (source D:\hardware\pcb\pci2nano\pci2nano.sch)

4 | (date "9/27/2019 9:53:51 AM")

5 | (tool "Eeschema (5.1.4)-1")

6 | (sheet (number 1) (name /) (tstamps /)

7 | (title_block

8 | (title)

9 | (company)

10 | (rev)

11 | (date)

12 | (source pci2nano.sch)

13 | (comment (number 1) (value ""))

14 | (comment (number 2) (value ""))

15 | (comment (number 3) (value ""))

16 | (comment (number 4) (value "")))))

17 | (components

18 | (comp (ref J2)

19 | (value Conn_02x20_Odd_Even)

20 | (footprint Connector_PinHeader_2.54mm:PinHeader_2x20_P2.54mm_Vertical)

21 | (datasheet ~)

22 | (libsource (lib Connector_Generic) (part Conn_02x20_Odd_Even) (description "Generic connector, double row, 02x20, odd/even pin numbering scheme (row 1 odd numbers, row 2 even numbers), script generated (kicad-library-utils/schlib/autogen/connector/)"))

23 | (sheetpath (names /) (tstamps /))

24 | (tstamp 5D8D1ED3))

25 | (comp (ref J3)

26 | (value Conn_02x20_Odd_Even)

27 | (footprint Connector_PinHeader_2.54mm:PinHeader_2x20_P2.54mm_Vertical)

28 | (datasheet ~)

29 | (libsource (lib Connector_Generic) (part Conn_02x20_Odd_Even) (description "Generic connector, double row, 02x20, odd/even pin numbering scheme (row 1 odd numbers, row 2 even numbers), script generated (kicad-library-utils/schlib/autogen/connector/)"))

30 | (sheetpath (names /) (tstamps /))

31 | (tstamp 5D8D490E))

32 | (comp (ref J1)

33 | (value Bus_PCI_32bit_Universal)

34 | (footprint Connector_PCBEdge:BUS_PCI_UNIVERSAL)

35 | (datasheet http://pinouts.ru/Slots/PCI_pinout.shtml)

36 | (libsource (lib Connector) (part Bus_PCI_32bit_Universal) (description "PCI bus connector for universal 5V/3.3V cards"))

37 | (sheetpath (names /) (tstamps /))

38 | (tstamp 5D8DE1B0))

39 | (comp (ref JP1)

40 | (value SolderJumper_2_Bridged)

41 | (datasheet ~)

42 | (libsource (lib Jumper) (part SolderJumper_2_Bridged) (description "Solder Jumper, 2-pole, closed/bridged"))

43 | (sheetpath (names /) (tstamps /))

44 | (tstamp 5D8F6E87))

45 | (comp (ref JP2)

46 | (value SolderJumper_2_Bridged)

47 | (datasheet ~)

48 | (libsource (lib Jumper) (part SolderJumper_2_Bridged) (description "Solder Jumper, 2-pole, closed/bridged"))

49 | (sheetpath (names /) (tstamps /))

50 | (tstamp 5D900D15)))

51 | (libparts

52 | (libpart (lib Connector) (part Bus_PCI_32bit_Universal)

53 | (description "PCI bus connector for universal 5V/3.3V cards")

54 | (docs http://pinouts.ru/Slots/PCI_pinout.shtml)

55 | (fields

56 | (field (name Reference) J)

57 | (field (name Value) Bus_PCI_32bit_Universal))

58 | (pins

59 | (pin (num A1) (name ~TRST#) (type output))

60 | (pin (num A2) (name +12V) (type power_in))

61 | (pin (num A3) (name TMS) (type output))

62 | (pin (num A4) (name TDI) (type output))

63 | (pin (num A5) (name +5V) (type power_in))

64 | (pin (num A6) (name ~INTA#) (type input))

65 | (pin (num A7) (name ~INTC#) (type input))

66 | (pin (num A8) (name +5V) (type power_in))

67 | (pin (num A9) (name RESERVED) (type passive))

68 | (pin (num A10) (name VIO) (type power_in))

69 | (pin (num A11) (name RESERVED) (type passive))

70 | (pin (num A14) (name 3.3VAUX) (type passive))

71 | (pin (num A15) (name ~RST#) (type output))

72 | (pin (num A16) (name VIO) (type power_in))

73 | (pin (num A17) (name ~GNT#) (type BiDi))

74 | (pin (num A18) (name GND) (type power_in))

75 | (pin (num A19) (name PME#) (type passive))

76 | (pin (num A20) (name AD[30]) (type BiDi))

77 | (pin (num A21) (name +3.3V) (type power_in))

78 | (pin (num A22) (name AD[28]) (type BiDi))

79 | (pin (num A23) (name AD[26]) (type BiDi))

80 | (pin (num A24) (name GND) (type power_in))

81 | (pin (num A25) (name AD[24]) (type BiDi))

82 | (pin (num A26) (name IDSEL) (type output))

83 | (pin (num A27) (name +3.3V) (type power_in))

84 | (pin (num A28) (name AD[22]) (type BiDi))

85 | (pin (num A29) (name AD[20]) (type BiDi))

86 | (pin (num A30) (name GND) (type power_in))

87 | (pin (num A31) (name AD[18]) (type BiDi))

88 | (pin (num A32) (name AD[16]) (type BiDi))

89 | (pin (num A33) (name +3.3V) (type power_in))

90 | (pin (num A34) (name ~FRAME#) (type BiDi))

91 | (pin (num A35) (name GND) (type power_in))

92 | (pin (num A36) (name ~TRDY#) (type BiDi))

93 | (pin (num A37) (name GND) (type power_in))

94 | (pin (num A38) (name ~STOP#) (type BiDi))

95 | (pin (num A39) (name +3.3V) (type power_in))

96 | (pin (num A40) (name RESERVED) (type BiDi))

97 | (pin (num A41) (name RESERVED) (type BiDi))

98 | (pin (num A42) (name GND) (type power_in))

99 | (pin (num A43) (name PAR) (type BiDi))

100 | (pin (num A44) (name AD[15]) (type BiDi))

101 | (pin (num A45) (name +3.3V) (type power_in))

102 | (pin (num A46) (name AD[13]) (type BiDi))

103 | (pin (num A47) (name AD[11]) (type BiDi))

104 | (pin (num A48) (name GND) (type power_in))

105 | (pin (num A49) (name AD[09]) (type BiDi))

106 | (pin (num A52) (name ~C/BE#[0]) (type BiDi))

107 | (pin (num A53) (name +3.3V) (type power_in))

108 | (pin (num A54) (name AD[06]) (type BiDi))

109 | (pin (num A55) (name AD[04]) (type BiDi))

110 | (pin (num A56) (name GND) (type power_in))

111 | (pin (num A57) (name AD[02]) (type BiDi))

112 | (pin (num A58) (name AD[00]) (type BiDi))

113 | (pin (num A59) (name VIO) (type power_in))

114 | (pin (num A60) (name ~REQ64#) (type BiDi))

115 | (pin (num A61) (name +5V) (type power_in))

116 | (pin (num A62) (name +5V) (type power_in))

117 | (pin (num B1) (name -12V) (type power_in))

118 | (pin (num B2) (name TCK) (type output))

119 | (pin (num B3) (name GND) (type power_in))

120 | (pin (num B4) (name TDO) (type input))

121 | (pin (num B5) (name +5V) (type power_in))

122 | (pin (num B6) (name +5V) (type power_in))

123 | (pin (num B7) (name ~INTB#) (type input))

124 | (pin (num B8) (name ~INTD#) (type input))

125 | (pin (num B9) (name ~PRSNT1#) (type input))

126 | (pin (num B10) (name RESERVED) (type passive))

127 | (pin (num B11) (name ~PRSNT2#) (type input))

128 | (pin (num B14) (name RESERVED) (type passive))

129 | (pin (num B15) (name GND) (type power_in))

130 | (pin (num B16) (name CLK) (type output))

131 | (pin (num B17) (name GND) (type power_in))

132 | (pin (num B18) (name ~REQ#) (type BiDi))

133 | (pin (num B19) (name VIO) (type power_in))

134 | (pin (num B20) (name AD[31]) (type BiDi))

135 | (pin (num B21) (name AD[29]) (type BiDi))

136 | (pin (num B22) (name GND) (type power_in))

137 | (pin (num B23) (name AD[27]) (type BiDi))

138 | (pin (num B24) (name AD[25]) (type BiDi))

139 | (pin (num B25) (name +3.3V) (type power_in))

140 | (pin (num B26) (name C/BE#[3]) (type BiDi))

141 | (pin (num B27) (name AD[23]) (type BiDi))

142 | (pin (num B28) (name GND) (type power_in))

143 | (pin (num B29) (name AD[21]) (type BiDi))

144 | (pin (num B30) (name AD[19]) (type BiDi))

145 | (pin (num B31) (name +3.3V) (type power_in))

146 | (pin (num B32) (name AD[17]) (type BiDi))

147 | (pin (num B33) (name ~C/BE#[2]) (type BiDi))

148 | (pin (num B34) (name GND) (type power_in))

149 | (pin (num B35) (name ~IRDY#) (type BiDi))

150 | (pin (num B36) (name +3.3V) (type power_in))

151 | (pin (num B37) (name ~DEVSEL#) (type BiDi))

152 | (pin (num B38) (name GND) (type power_in))

153 | (pin (num B39) (name ~LOCK#) (type BiDi))

154 | (pin (num B40) (name ~PERR#) (type BiDi))

155 | (pin (num B41) (name +3.3V) (type power_in))

156 | (pin (num B42) (name ~SERR#) (type input))

157 | (pin (num B43) (name +3.3V) (type power_in))

158 | (pin (num B44) (name ~C/BE#[1]) (type BiDi))

159 | (pin (num B45) (name AD[14]) (type BiDi))

160 | (pin (num B46) (name GND) (type power_in))

161 | (pin (num B47) (name AD[12]) (type BiDi))

162 | (pin (num B48) (name AD[10]) (type BiDi))

163 | (pin (num B49) (name M66EN) (type power_in))

164 | (pin (num B52) (name AD[08]) (type BiDi))

165 | (pin (num B53) (name AD[07]) (type BiDi))

166 | (pin (num B54) (name +3.3V) (type input))

167 | (pin (num B55) (name AD[05]) (type BiDi))

168 | (pin (num B56) (name AD[03]) (type BiDi))

169 | (pin (num B57) (name GND) (type power_in))

170 | (pin (num B58) (name AD[01]) (type BiDi))

171 | (pin (num B59) (name VIO) (type power_in))

172 | (pin (num B60) (name ~ACK64#) (type BiDi))

173 | (pin (num B61) (name +5V) (type power_in))

174 | (pin (num B62) (name +5V) (type power_in))))

175 | (libpart (lib Connector_Generic) (part Conn_02x20_Odd_Even)

176 | (description "Generic connector, double row, 02x20, odd/even pin numbering scheme (row 1 odd numbers, row 2 even numbers), script generated (kicad-library-utils/schlib/autogen/connector/)")

177 | (docs ~)

178 | (footprints

179 | (fp Connector*:*_2x??_*))

180 | (fields

181 | (field (name Reference) J)

182 | (field (name Value) Conn_02x20_Odd_Even))

183 | (pins

184 | (pin (num 1) (name Pin_1) (type passive))

185 | (pin (num 2) (name Pin_2) (type passive))

186 | (pin (num 3) (name Pin_3) (type passive))

187 | (pin (num 4) (name Pin_4) (type passive))

188 | (pin (num 5) (name Pin_5) (type passive))

189 | (pin (num 6) (name Pin_6) (type passive))

190 | (pin (num 7) (name Pin_7) (type passive))

191 | (pin (num 8) (name Pin_8) (type passive))

192 | (pin (num 9) (name Pin_9) (type passive))

193 | (pin (num 10) (name Pin_10) (type passive))

194 | (pin (num 11) (name Pin_11) (type passive))

195 | (pin (num 12) (name Pin_12) (type passive))

196 | (pin (num 13) (name Pin_13) (type passive))

197 | (pin (num 14) (name Pin_14) (type passive))

198 | (pin (num 15) (name Pin_15) (type passive))

199 | (pin (num 16) (name Pin_16) (type passive))

200 | (pin (num 17) (name Pin_17) (type passive))

201 | (pin (num 18) (name Pin_18) (type passive))

202 | (pin (num 19) (name Pin_19) (type passive))

203 | (pin (num 20) (name Pin_20) (type passive))

204 | (pin (num 21) (name Pin_21) (type passive))

205 | (pin (num 22) (name Pin_22) (type passive))

206 | (pin (num 23) (name Pin_23) (type passive))

207 | (pin (num 24) (name Pin_24) (type passive))

208 | (pin (num 25) (name Pin_25) (type passive))

209 | (pin (num 26) (name Pin_26) (type passive))

210 | (pin (num 27) (name Pin_27) (type passive))

211 | (pin (num 28) (name Pin_28) (type passive))

212 | (pin (num 29) (name Pin_29) (type passive))

213 | (pin (num 30) (name Pin_30) (type passive))

214 | (pin (num 31) (name Pin_31) (type passive))

215 | (pin (num 32) (name Pin_32) (type passive))

216 | (pin (num 33) (name Pin_33) (type passive))

217 | (pin (num 34) (name Pin_34) (type passive))

218 | (pin (num 35) (name Pin_35) (type passive))

219 | (pin (num 36) (name Pin_36) (type passive))

220 | (pin (num 37) (name Pin_37) (type passive))

221 | (pin (num 38) (name Pin_38) (type passive))

222 | (pin (num 39) (name Pin_39) (type passive))

223 | (pin (num 40) (name Pin_40) (type passive))))

224 | (libpart (lib Jumper) (part SolderJumper_2_Bridged)

225 | (description "Solder Jumper, 2-pole, closed/bridged")

226 | (docs ~)

227 | (footprints

228 | (fp SolderJumper*Bridged*))

229 | (fields

230 | (field (name Reference) JP)

231 | (field (name Value) SolderJumper_2_Bridged))

232 | (pins

233 | (pin (num 1) (name A) (type passive))

234 | (pin (num 2) (name B) (type passive)))))

235 | (libraries

236 | (library (logical Connector)

237 | (uri "D:\\Program Files\\KiCad\\share\\kicad\\library/Connector.lib"))

238 | (library (logical Connector_Generic)

239 | (uri "D:\\Program Files\\KiCad\\share\\kicad\\library/Connector_Generic.lib"))

240 | (library (logical Jumper)

241 | (uri "D:\\Program Files\\KiCad\\share\\kicad\\library/Jumper.lib")))

242 | (nets

243 | (net (code 1) (name "Net-(J1-PadA19)")

244 | (node (ref J1) (pin A19)))

245 | (net (code 2) (name "Net-(J1-PadA3)")

246 | (node (ref J1) (pin A3)))

247 | (net (code 3) (name "Net-(J1-PadA2)")

248 | (node (ref J1) (pin A2)))

249 | (net (code 4) (name "Net-(J1-PadA16)")

250 | (node (ref J1) (pin A16)))

251 | (net (code 5) (name "Net-(J1-PadA14)")

252 | (node (ref J1) (pin A14)))

253 | (net (code 6) (name "Net-(J1-PadA11)")

254 | (node (ref J1) (pin A11)))

255 | (net (code 7) (name "Net-(J1-PadA10)")

256 | (node (ref J1) (pin A10)))

257 | (net (code 8) (name "Net-(J1-PadA1)")

258 | (node (ref J1) (pin A1)))

259 | (net (code 9) (name IDSEL)

260 | (node (ref J1) (pin A26)))

261 | (net (code 10) (name PAR)

262 | (node (ref J1) (pin A43)))

263 | (net (code 11) (name STOP#)

264 | (node (ref J1) (pin A38)))

265 | (net (code 12) (name TRDY#)

266 | (node (ref J1) (pin A36)))

267 | (net (code 13) (name FRAME#)

268 | (node (ref J1) (pin A34)))

269 | (net (code 14) (name AD[00])

270 | (node (ref J1) (pin A58)))

271 | (net (code 15) (name "Net-(J1-PadA41)")

272 | (node (ref J1) (pin A41)))

273 | (net (code 16) (name "Net-(J1-PadA40)")

274 | (node (ref J1) (pin A40)))

275 | (net (code 17) (name AD[25])

276 | (node (ref J1) (pin B24)))

277 | (net (code 18) (name AD[14])

278 | (node (ref J1) (pin B45)))

279 | (net (code 19) (name SERR#)

280 | (node (ref J1) (pin B42)))

281 | (net (code 20) (name PERR#)

282 | (node (ref J1) (pin B40)))

283 | (net (code 21) (name LOCK#)

284 | (node (ref J1) (pin B39)))

285 | (net (code 22) (name DEVSEL#)

286 | (node (ref J1) (pin B37)))

287 | (net (code 23) (name IRDY#)

288 | (node (ref J1) (pin B35)))

289 | (net (code 24) (name C\BE#[1])

290 | (node (ref J1) (pin B44)))

291 | (net (code 25) (name C\BE#[2])

292 | (node (ref J1) (pin B33)))

293 | (net (code 26) (name AD[17])

294 | (node (ref J1) (pin B32)))

295 | (net (code 27) (name AD[19])

296 | (node (ref J1) (pin B30)))

297 | (net (code 28) (name AD[21])

298 | (node (ref J1) (pin B29)))

299 | (net (code 29) (name C\BE#[3])

300 | (node (ref J1) (pin B26)))

301 | (net (code 30) (name AD[23])

302 | (node (ref J1) (pin B27)))

303 | (net (code 31) (name AD[12])

304 | (node (ref J1) (pin B47)))

305 | (net (code 32) (name AD[27])

306 | (node (ref J1) (pin B23)))

307 | (net (code 33) (name AD[29])

308 | (node (ref J1) (pin B21)))

309 | (net (code 34) (name AD[31])

310 | (node (ref J1) (pin B20)))

311 | (net (code 35) (name REQ#)

312 | (node (ref J1) (pin B18)))

313 | (net (code 36) (name CLK)

314 | (node (ref J1) (pin B16)))

315 | (net (code 37) (name INTD#)

316 | (node (ref J1) (pin B8)))

317 | (net (code 38) (name INTB#)

318 | (node (ref J1) (pin B7)))

319 | (net (code 39) (name AD[28])

320 | (node (ref J1) (pin A22)))

321 | (net (code 40) (name AD[02])

322 | (node (ref J1) (pin A57)))

323 | (net (code 41) (name AD[04])

324 | (node (ref J1) (pin A55)))

325 | (net (code 42) (name AD[09])

326 | (node (ref J1) (pin A49)))

327 | (net (code 43) (name AD[06])

328 | (node (ref J1) (pin A54)))

329 | (net (code 44) (name AD[11])

330 | (node (ref J1) (pin A47)))

331 | (net (code 45) (name AD[13])

332 | (node (ref J1) (pin A46)))

333 | (net (code 46) (name AD[15])

334 | (node (ref J1) (pin A44)))

335 | (net (code 47) (name AD[16])

336 | (node (ref J1) (pin A32)))

337 | (net (code 48) (name AD[18])

338 | (node (ref J1) (pin A31)))

339 | (net (code 49) (name AD[20])

340 | (node (ref J1) (pin A29)))

341 | (net (code 50) (name AD[22])

342 | (node (ref J1) (pin A28)))

343 | (net (code 51) (name AD[24])

344 | (node (ref J1) (pin A25)))

345 | (net (code 52) (name AD[26])

346 | (node (ref J1) (pin A23)))

347 | (net (code 53) (name AD[30])

348 | (node (ref J1) (pin A20)))

349 | (net (code 54) (name GNT#)

350 | (node (ref J1) (pin A17)))

351 | (net (code 55) (name C\BE#[0])

352 | (node (ref J1) (pin A52)))

353 | (net (code 56) (name RST#)

354 | (node (ref J1) (pin A15)))

355 | (net (code 57) (name INTC#)

356 | (node (ref J1) (pin A7)))

357 | (net (code 58) (name INTA#)

358 | (node (ref J1) (pin A6)))

359 | (net (code 59) (name AD[01])

360 | (node (ref J1) (pin B58)))

361 | (net (code 60) (name AD[03])

362 | (node (ref J1) (pin B56)))

363 | (net (code 61) (name AD[05])

364 | (node (ref J1) (pin B55)))

365 | (net (code 62) (name AD[07])

366 | (node (ref J1) (pin B53)))

367 | (net (code 63) (name AD[08])

368 | (node (ref J1) (pin B52)))

369 | (net (code 64) (name AD[10])

370 | (node (ref J1) (pin B48)))

371 | (net (code 65) (name "Net-(J1-PadB19)")

372 | (node (ref J1) (pin B19)))

373 | (net (code 66) (name +5VP)

374 | (node (ref J2) (pin 11))

375 | (node (ref J3) (pin 11))

376 | (node (ref JP1) (pin 2)))

377 | (net (code 67) (name GND)

378 | (node (ref J3) (pin 12))

379 | (node (ref J2) (pin 12))

380 | (node (ref J2) (pin 30))

381 | (node (ref J3) (pin 30))

382 | (node (ref J1) (pin B3))

383 | (node (ref J1) (pin B38))

384 | (node (ref J1) (pin B46))

385 | (node (ref J1) (pin B49))

386 | (node (ref J1) (pin B28))

387 | (node (ref J1) (pin B17))

388 | (node (ref J1) (pin B22))

389 | (node (ref J1) (pin B15))

390 | (node (ref J1) (pin B57))

391 | (node (ref J1) (pin B9))

392 | (node (ref J1) (pin B34))

393 | (node (ref J1) (pin A35))

394 | (node (ref J1) (pin A37))

395 | (node (ref J1) (pin A42))

396 | (node (ref J1) (pin A48))

397 | (node (ref J1) (pin A56))

398 | (node (ref J1) (pin A18))

399 | (node (ref J1) (pin A24))

400 | (node (ref J1) (pin A30)))

401 | (net (code 68) (name "Net-(J1-PadB11)")

402 | (node (ref J1) (pin B11)))

403 | (net (code 69) (name "Net-(J1-PadB59)")

404 | (node (ref J1) (pin B59)))

405 | (net (code 70) (name "Net-(J1-PadA59)")

406 | (node (ref J1) (pin A59)))

407 | (net (code 71) (name "Net-(J1-PadB60)")

408 | (node (ref J1) (pin B60)))

409 | (net (code 72) (name +3.3VA)

410 | (node (ref JP2) (pin 2))

411 | (node (ref J2) (pin 29))

412 | (node (ref J3) (pin 29)))

413 | (net (code 73) (name +3V3)

414 | (node (ref JP2) (pin 1))

415 | (node (ref J1) (pin B54))

416 | (node (ref J1) (pin B25))

417 | (node (ref J1) (pin B43))

418 | (node (ref J1) (pin B41))

419 | (node (ref J1) (pin B31))

420 | (node (ref J1) (pin B36))

421 | (node (ref J1) (pin A27))

422 | (node (ref J1) (pin A21))

423 | (node (ref J1) (pin A53))

424 | (node (ref J1) (pin A45))

425 | (node (ref J1) (pin A39))

426 | (node (ref J1) (pin A33)))

427 | (net (code 74) (name +5V)

428 | (node (ref J1) (pin A62))

429 | (node (ref J1) (pin B61))

430 | (node (ref J1) (pin B62))

431 | (node (ref J1) (pin A5))

432 | (node (ref J1) (pin B5))

433 | (node (ref J1) (pin A61))

434 | (node (ref J1) (pin A8))

435 | (node (ref JP1) (pin 1))

436 | (node (ref J1) (pin B6)))

437 | (net (code 75) (name "Net-(J3-Pad3)")

438 | (node (ref J3) (pin 3)))

439 | (net (code 76) (name "Net-(J3-Pad1)")

440 | (node (ref J3) (pin 1)))

441 | (net (code 77) (name "Net-(J2-Pad3)")

442 | (node (ref J2) (pin 3)))

443 | (net (code 78) (name "Net-(J2-Pad1)")

444 | (node (ref J2) (pin 1)))

445 | (net (code 79) (name "Net-(J1-PadB2)")

446 | (node (ref J1) (pin B2)))

447 | (net (code 80) (name "Net-(J1-PadB14)")

448 | (node (ref J1) (pin B14)))

449 | (net (code 81) (name "Net-(J1-PadB10)")

450 | (node (ref J1) (pin B10)))

451 | (net (code 82) (name "Net-(J1-PadB1)")

452 | (node (ref J1) (pin B1)))

453 | (net (code 83) (name "Net-(J1-PadA9)")

454 | (node (ref J1) (pin A9)))

455 | (net (code 84) (name "Net-(J1-PadA60)")

456 | (node (ref J1) (pin A60)))

457 | (net (code 85) (name JTAG)

458 | (node (ref J1) (pin A4))

459 | (node (ref J1) (pin B4)))

460 | (net (code 86) (name "Net-(J3-Pad35)")

461 | (node (ref J3) (pin 35)))

462 | (net (code 87) (name "Net-(J3-Pad9)")

463 | (node (ref J3) (pin 9)))

464 | (net (code 88) (name "Net-(J3-Pad8)")

465 | (node (ref J3) (pin 8)))

466 | (net (code 89) (name "Net-(J3-Pad7)")

467 | (node (ref J3) (pin 7)))

468 | (net (code 90) (name "Net-(J3-Pad6)")

469 | (node (ref J3) (pin 6)))

470 | (net (code 91) (name "Net-(J3-Pad5)")

471 | (node (ref J3) (pin 5)))

472 | (net (code 92) (name "Net-(J3-Pad40)")

473 | (node (ref J3) (pin 40)))

474 | (net (code 93) (name "Net-(J3-Pad4)")

475 | (node (ref J3) (pin 4)))

476 | (net (code 94) (name "Net-(J3-Pad39)")

477 | (node (ref J3) (pin 39)))

478 | (net (code 95) (name "Net-(J3-Pad38)")

479 | (node (ref J3) (pin 38)))

480 | (net (code 96) (name "Net-(J3-Pad37)")

481 | (node (ref J3) (pin 37)))

482 | (net (code 97) (name "Net-(J3-Pad36)")

483 | (node (ref J3) (pin 36)))

484 | (net (code 98) (name "Net-(J3-Pad34)")

485 | (node (ref J3) (pin 34)))

486 | (net (code 99) (name "Net-(J3-Pad33)")

487 | (node (ref J3) (pin 33)))

488 | (net (code 100) (name "Net-(J3-Pad32)")

489 | (node (ref J3) (pin 32)))

490 | (net (code 101) (name "Net-(J3-Pad31)")

491 | (node (ref J3) (pin 31)))

492 | (net (code 102) (name "Net-(J3-Pad28)")

493 | (node (ref J3) (pin 28)))

494 | (net (code 103) (name "Net-(J3-Pad27)")

495 | (node (ref J3) (pin 27)))

496 | (net (code 104) (name "Net-(J3-Pad26)")

497 | (node (ref J3) (pin 26)))

498 | (net (code 105) (name "Net-(J3-Pad25)")

499 | (node (ref J3) (pin 25)))

500 | (net (code 106) (name "Net-(J3-Pad24)")

501 | (node (ref J3) (pin 24)))

502 | (net (code 107) (name "Net-(J3-Pad23)")

503 | (node (ref J3) (pin 23)))

504 | (net (code 108) (name "Net-(J3-Pad22)")

505 | (node (ref J3) (pin 22)))

506 | (net (code 109) (name "Net-(J2-Pad21)")

507 | (node (ref J2) (pin 21)))

508 | (net (code 110) (name "Net-(J2-Pad33)")

509 | (node (ref J2) (pin 33)))

510 | (net (code 111) (name "Net-(J2-Pad32)")

511 | (node (ref J2) (pin 32)))

512 | (net (code 112) (name "Net-(J2-Pad31)")

513 | (node (ref J2) (pin 31)))

514 | (net (code 113) (name "Net-(J2-Pad28)")

515 | (node (ref J2) (pin 28)))

516 | (net (code 114) (name "Net-(J2-Pad27)")

517 | (node (ref J2) (pin 27)))

518 | (net (code 115) (name "Net-(J2-Pad26)")

519 | (node (ref J2) (pin 26)))

520 | (net (code 116) (name "Net-(J2-Pad25)")

521 | (node (ref J2) (pin 25)))

522 | (net (code 117) (name "Net-(J2-Pad24)")

523 | (node (ref J2) (pin 24)))

524 | (net (code 118) (name "Net-(J2-Pad23)")

525 | (node (ref J2) (pin 23)))

526 | (net (code 119) (name "Net-(J2-Pad22)")

527 | (node (ref J2) (pin 22)))

528 | (net (code 120) (name "Net-(J2-Pad34)")

529 | (node (ref J2) (pin 34)))

530 | (net (code 121) (name "Net-(J2-Pad20)")

531 | (node (ref J2) (pin 20)))

532 | (net (code 122) (name "Net-(J2-Pad2)")

533 | (node (ref J2) (pin 2)))

534 | (net (code 123) (name "Net-(J2-Pad19)")

535 | (node (ref J2) (pin 19)))

536 | (net (code 124) (name "Net-(J2-Pad18)")

537 | (node (ref J2) (pin 18)))

538 | (net (code 125) (name "Net-(J2-Pad17)")

539 | (node (ref J2) (pin 17)))

540 | (net (code 126) (name "Net-(J2-Pad16)")

541 | (node (ref J2) (pin 16)))

542 | (net (code 127) (name "Net-(J2-Pad15)")

543 | (node (ref J2) (pin 15)))

544 | (net (code 128) (name "Net-(J2-Pad14)")

545 | (node (ref J2) (pin 14)))

546 | (net (code 129) (name "Net-(J2-Pad13)")

547 | (node (ref J2) (pin 13)))

548 | (net (code 130) (name "Net-(J2-Pad10)")

549 | (node (ref J2) (pin 10)))

550 | (net (code 131) (name "Net-(J3-Pad21)")

551 | (node (ref J3) (pin 21)))

552 | (net (code 132) (name "Net-(J3-Pad20)")

553 | (node (ref J3) (pin 20)))

554 | (net (code 133) (name "Net-(J3-Pad2)")

555 | (node (ref J3) (pin 2)))

556 | (net (code 134) (name "Net-(J3-Pad19)")

557 | (node (ref J3) (pin 19)))

558 | (net (code 135) (name "Net-(J3-Pad18)")

559 | (node (ref J3) (pin 18)))

560 | (net (code 136) (name "Net-(J3-Pad17)")

561 | (node (ref J3) (pin 17)))

562 | (net (code 137) (name "Net-(J3-Pad16)")

563 | (node (ref J3) (pin 16)))

564 | (net (code 138) (name "Net-(J3-Pad15)")

565 | (node (ref J3) (pin 15)))

566 | (net (code 139) (name "Net-(J3-Pad14)")

567 | (node (ref J3) (pin 14)))

568 | (net (code 140) (name "Net-(J3-Pad13)")

569 | (node (ref J3) (pin 13)))

570 | (net (code 141) (name "Net-(J3-Pad10)")

571 | (node (ref J3) (pin 10)))

572 | (net (code 142) (name "Net-(J2-Pad9)")

573 | (node (ref J2) (pin 9)))

574 | (net (code 143) (name "Net-(J2-Pad8)")

575 | (node (ref J2) (pin 8)))

576 | (net (code 144) (name "Net-(J2-Pad7)")

577 | (node (ref J2) (pin 7)))

578 | (net (code 145) (name "Net-(J2-Pad6)")

579 | (node (ref J2) (pin 6)))

580 | (net (code 146) (name "Net-(J2-Pad5)")

581 | (node (ref J2) (pin 5)))

582 | (net (code 147) (name "Net-(J2-Pad40)")

583 | (node (ref J2) (pin 40)))

584 | (net (code 148) (name "Net-(J2-Pad4)")

585 | (node (ref J2) (pin 4)))

586 | (net (code 149) (name "Net-(J2-Pad39)")

587 | (node (ref J2) (pin 39)))

588 | (net (code 150) (name "Net-(J2-Pad38)")

589 | (node (ref J2) (pin 38)))

590 | (net (code 151) (name "Net-(J2-Pad37)")

591 | (node (ref J2) (pin 37)))

592 | (net (code 152) (name "Net-(J2-Pad36)")

593 | (node (ref J2) (pin 36)))

594 | (net (code 153) (name "Net-(J2-Pad35)")

595 | (node (ref J2) (pin 35)))))

--------------------------------------------------------------------------------

/pci2nano.pro:

--------------------------------------------------------------------------------

1 | update=9/27/2019 10:22:09 AM

2 | version=1

3 | last_client=kicad

4 | [general]

5 | version=1

6 | RootSch=

7 | BoardNm=

8 | [cvpcb]

9 | version=1

10 | NetIExt=net

11 | [eeschema]

12 | version=1

13 | LibDir=

14 | [eeschema/libraries]

15 | [schematic_editor]

16 | version=1

17 | PageLayoutDescrFile=

18 | PlotDirectoryName=

19 | SubpartIdSeparator=0

20 | SubpartFirstId=65

21 | NetFmtName=Pcbnew

22 | SpiceAjustPassiveValues=0

23 | LabSize=50

24 | ERC_TestSimilarLabels=1

25 | [pcbnew]

26 | version=1

27 | PageLayoutDescrFile=

28 | LastNetListRead=pci2nano.net

29 | CopperLayerCount=2

30 | BoardThickness=1.6

31 | AllowMicroVias=0

32 | AllowBlindVias=0

33 | RequireCourtyardDefinitions=0

34 | ProhibitOverlappingCourtyards=1

35 | MinTrackWidth=0.1524

36 | MinViaDiameter=0.4

37 | MinViaDrill=0.254

38 | MinMicroViaDiameter=0.2

39 | MinMicroViaDrill=0.09999999999999999

40 | MinHoleToHole=0.25

41 | TrackWidth1=0.25

42 | TrackWidth2=0.16

43 | TrackWidth3=0.4

44 | ViaDiameter1=0.8

45 | ViaDrill1=0.4

46 | dPairWidth1=0.2

47 | dPairGap1=0.25

48 | dPairViaGap1=0.25

49 | SilkLineWidth=0.12

50 | SilkTextSizeV=1

51 | SilkTextSizeH=1

52 | SilkTextSizeThickness=0.15

53 | SilkTextItalic=0

54 | SilkTextUpright=1

55 | CopperLineWidth=0.2

56 | CopperTextSizeV=1.5

57 | CopperTextSizeH=1.5

58 | CopperTextThickness=0.3

59 | CopperTextItalic=0

60 | CopperTextUpright=1

61 | EdgeCutLineWidth=0.05

62 | CourtyardLineWidth=0.05

63 | OthersLineWidth=0.15

64 | OthersTextSizeV=1

65 | OthersTextSizeH=1

66 | OthersTextSizeThickness=0.15

67 | OthersTextItalic=0

68 | OthersTextUpright=1

69 | SolderMaskClearance=0.051

70 | SolderMaskMinWidth=0.25

71 | SolderPasteClearance=0

72 | SolderPasteRatio=-0

73 | [pcbnew/Layer.F.Cu]

74 | Name=F.Cu

75 | Type=0

76 | Enabled=1

77 | [pcbnew/Layer.In1.Cu]

78 | Name=In1.Cu

79 | Type=0

80 | Enabled=0

81 | [pcbnew/Layer.In2.Cu]

82 | Name=In2.Cu

83 | Type=0

84 | Enabled=0

85 | [pcbnew/Layer.In3.Cu]

86 | Name=In3.Cu

87 | Type=0

88 | Enabled=0

89 | [pcbnew/Layer.In4.Cu]

90 | Name=In4.Cu

91 | Type=0

92 | Enabled=0

93 | [pcbnew/Layer.In5.Cu]

94 | Name=In5.Cu

95 | Type=0

96 | Enabled=0

97 | [pcbnew/Layer.In6.Cu]

98 | Name=In6.Cu

99 | Type=0

100 | Enabled=0

101 | [pcbnew/Layer.In7.Cu]

102 | Name=In7.Cu

103 | Type=0

104 | Enabled=0

105 | [pcbnew/Layer.In8.Cu]

106 | Name=In8.Cu

107 | Type=0

108 | Enabled=0

109 | [pcbnew/Layer.In9.Cu]

110 | Name=In9.Cu

111 | Type=0

112 | Enabled=0

113 | [pcbnew/Layer.In10.Cu]

114 | Name=In10.Cu

115 | Type=0

116 | Enabled=0

117 | [pcbnew/Layer.In11.Cu]

118 | Name=In11.Cu

119 | Type=0

120 | Enabled=0

121 | [pcbnew/Layer.In12.Cu]

122 | Name=In12.Cu

123 | Type=0

124 | Enabled=0

125 | [pcbnew/Layer.In13.Cu]

126 | Name=In13.Cu

127 | Type=0

128 | Enabled=0

129 | [pcbnew/Layer.In14.Cu]

130 | Name=In14.Cu

131 | Type=0

132 | Enabled=0

133 | [pcbnew/Layer.In15.Cu]

134 | Name=In15.Cu

135 | Type=0

136 | Enabled=0

137 | [pcbnew/Layer.In16.Cu]

138 | Name=In16.Cu

139 | Type=0

140 | Enabled=0

141 | [pcbnew/Layer.In17.Cu]

142 | Name=In17.Cu

143 | Type=0

144 | Enabled=0

145 | [pcbnew/Layer.In18.Cu]

146 | Name=In18.Cu

147 | Type=0

148 | Enabled=0

149 | [pcbnew/Layer.In19.Cu]

150 | Name=In19.Cu

151 | Type=0

152 | Enabled=0

153 | [pcbnew/Layer.In20.Cu]

154 | Name=In20.Cu

155 | Type=0

156 | Enabled=0

157 | [pcbnew/Layer.In21.Cu]

158 | Name=In21.Cu

159 | Type=0

160 | Enabled=0

161 | [pcbnew/Layer.In22.Cu]

162 | Name=In22.Cu

163 | Type=0

164 | Enabled=0

165 | [pcbnew/Layer.In23.Cu]

166 | Name=In23.Cu

167 | Type=0

168 | Enabled=0

169 | [pcbnew/Layer.In24.Cu]

170 | Name=In24.Cu

171 | Type=0

172 | Enabled=0

173 | [pcbnew/Layer.In25.Cu]

174 | Name=In25.Cu

175 | Type=0

176 | Enabled=0

177 | [pcbnew/Layer.In26.Cu]

178 | Name=In26.Cu

179 | Type=0

180 | Enabled=0

181 | [pcbnew/Layer.In27.Cu]