├── .gitignore

├── blinky_test.bin

├── Design

├── bootloader.png

├── memory_map.png

├── terminal-putty.png

├── stm32f100-pinout.png

└── terminal-teraterm.png

├── Drivers

├── CMSIS

│ ├── Device

│ │ └── ST

│ │ │ └── STM32F1xx

│ │ │ └── Include

│ │ │ ├── stm32f1xx.h

│ │ │ ├── stm32f100xb.h

│ │ │ └── system_stm32f1xx.h

│ └── Include

│ │ ├── core_cmFunc.h

│ │ ├── core_cmInstr.h

│ │ ├── core_cmSimd.h

│ │ ├── arm_const_structs.h

│ │ └── arm_common_tables.h

└── STM32F1xx_HAL_Driver

│ ├── Src

│ └── stm32f1xx_hal_gpio_ex.c

│ └── Inc

│ ├── stm32f1xx_hal_def.h

│ ├── stm32f1xx_hal_flash.h

│ ├── stm32f1xx_hal.h

│ ├── stm32f1xx_hal_gpio.h

│ ├── stm32f1xx_hal_pwr.h

│ └── stm32f1xx_hal_dma_ex.h

├── Inc

├── uart.h

├── flash.h

├── xmodem.h

├── stm32f1xx_it.h

├── main.h

└── stm32f1xx_hal_conf.h

├── LICENSE

├── Src

├── uart.c

├── flash.c

├── stm32f1xx_hal_msp.c

├── stm32f1xx_it.c

├── xmodem.c

└── main.c

├── .project

├── .mxproject

├── Bootloader.ioc

├── README.md

├── STM32F100RB_FLASH.ld

└── startup

└── startup_stm32f100xb.s

/.gitignore:

--------------------------------------------------------------------------------

1 | .settings

2 | Debug/

3 | Release/

4 | *.launch

5 | !blinky_test.bin

--------------------------------------------------------------------------------

/blinky_test.bin:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/ferenc-nemeth/stm32-bootloader/HEAD/blinky_test.bin

--------------------------------------------------------------------------------

/Design/bootloader.png:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/ferenc-nemeth/stm32-bootloader/HEAD/Design/bootloader.png

--------------------------------------------------------------------------------

/Design/memory_map.png:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/ferenc-nemeth/stm32-bootloader/HEAD/Design/memory_map.png

--------------------------------------------------------------------------------

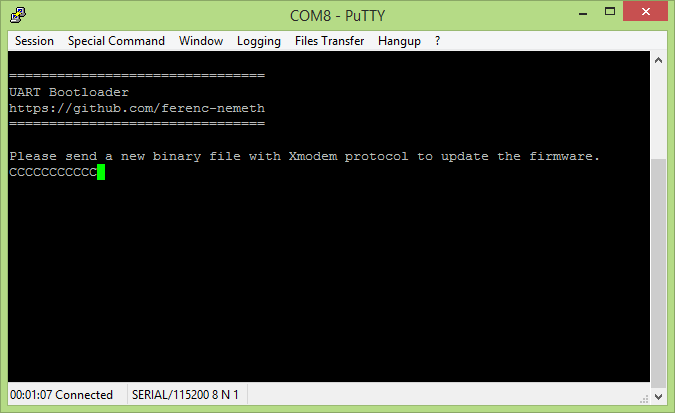

/Design/terminal-putty.png:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/ferenc-nemeth/stm32-bootloader/HEAD/Design/terminal-putty.png

--------------------------------------------------------------------------------

/Design/stm32f100-pinout.png:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/ferenc-nemeth/stm32-bootloader/HEAD/Design/stm32f100-pinout.png

--------------------------------------------------------------------------------

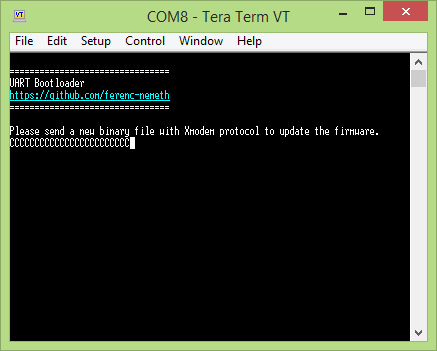

/Design/terminal-teraterm.png:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/ferenc-nemeth/stm32-bootloader/HEAD/Design/terminal-teraterm.png

--------------------------------------------------------------------------------

/Drivers/CMSIS/Device/ST/STM32F1xx/Include/stm32f1xx.h:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/ferenc-nemeth/stm32-bootloader/HEAD/Drivers/CMSIS/Device/ST/STM32F1xx/Include/stm32f1xx.h

--------------------------------------------------------------------------------

/Drivers/CMSIS/Device/ST/STM32F1xx/Include/stm32f100xb.h:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/ferenc-nemeth/stm32-bootloader/HEAD/Drivers/CMSIS/Device/ST/STM32F1xx/Include/stm32f100xb.h

--------------------------------------------------------------------------------

/Inc/uart.h:

--------------------------------------------------------------------------------

1 | /**

2 | * @file uart.h

3 | * @author Ferenc Nemeth

4 | * @date 21 Dec 2018

5 | * @brief This module is a layer between the HAL UART functions and my Xmodem protocol.

6 | *

7 | * Copyright (c) 2018 Ferenc Nemeth - https://github.com/ferenc-nemeth

8 | */

9 |

10 | #ifndef UART_H_

11 | #define UART_H_

12 |

13 | #include "stm32f1xx_hal.h"

14 |

15 | extern UART_HandleTypeDef huart1;

16 |

17 | /* Timeout for HAL. */

18 | #define UART_TIMEOUT ((uint16_t)1000u)

19 |

20 | /* Status report for the functions. */

21 | typedef enum {

22 | UART_OK = 0x00u, /**< The action was successful. */

23 | UART_ERROR = 0xFFu /**< Generic error. */

24 | } uart_status;

25 |

26 | uart_status uart_receive(uint8_t *data, uint16_t length);

27 | uart_status uart_transmit_str(uint8_t *data);

28 | uart_status uart_transmit_ch(uint8_t data);

29 |

30 |

31 | #endif /* UART_H_ */

32 |

--------------------------------------------------------------------------------

/LICENSE:

--------------------------------------------------------------------------------

1 | MIT License

2 |

3 | Copyright (c) 2018 Ferenc Németh - https://github.com/ferenc-nemeth/

4 |

5 | Permission is hereby granted, free of charge, to any person obtaining a copy

6 | of this software and associated documentation files (the "Software"), to deal

7 | in the Software without restriction, including without limitation the rights

8 | to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

9 | copies of the Software, and to permit persons to whom the Software is

10 | furnished to do so, subject to the following conditions:

11 |

12 | The above copyright notice and this permission notice shall be included in all

13 | copies or substantial portions of the Software.

14 |

15 | THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

16 | IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

17 | FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

18 | AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

19 | LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

20 | OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE

21 | SOFTWARE.

22 |

--------------------------------------------------------------------------------

/Inc/flash.h:

--------------------------------------------------------------------------------

1 | /**

2 | * @file flash.h

3 | * @author Ferenc Nemeth

4 | * @date 21 Dec 2018

5 | * @brief This module handles the memory related functions.

6 | *

7 | * Copyright (c) 2018 Ferenc Nemeth - https://github.com/ferenc-nemeth

8 | */

9 |

10 | #ifndef FLASH_H_

11 | #define FLASH_H_

12 |

13 | #include "stm32f1xx_hal.h"

14 |

15 | /* Start and end addresses of the user application. */

16 | #define FLASH_APP_START_ADDRESS ((uint32_t)0x08008000u)

17 | #define FLASH_APP_END_ADDRESS ((uint32_t)FLASH_BANK1_END-0x10u) /**< Leave a little extra space at the end. */

18 |

19 | /* Status report for the functions. */

20 | typedef enum {

21 | FLASH_OK = 0x00u, /**< The action was successful. */

22 | FLASH_ERROR_SIZE = 0x01u, /**< The binary is too big. */

23 | FLASH_ERROR_WRITE = 0x02u, /**< Writing failed. */

24 | FLASH_ERROR_READBACK = 0x04u, /**< Writing was successful, but the content of the memory is wrong. */

25 | FLASH_ERROR = 0xFFu /**< Generic error. */

26 | } flash_status;

27 |

28 | flash_status flash_erase(uint32_t address);

29 | flash_status flash_write(uint32_t address, uint32_t *data, uint32_t length);

30 | void flash_jump_to_app(void);

31 |

32 | #endif /* FLASH_H_ */

33 |

--------------------------------------------------------------------------------

/Src/uart.c:

--------------------------------------------------------------------------------

1 | /**

2 | * @file uart.c

3 | * @author Ferenc Nemeth

4 | * @date 21 Dec 2018

5 | * @brief This module is a layer between the HAL UART functions and my Xmodem protocol.

6 | *

7 | * Copyright (c) 2018 Ferenc Nemeth - https://github.com/ferenc-nemeth

8 | */

9 |

10 | #include "uart.h"

11 |

12 | /**

13 | * @brief Receives data from UART.

14 | * @param *data: Array to save the received data.

15 | * @param length: Size of the data.

16 | * @return status: Report about the success of the receiving.

17 | */

18 | uart_status uart_receive(uint8_t *data, uint16_t length)

19 | {

20 | uart_status status = UART_ERROR;

21 |

22 | if (HAL_OK == HAL_UART_Receive(&huart1, data, length, UART_TIMEOUT))

23 | {

24 | status = UART_OK;

25 | }

26 |

27 | return status;

28 | }

29 |

30 | /**

31 | * @brief Transmits a string to UART.

32 | * @param *data: Array of the data.

33 | * @return status: Report about the success of the transmission.

34 | */

35 | uart_status uart_transmit_str(uint8_t *data)

36 | {

37 | uart_status status = UART_ERROR;

38 | uint16_t length = 0u;

39 |

40 | /* Calculate the length. */

41 | while ('\0' != data[length])

42 | {

43 | length++;

44 | }

45 |

46 | if (HAL_OK == HAL_UART_Transmit(&huart1, data, length, UART_TIMEOUT))

47 | {

48 | status = UART_OK;

49 | }

50 |

51 | return status;

52 | }

53 |

54 | /**

55 | * @brief Transmits a single char to UART.

56 | * @param *data: The char.

57 | * @return status: Report about the success of the transmission.

58 | */

59 | uart_status uart_transmit_ch(uint8_t data)

60 | {

61 | uart_status status = UART_ERROR;

62 |

63 | /* Make available the UART module. */

64 | if (HAL_UART_STATE_TIMEOUT == HAL_UART_GetState(&huart1))

65 | {

66 | HAL_UART_Abort(&huart1);

67 | }

68 |

69 | if (HAL_OK == HAL_UART_Transmit(&huart1, &data, 1u, UART_TIMEOUT))

70 | {

71 | status = UART_OK;

72 | }

73 | return status;

74 | }

75 |

--------------------------------------------------------------------------------

/Inc/xmodem.h:

--------------------------------------------------------------------------------

1 | /**

2 | * @file xmodem.h

3 | * @author Ferenc Nemeth

4 | * @date 21 Dec 2018

5 | * @brief This module is the implementation of the Xmodem protocol.

6 | *

7 | * Copyright (c) 2018 Ferenc Nemeth - https://github.com/ferenc-nemeth

8 | */

9 |

10 | #ifndef XMODEM_H_

11 | #define XMODEM_H_

12 |

13 | #include "uart.h"

14 | #include "flash.h"

15 | #include "stdbool.h"

16 |

17 | /* Xmodem (128 bytes) packet format

18 | * Byte 0: Header

19 | * Byte 1: Packet number

20 | * Byte 2: Packet number complement

21 | * Bytes 3-130: Data

22 | * Bytes 131-132: CRC

23 | */

24 |

25 | /* Xmodem (1024 bytes) packet format

26 | * Byte 0: Header

27 | * Byte 1: Packet number

28 | * Byte 2: Packet number complement

29 | * Bytes 3-1026: Data

30 | * Bytes 1027-1028: CRC

31 | */

32 |

33 | /* Maximum allowed errors (user defined). */

34 | #define X_MAX_ERRORS ((uint8_t)3u)

35 |

36 | /* Sizes of the packets. */

37 | #define X_PACKET_NUMBER_SIZE ((uint16_t)2u)

38 | #define X_PACKET_128_SIZE ((uint16_t)128u)

39 | #define X_PACKET_1024_SIZE ((uint16_t)1024u)

40 | #define X_PACKET_CRC_SIZE ((uint16_t)2u)

41 |

42 | /* Indexes inside packets. */

43 | #define X_PACKET_NUMBER_INDEX ((uint16_t)0u)

44 | #define X_PACKET_NUMBER_COMPLEMENT_INDEX ((uint16_t)1u)

45 | #define X_PACKET_CRC_HIGH_INDEX ((uint16_t)0u)

46 | #define X_PACKET_CRC_LOW_INDEX ((uint16_t)1u)

47 |

48 |

49 | /* Bytes defined by the protocol. */

50 | #define X_SOH ((uint8_t)0x01u) /**< Start Of Header (128 bytes). */

51 | #define X_STX ((uint8_t)0x02u) /**< Start Of Header (1024 bytes). */

52 | #define X_EOT ((uint8_t)0x04u) /**< End Of Transmission. */

53 | #define X_ACK ((uint8_t)0x06u) /**< Acknowledge. */

54 | #define X_NAK ((uint8_t)0x15u) /**< Not Acknowledge. */

55 | #define X_CAN ((uint8_t)0x18u) /**< Cancel. */

56 | #define X_C ((uint8_t)0x43u) /**< ASCII "C" to notify the host we want to use CRC16. */

57 |

58 | /* Status report for the functions. */

59 | typedef enum {

60 | X_OK = 0x00u, /**< The action was successful. */

61 | X_ERROR_CRC = 0x01u, /**< CRC calculation error. */

62 | X_ERROR_NUMBER = 0x02u, /**< Packet number mismatch error. */

63 | X_ERROR_UART = 0x04u, /**< UART communication error. */

64 | X_ERROR_FLASH = 0x08u, /**< Flash related error. */

65 | X_ERROR = 0xFFu /**< Generic error. */

66 | } xmodem_status;

67 |

68 | void xmodem_receive(void);

69 |

70 | #endif /* XMODEM_H_ */

71 |

--------------------------------------------------------------------------------

/.project:

--------------------------------------------------------------------------------

1 |

2 |

3 | Bootloader

4 |

5 |

6 |

7 |

8 |

9 | org.eclipse.cdt.managedbuilder.core.genmakebuilder

10 | clean,full,incremental,

11 |

12 |

13 | ?children?

14 | ?name?=outputEntries\|?children?=?name?=entry\\\\\\\|\\\|\||

15 |

16 |

17 | ?name?

18 |

19 |

20 |

21 | org.eclipse.cdt.make.core.append_environment

22 | true

23 |

24 |

25 | org.eclipse.cdt.make.core.buildArguments

26 |

27 |

28 |

29 | org.eclipse.cdt.make.core.buildCommand

30 | make

31 |

32 |

33 | org.eclipse.cdt.make.core.buildLocation

34 | ${workspace_loc:/STM32100B-EVAL/Debug}

35 |

36 |

37 | org.eclipse.cdt.make.core.contents

38 | org.eclipse.cdt.make.core.activeConfigSettings

39 |

40 |

41 | org.eclipse.cdt.make.core.enableAutoBuild

42 | false

43 |

44 |

45 | org.eclipse.cdt.make.core.enableCleanBuild

46 | true

47 |

48 |

49 | org.eclipse.cdt.make.core.enableFullBuild

50 | true

51 |

52 |

53 | org.eclipse.cdt.make.core.stopOnError

54 | true

55 |

56 |

57 | org.eclipse.cdt.make.core.useDefaultBuildCmd

58 | true

59 |

60 |

61 |

62 |

63 | org.eclipse.cdt.managedbuilder.core.ScannerConfigBuilder

64 |

65 |

66 |

67 |

68 |

69 | org.eclipse.cdt.core.cnature

70 | org.eclipse.cdt.managedbuilder.core.managedBuildNature

71 | org.eclipse.cdt.managedbuilder.core.ScannerConfigNature

72 |

73 |

74 |

75 |

76 |

77 |

--------------------------------------------------------------------------------

/Inc/stm32f1xx_it.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file stm32f1xx_it.h

4 | * @brief This file contains the headers of the interrupt handlers.

5 | ******************************************************************************

6 | *

7 | * COPYRIGHT(c) 2018 STMicroelectronics

8 | *

9 | * Redistribution and use in source and binary forms, with or without modification,

10 | * are permitted provided that the following conditions are met:

11 | * 1. Redistributions of source code must retain the above copyright notice,

12 | * this list of conditions and the following disclaimer.

13 | * 2. Redistributions in binary form must reproduce the above copyright notice,

14 | * this list of conditions and the following disclaimer in the documentation

15 | * and/or other materials provided with the distribution.

16 | * 3. Neither the name of STMicroelectronics nor the names of its contributors

17 | * may be used to endorse or promote products derived from this software

18 | * without specific prior written permission.

19 | *

20 | * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

21 | * AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE

22 | * IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE

23 | * DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE

24 | * FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL

25 | * DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR

26 | * SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER

27 | * CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY,

28 | * OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

29 | * OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

30 | *

31 | ******************************************************************************

32 | */

33 |

34 | /* Define to prevent recursive inclusion -------------------------------------*/

35 | #ifndef __STM32F1xx_IT_H

36 | #define __STM32F1xx_IT_H

37 |

38 | #ifdef __cplusplus

39 | extern "C" {

40 | #endif

41 |

42 | /* Includes ------------------------------------------------------------------*/

43 | #include "stm32f1xx_hal.h"

44 | #include "main.h"

45 | /* Exported types ------------------------------------------------------------*/

46 | /* Exported constants --------------------------------------------------------*/

47 | /* Exported macro ------------------------------------------------------------*/

48 | /* Exported functions ------------------------------------------------------- */

49 |

50 | void NMI_Handler(void);

51 | void HardFault_Handler(void);

52 | void MemManage_Handler(void);

53 | void BusFault_Handler(void);

54 | void UsageFault_Handler(void);

55 | void SVC_Handler(void);

56 | void DebugMon_Handler(void);

57 | void PendSV_Handler(void);

58 | void SysTick_Handler(void);

59 |

60 | #ifdef __cplusplus

61 | }

62 | #endif

63 |

64 | #endif /* __STM32F1xx_IT_H */

65 |

66 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

67 |

--------------------------------------------------------------------------------

/Src/flash.c:

--------------------------------------------------------------------------------

1 | /**

2 | * @file flash.c

3 | * @author Ferenc Nemeth

4 | * @date 21 Dec 2018

5 | * @brief This module handles the memory related functions.

6 | *

7 | * Copyright (c) 2018 Ferenc Nemeth - https://github.com/ferenc-nemeth

8 | */

9 |

10 | #include "flash.h"

11 |

12 | /* Function pointer for jumping to user application. */

13 | typedef void (*fnc_ptr)(void);

14 |

15 | /**

16 | * @brief This function erases the memory.

17 | * @param address: First address to be erased (the last is the end of the flash).

18 | * @return status: Report about the success of the erasing.

19 | */

20 | flash_status flash_erase(uint32_t address)

21 | {

22 | HAL_FLASH_Unlock();

23 |

24 | flash_status status = FLASH_ERROR;

25 | FLASH_EraseInitTypeDef erase_init;

26 | uint32_t error = 0u;

27 |

28 | erase_init.TypeErase = FLASH_TYPEERASE_PAGES;

29 | erase_init.PageAddress = address;

30 | erase_init.Banks = FLASH_BANK_1;

31 | /* Calculate the number of pages from "address" and the end of flash. */

32 | erase_init.NbPages = (FLASH_BANK1_END - address) / FLASH_PAGE_SIZE;

33 | /* Do the actual erasing. */

34 | if (HAL_OK == HAL_FLASHEx_Erase(&erase_init, &error))

35 | {

36 | status = FLASH_OK;

37 | }

38 |

39 | HAL_FLASH_Lock();

40 |

41 | return status;

42 | }

43 |

44 | /**

45 | * @brief This function flashes the memory.

46 | * @param address: First address to be written to.

47 | * @param *data: Array of the data that we want to write.

48 | * @param *length: Size of the array.

49 | * @return status: Report about the success of the writing.

50 | */

51 | flash_status flash_write(uint32_t address, uint32_t *data, uint32_t length)

52 | {

53 | flash_status status = FLASH_OK;

54 |

55 | HAL_FLASH_Unlock();

56 |

57 | /* Loop through the array. */

58 | for (uint32_t i = 0u; (i < length) && (FLASH_OK == status); i++)

59 | {

60 | /* If we reached the end of the memory, then report an error and don't do anything else.*/

61 | if (FLASH_APP_END_ADDRESS <= address)

62 | {

63 | status |= FLASH_ERROR_SIZE;

64 | }

65 | else

66 | {

67 | /* The actual flashing. If there is an error, then report it. */

68 | if (HAL_OK != HAL_FLASH_Program(FLASH_TYPEPROGRAM_WORD, address, data[i]))

69 | {

70 | status |= FLASH_ERROR_WRITE;

71 | }

72 | /* Read back the content of the memory. If it is wrong, then report an error. */

73 | if (((data[i])) != (*(volatile uint32_t*)address))

74 | {

75 | status |= FLASH_ERROR_READBACK;

76 | }

77 |

78 | /* Shift the address by a word. */

79 | address += 4u;

80 | }

81 | }

82 |

83 | HAL_FLASH_Lock();

84 |

85 | return status;

86 | }

87 |

88 | /**

89 | * @brief Actually jumps to the user application.

90 | * @param void

91 | * @return void

92 | */

93 | void flash_jump_to_app(void)

94 | {

95 | /* Function pointer to the address of the user application. */

96 | fnc_ptr jump_to_app;

97 | jump_to_app = (fnc_ptr)(*(volatile uint32_t*) (FLASH_APP_START_ADDRESS+4u));

98 | HAL_DeInit();

99 | /* Change the main stack pointer. */

100 | __set_MSP(*(volatile uint32_t*)FLASH_APP_START_ADDRESS);

101 | jump_to_app();

102 | }

103 |

104 |

--------------------------------------------------------------------------------

/.mxproject:

--------------------------------------------------------------------------------

1 | [PreviousGenFiles]

2 | HeaderPath=C:/Users/Feco/Documents/STM32/Bootloader/Inc

3 | HeaderFiles=stm32f1xx_it.h;stm32f1xx_hal_conf.h;main.h;

4 | SourcePath=C:/Users/Feco/Documents/STM32/Bootloader/Src

5 | SourceFiles=stm32f1xx_it.c;stm32f1xx_hal_msp.c;main.c;

6 |

7 | [PreviousLibFiles]

8 | LibFiles=Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_tim.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_tim_ex.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_uart.h;Drivers/STM32F1xx_HAL_Driver/Inc/Legacy/stm32_hal_legacy.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_def.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_rcc.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_rcc_ex.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_gpio.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_gpio_ex.h;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_gpio_ex.c;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_dma_ex.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_dma.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_cortex.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_pwr.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_flash.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_flash_ex.h;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_tim.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_tim_ex.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_uart.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_rcc.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_rcc_ex.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_gpio.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_dma.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_cortex.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_pwr.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_flash.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_flash_ex.c;Drivers/CMSIS/Device/ST/STM32F1xx/Include/stm32f100xb.h;Drivers/CMSIS/Device/ST/STM32F1xx/Include/stm32f1xx.h;Drivers/CMSIS/Device/ST/STM32F1xx/Include/system_stm32f1xx.h;Drivers/CMSIS/Device/ST/STM32F1xx/Source/Templates/system_stm32f1xx.c;Drivers/CMSIS/Include/arm_common_tables.h;Drivers/CMSIS/Include/arm_const_structs.h;Drivers/CMSIS/Include/arm_math.h;Drivers/CMSIS/Include/cmsis_armcc.h;Drivers/CMSIS/Include/cmsis_armcc_V6.h;Drivers/CMSIS/Include/cmsis_gcc.h;Drivers/CMSIS/Include/core_cm0.h;Drivers/CMSIS/Include/core_cm0plus.h;Drivers/CMSIS/Include/core_cm3.h;Drivers/CMSIS/Include/core_cm4.h;Drivers/CMSIS/Include/core_cm7.h;Drivers/CMSIS/Include/core_cmFunc.h;Drivers/CMSIS/Include/core_cmInstr.h;Drivers/CMSIS/Include/core_cmSimd.h;Drivers/CMSIS/Include/core_sc000.h;Drivers/CMSIS/Include/core_sc300.h;

9 |

10 | [PreviousUsedTStudioFiles]

11 | SourceFiles=..\Src\main.c;..\Src\stm32f1xx_it.c;..\Src\stm32f1xx_hal_msp.c;../Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_gpio_ex.c;../Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_tim.c;../Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_tim_ex.c;../Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_uart.c;../Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal.c;../Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_rcc.c;../Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_rcc_ex.c;../Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_gpio.c;../Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_dma.c;../Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_cortex.c;../Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_pwr.c;../Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_flash.c;../Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_flash_ex.c;../\Src/system_stm32f1xx.c;../Drivers/CMSIS/Device/ST/STM32F1xx/Source/Templates/system_stm32f1xx.c;null;

12 | HeaderPath=..\Drivers\STM32F1xx_HAL_Driver\Inc;..\Drivers\STM32F1xx_HAL_Driver\Inc\Legacy;..\Drivers\CMSIS\Device\ST\STM32F1xx\Include;..\Drivers\CMSIS\Include;..\Inc;

13 | CDefines=__weak:__attribute__((weak));__packed:__attribute__((__packed__));

14 |

15 |

--------------------------------------------------------------------------------

/Inc/main.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file : main.h

4 | * @brief : Header for main.c file.

5 | * This file contains the common defines of the application.

6 | ******************************************************************************

7 | ** This notice applies to any and all portions of this file

8 | * that are not between comment pairs USER CODE BEGIN and

9 | * USER CODE END. Other portions of this file, whether

10 | * inserted by the user or by software development tools

11 | * are owned by their respective copyright owners.

12 | *

13 | * COPYRIGHT(c) 2018 STMicroelectronics

14 | *

15 | * Redistribution and use in source and binary forms, with or without modification,

16 | * are permitted provided that the following conditions are met:

17 | * 1. Redistributions of source code must retain the above copyright notice,

18 | * this list of conditions and the following disclaimer.

19 | * 2. Redistributions in binary form must reproduce the above copyright notice,

20 | * this list of conditions and the following disclaimer in the documentation

21 | * and/or other materials provided with the distribution.

22 | * 3. Neither the name of STMicroelectronics nor the names of its contributors

23 | * may be used to endorse or promote products derived from this software

24 | * without specific prior written permission.

25 | *

26 | * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

27 | * AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE

28 | * IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE

29 | * DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE

30 | * FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL

31 | * DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR

32 | * SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER

33 | * CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY,

34 | * OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

35 | * OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

36 | *

37 | ******************************************************************************

38 | */

39 |

40 | /* Define to prevent recursive inclusion -------------------------------------*/

41 | #ifndef __MAIN_H__

42 | #define __MAIN_H__

43 |

44 | /* Includes ------------------------------------------------------------------*/

45 |

46 | /* USER CODE BEGIN Includes */

47 |

48 | /* USER CODE END Includes */

49 |

50 | /* Private define ------------------------------------------------------------*/

51 |

52 | #define BTN_Pin GPIO_PIN_0

53 | #define BTN_GPIO_Port GPIOA

54 | #define LD4_Pin GPIO_PIN_8

55 | #define LD4_GPIO_Port GPIOC

56 | #define LD3_Pin GPIO_PIN_9

57 | #define LD3_GPIO_Port GPIOC

58 | #define TMS_SWDIO_Pin GPIO_PIN_13

59 | #define TMS_SWDIO_GPIO_Port GPIOA

60 | #define TCK_SWCLK_Pin GPIO_PIN_14

61 | #define TCK_SWCLK_GPIO_Port GPIOA

62 |

63 | /* ########################## Assert Selection ############################## */

64 | /**

65 | * @brief Uncomment the line below to expanse the "assert_param" macro in the

66 | * HAL drivers code

67 | */

68 | /* #define USE_FULL_ASSERT 1U */

69 |

70 | /* USER CODE BEGIN Private defines */

71 |

72 | /* USER CODE END Private defines */

73 |

74 | #ifdef __cplusplus

75 | extern "C" {

76 | #endif

77 | void _Error_Handler(char *, int);

78 |

79 | #define Error_Handler() _Error_Handler(__FILE__, __LINE__)

80 | #ifdef __cplusplus

81 | }

82 | #endif

83 |

84 | #endif /* __MAIN_H__ */

85 |

86 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

87 |

--------------------------------------------------------------------------------

/Drivers/CMSIS/Include/core_cmFunc.h:

--------------------------------------------------------------------------------

1 | /**************************************************************************//**

2 | * @file core_cmFunc.h

3 | * @brief CMSIS Cortex-M Core Function Access Header File

4 | * @version V4.30

5 | * @date 20. October 2015

6 | ******************************************************************************/

7 | /* Copyright (c) 2009 - 2015 ARM LIMITED

8 |

9 | All rights reserved.

10 | Redistribution and use in source and binary forms, with or without

11 | modification, are permitted provided that the following conditions are met:

12 | - Redistributions of source code must retain the above copyright

13 | notice, this list of conditions and the following disclaimer.

14 | - Redistributions in binary form must reproduce the above copyright

15 | notice, this list of conditions and the following disclaimer in the

16 | documentation and/or other materials provided with the distribution.

17 | - Neither the name of ARM nor the names of its contributors may be used

18 | to endorse or promote products derived from this software without

19 | specific prior written permission.

20 | *

21 | THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

22 | AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE

23 | IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE

24 | ARE DISCLAIMED. IN NO EVENT SHALL COPYRIGHT HOLDERS AND CONTRIBUTORS BE

25 | LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR

26 | CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF

27 | SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS

28 | INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN

29 | CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE)

30 | ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE

31 | POSSIBILITY OF SUCH DAMAGE.

32 | ---------------------------------------------------------------------------*/

33 |

34 |

35 | #if defined ( __ICCARM__ )

36 | #pragma system_include /* treat file as system include file for MISRA check */

37 | #elif defined(__ARMCC_VERSION) && (__ARMCC_VERSION >= 6010050)

38 | #pragma clang system_header /* treat file as system include file */

39 | #endif

40 |

41 | #ifndef __CORE_CMFUNC_H

42 | #define __CORE_CMFUNC_H

43 |

44 |

45 | /* ########################### Core Function Access ########################### */

46 | /** \ingroup CMSIS_Core_FunctionInterface

47 | \defgroup CMSIS_Core_RegAccFunctions CMSIS Core Register Access Functions

48 | @{

49 | */

50 |

51 | /*------------------ RealView Compiler -----------------*/

52 | #if defined ( __CC_ARM )

53 | #include "cmsis_armcc.h"

54 |

55 | /*------------------ ARM Compiler V6 -------------------*/

56 | #elif defined(__ARMCC_VERSION) && (__ARMCC_VERSION >= 6010050)

57 | #include "cmsis_armcc_V6.h"

58 |

59 | /*------------------ GNU Compiler ----------------------*/

60 | #elif defined ( __GNUC__ )

61 | #include "cmsis_gcc.h"

62 |

63 | /*------------------ ICC Compiler ----------------------*/

64 | #elif defined ( __ICCARM__ )

65 | #include

66 |

67 | /*------------------ TI CCS Compiler -------------------*/

68 | #elif defined ( __TMS470__ )

69 | #include

70 |

71 | /*------------------ TASKING Compiler ------------------*/

72 | #elif defined ( __TASKING__ )

73 | /*

74 | * The CMSIS functions have been implemented as intrinsics in the compiler.

75 | * Please use "carm -?i" to get an up to date list of all intrinsics,

76 | * Including the CMSIS ones.

77 | */

78 |

79 | /*------------------ COSMIC Compiler -------------------*/

80 | #elif defined ( __CSMC__ )

81 | #include

82 |

83 | #endif

84 |

85 | /*@} end of CMSIS_Core_RegAccFunctions */

86 |

87 | #endif /* __CORE_CMFUNC_H */

88 |

--------------------------------------------------------------------------------

/Drivers/CMSIS/Device/ST/STM32F1xx/Include/system_stm32f1xx.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file system_stm32f10x.h

4 | * @author MCD Application Team

5 | * @version V4.2.0

6 | * @date 31-March-2017

7 | * @brief CMSIS Cortex-M3 Device Peripheral Access Layer System Header File.

8 | ******************************************************************************

9 | * @attention

10 | *

11 | * © COPYRIGHT(c) 2017 STMicroelectronics

12 | *

13 | * Redistribution and use in source and binary forms, with or without modification,

14 | * are permitted provided that the following conditions are met:

15 | * 1. Redistributions of source code must retain the above copyright notice,

16 | * this list of conditions and the following disclaimer.

17 | * 2. Redistributions in binary form must reproduce the above copyright notice,

18 | * this list of conditions and the following disclaimer in the documentation

19 | * and/or other materials provided with the distribution.

20 | * 3. Neither the name of STMicroelectronics nor the names of its contributors

21 | * may be used to endorse or promote products derived from this software

22 | * without specific prior written permission.

23 | *

24 | * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

25 | * AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE

26 | * IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE

27 | * DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE

28 | * FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL

29 | * DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR

30 | * SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER

31 | * CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY,

32 | * OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

33 | * OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

34 | *

35 | ******************************************************************************

36 | */

37 |

38 | /** @addtogroup CMSIS

39 | * @{

40 | */

41 |

42 | /** @addtogroup stm32f10x_system

43 | * @{

44 | */

45 |

46 | /**

47 | * @brief Define to prevent recursive inclusion

48 | */

49 | #ifndef __SYSTEM_STM32F10X_H

50 | #define __SYSTEM_STM32F10X_H

51 |

52 | #ifdef __cplusplus

53 | extern "C" {

54 | #endif

55 |

56 | /** @addtogroup STM32F10x_System_Includes

57 | * @{

58 | */

59 |

60 | /**

61 | * @}

62 | */

63 |

64 |

65 | /** @addtogroup STM32F10x_System_Exported_types

66 | * @{

67 | */

68 |

69 | extern uint32_t SystemCoreClock; /*!< System Clock Frequency (Core Clock) */

70 | extern const uint8_t AHBPrescTable[16U]; /*!< AHB prescalers table values */

71 | extern const uint8_t APBPrescTable[8U]; /*!< APB prescalers table values */

72 |

73 | /**

74 | * @}

75 | */

76 |

77 | /** @addtogroup STM32F10x_System_Exported_Constants

78 | * @{

79 | */

80 |

81 | /**

82 | * @}

83 | */

84 |

85 | /** @addtogroup STM32F10x_System_Exported_Macros

86 | * @{

87 | */

88 |

89 | /**

90 | * @}

91 | */

92 |

93 | /** @addtogroup STM32F10x_System_Exported_Functions

94 | * @{

95 | */

96 |

97 | extern void SystemInit(void);

98 | extern void SystemCoreClockUpdate(void);

99 | /**

100 | * @}

101 | */

102 |

103 | #ifdef __cplusplus

104 | }

105 | #endif

106 |

107 | #endif /*__SYSTEM_STM32F10X_H */

108 |

109 | /**

110 | * @}

111 | */

112 |

113 | /**

114 | * @}

115 | */

116 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

117 |

--------------------------------------------------------------------------------

/Drivers/CMSIS/Include/core_cmInstr.h:

--------------------------------------------------------------------------------

1 | /**************************************************************************//**

2 | * @file core_cmInstr.h

3 | * @brief CMSIS Cortex-M Core Instruction Access Header File

4 | * @version V4.30

5 | * @date 20. October 2015

6 | ******************************************************************************/

7 | /* Copyright (c) 2009 - 2015 ARM LIMITED

8 |

9 | All rights reserved.

10 | Redistribution and use in source and binary forms, with or without

11 | modification, are permitted provided that the following conditions are met:

12 | - Redistributions of source code must retain the above copyright

13 | notice, this list of conditions and the following disclaimer.

14 | - Redistributions in binary form must reproduce the above copyright

15 | notice, this list of conditions and the following disclaimer in the

16 | documentation and/or other materials provided with the distribution.

17 | - Neither the name of ARM nor the names of its contributors may be used

18 | to endorse or promote products derived from this software without

19 | specific prior written permission.

20 | *

21 | THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

22 | AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE

23 | IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE

24 | ARE DISCLAIMED. IN NO EVENT SHALL COPYRIGHT HOLDERS AND CONTRIBUTORS BE

25 | LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR

26 | CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF

27 | SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS

28 | INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN

29 | CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE)

30 | ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE

31 | POSSIBILITY OF SUCH DAMAGE.

32 | ---------------------------------------------------------------------------*/

33 |

34 |

35 | #if defined ( __ICCARM__ )

36 | #pragma system_include /* treat file as system include file for MISRA check */

37 | #elif defined(__ARMCC_VERSION) && (__ARMCC_VERSION >= 6010050)

38 | #pragma clang system_header /* treat file as system include file */

39 | #endif

40 |

41 | #ifndef __CORE_CMINSTR_H

42 | #define __CORE_CMINSTR_H

43 |

44 |

45 | /* ########################## Core Instruction Access ######################### */

46 | /** \defgroup CMSIS_Core_InstructionInterface CMSIS Core Instruction Interface

47 | Access to dedicated instructions

48 | @{

49 | */

50 |

51 | /*------------------ RealView Compiler -----------------*/

52 | #if defined ( __CC_ARM )

53 | #include "cmsis_armcc.h"

54 |

55 | /*------------------ ARM Compiler V6 -------------------*/

56 | #elif defined(__ARMCC_VERSION) && (__ARMCC_VERSION >= 6010050)

57 | #include "cmsis_armcc_V6.h"

58 |

59 | /*------------------ GNU Compiler ----------------------*/

60 | #elif defined ( __GNUC__ )

61 | #include "cmsis_gcc.h"

62 |

63 | /*------------------ ICC Compiler ----------------------*/

64 | #elif defined ( __ICCARM__ )

65 | #include

66 |

67 | /*------------------ TI CCS Compiler -------------------*/

68 | #elif defined ( __TMS470__ )

69 | #include

70 |

71 | /*------------------ TASKING Compiler ------------------*/

72 | #elif defined ( __TASKING__ )

73 | /*

74 | * The CMSIS functions have been implemented as intrinsics in the compiler.

75 | * Please use "carm -?i" to get an up to date list of all intrinsics,

76 | * Including the CMSIS ones.

77 | */

78 |

79 | /*------------------ COSMIC Compiler -------------------*/

80 | #elif defined ( __CSMC__ )

81 | #include

82 |

83 | #endif

84 |

85 | /*@}*/ /* end of group CMSIS_Core_InstructionInterface */

86 |

87 | #endif /* __CORE_CMINSTR_H */

88 |

--------------------------------------------------------------------------------

/Drivers/CMSIS/Include/core_cmSimd.h:

--------------------------------------------------------------------------------

1 | /**************************************************************************//**

2 | * @file core_cmSimd.h

3 | * @brief CMSIS Cortex-M SIMD Header File

4 | * @version V4.30

5 | * @date 20. October 2015

6 | ******************************************************************************/

7 | /* Copyright (c) 2009 - 2015 ARM LIMITED

8 |

9 | All rights reserved.

10 | Redistribution and use in source and binary forms, with or without

11 | modification, are permitted provided that the following conditions are met:

12 | - Redistributions of source code must retain the above copyright

13 | notice, this list of conditions and the following disclaimer.

14 | - Redistributions in binary form must reproduce the above copyright

15 | notice, this list of conditions and the following disclaimer in the

16 | documentation and/or other materials provided with the distribution.

17 | - Neither the name of ARM nor the names of its contributors may be used

18 | to endorse or promote products derived from this software without

19 | specific prior written permission.

20 | *

21 | THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

22 | AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE

23 | IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE

24 | ARE DISCLAIMED. IN NO EVENT SHALL COPYRIGHT HOLDERS AND CONTRIBUTORS BE

25 | LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR

26 | CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF

27 | SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS

28 | INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN

29 | CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE)

30 | ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE

31 | POSSIBILITY OF SUCH DAMAGE.

32 | ---------------------------------------------------------------------------*/

33 |

34 |

35 | #if defined ( __ICCARM__ )

36 | #pragma system_include /* treat file as system include file for MISRA check */

37 | #elif defined(__ARMCC_VERSION) && (__ARMCC_VERSION >= 6010050)

38 | #pragma clang system_header /* treat file as system include file */

39 | #endif

40 |

41 | #ifndef __CORE_CMSIMD_H

42 | #define __CORE_CMSIMD_H

43 |

44 | #ifdef __cplusplus

45 | extern "C" {

46 | #endif

47 |

48 |

49 | /* ################### Compiler specific Intrinsics ########################### */

50 | /** \defgroup CMSIS_SIMD_intrinsics CMSIS SIMD Intrinsics

51 | Access to dedicated SIMD instructions

52 | @{

53 | */

54 |

55 | /*------------------ RealView Compiler -----------------*/

56 | #if defined ( __CC_ARM )

57 | #include "cmsis_armcc.h"

58 |

59 | /*------------------ ARM Compiler V6 -------------------*/

60 | #elif defined(__ARMCC_VERSION) && (__ARMCC_VERSION >= 6010050)

61 | #include "cmsis_armcc_V6.h"

62 |

63 | /*------------------ GNU Compiler ----------------------*/

64 | #elif defined ( __GNUC__ )

65 | #include "cmsis_gcc.h"

66 |

67 | /*------------------ ICC Compiler ----------------------*/

68 | #elif defined ( __ICCARM__ )

69 | #include

70 |

71 | /*------------------ TI CCS Compiler -------------------*/

72 | #elif defined ( __TMS470__ )

73 | #include

74 |

75 | /*------------------ TASKING Compiler ------------------*/

76 | #elif defined ( __TASKING__ )

77 | /*

78 | * The CMSIS functions have been implemented as intrinsics in the compiler.

79 | * Please use "carm -?i" to get an up to date list of all intrinsics,

80 | * Including the CMSIS ones.

81 | */

82 |

83 | /*------------------ COSMIC Compiler -------------------*/

84 | #elif defined ( __CSMC__ )

85 | #include

86 |

87 | #endif

88 |

89 | /*@} end of group CMSIS_SIMD_intrinsics */

90 |

91 |

92 | #ifdef __cplusplus

93 | }

94 | #endif

95 |

96 | #endif /* __CORE_CMSIMD_H */

97 |

--------------------------------------------------------------------------------

/Drivers/CMSIS/Include/arm_const_structs.h:

--------------------------------------------------------------------------------

1 | /* ----------------------------------------------------------------------

2 | * Copyright (C) 2010-2014 ARM Limited. All rights reserved.

3 | *

4 | * $Date: 19. March 2015

5 | * $Revision: V.1.4.5

6 | *

7 | * Project: CMSIS DSP Library

8 | * Title: arm_const_structs.h

9 | *

10 | * Description: This file has constant structs that are initialized for

11 | * user convenience. For example, some can be given as

12 | * arguments to the arm_cfft_f32() function.

13 | *

14 | * Target Processor: Cortex-M4/Cortex-M3

15 | *

16 | * Redistribution and use in source and binary forms, with or without

17 | * modification, are permitted provided that the following conditions

18 | * are met:

19 | * - Redistributions of source code must retain the above copyright

20 | * notice, this list of conditions and the following disclaimer.

21 | * - Redistributions in binary form must reproduce the above copyright

22 | * notice, this list of conditions and the following disclaimer in

23 | * the documentation and/or other materials provided with the

24 | * distribution.

25 | * - Neither the name of ARM LIMITED nor the names of its contributors

26 | * may be used to endorse or promote products derived from this

27 | * software without specific prior written permission.

28 | *

29 | * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

30 | * "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

31 | * LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS

32 | * FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE

33 | * COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT,

34 | * INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING,

35 | * BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES;

36 | * LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER

37 | * CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT

38 | * LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN

39 | * ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE

40 | * POSSIBILITY OF SUCH DAMAGE.

41 | * -------------------------------------------------------------------- */

42 |

43 | #ifndef _ARM_CONST_STRUCTS_H

44 | #define _ARM_CONST_STRUCTS_H

45 |

46 | #include "arm_math.h"

47 | #include "arm_common_tables.h"

48 |

49 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len16;

50 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len32;

51 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len64;

52 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len128;

53 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len256;

54 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len512;

55 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len1024;

56 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len2048;

57 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len4096;

58 |

59 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len16;

60 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len32;

61 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len64;

62 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len128;

63 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len256;

64 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len512;

65 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len1024;

66 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len2048;

67 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len4096;

68 |

69 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len16;

70 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len32;

71 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len64;

72 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len128;

73 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len256;

74 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len512;

75 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len1024;

76 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len2048;

77 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len4096;

78 |

79 | #endif

80 |

--------------------------------------------------------------------------------

/Bootloader.ioc:

--------------------------------------------------------------------------------

1 | #MicroXplorer Configuration settings - do not modify

2 | File.Version=6

3 | KeepUserPlacement=true

4 | Mcu.Family=STM32F1

5 | Mcu.IP0=NVIC

6 | Mcu.IP1=RCC

7 | Mcu.IP2=SYS

8 | Mcu.IP3=USART1

9 | Mcu.IPNb=4

10 | Mcu.Name=STM32F100R(8-B)Tx

11 | Mcu.Package=LQFP64

12 | Mcu.Pin0=PD0-OSC_IN

13 | Mcu.Pin1=PD1-OSC_OUT

14 | Mcu.Pin2=PA0-WKUP

15 | Mcu.Pin3=PC8

16 | Mcu.Pin4=PC9

17 | Mcu.Pin5=PA9

18 | Mcu.Pin6=PA10

19 | Mcu.Pin7=PA13

20 | Mcu.Pin8=PA14

21 | Mcu.Pin9=VP_SYS_VS_Systick

22 | Mcu.PinsNb=10

23 | Mcu.ThirdPartyNb=0

24 | Mcu.UserConstants=

25 | Mcu.UserName=STM32F100RBTx

26 | MxCube.Version=4.26.1

27 | MxDb.Version=DB.4.0.261

28 | NVIC.BusFault_IRQn=true\:0\:0\:false\:false\:true\:true

29 | NVIC.DebugMonitor_IRQn=true\:0\:0\:false\:false\:true\:true

30 | NVIC.HardFault_IRQn=true\:0\:0\:false\:false\:true\:true

31 | NVIC.MemoryManagement_IRQn=true\:0\:0\:false\:false\:true\:true

32 | NVIC.NonMaskableInt_IRQn=true\:0\:0\:false\:false\:true\:true

33 | NVIC.PendSV_IRQn=true\:0\:0\:false\:false\:true\:true

34 | NVIC.PriorityGroup=NVIC_PRIORITYGROUP_4

35 | NVIC.SVCall_IRQn=true\:0\:0\:false\:false\:true\:true

36 | NVIC.SysTick_IRQn=true\:0\:0\:false\:false\:true\:true

37 | NVIC.UsageFault_IRQn=true\:0\:0\:false\:false\:true\:true

38 | PA0-WKUP.GPIOParameters=GPIO_Label

39 | PA0-WKUP.GPIO_Label=BTN

40 | PA0-WKUP.Locked=true

41 | PA0-WKUP.Signal=GPIO_Input

42 | PA10.Mode=Asynchronous

43 | PA10.Signal=USART1_RX

44 | PA13.GPIOParameters=GPIO_Label

45 | PA13.GPIO_Label=TMS_SWDIO

46 | PA13.Locked=true

47 | PA13.Mode=Serial_Wire

48 | PA13.Signal=SYS_JTMS-SWDIO

49 | PA14.GPIOParameters=GPIO_Label

50 | PA14.GPIO_Label=TCK_SWCLK

51 | PA14.Locked=true

52 | PA14.Mode=Serial_Wire

53 | PA14.Signal=SYS_JTCK-SWCLK

54 | PA9.Mode=Asynchronous

55 | PA9.Signal=USART1_TX

56 | PC8.GPIOParameters=GPIO_Label

57 | PC8.GPIO_Label=LD4 [Blue]

58 | PC8.Locked=true

59 | PC8.Signal=GPIO_Output

60 | PC9.GPIOParameters=GPIO_Label

61 | PC9.GPIO_Label=LD3 [Green]

62 | PC9.Locked=true

63 | PC9.Signal=GPIO_Output

64 | PCC.Checker=false

65 | PCC.Line=STM32F100 Value Line

66 | PCC.MCU=STM32F100R(8-B)Tx

67 | PCC.PartNumber=STM32F100RBTx

68 | PCC.Seq0=0

69 | PCC.Series=STM32F1

70 | PCC.Temperature=25

71 | PCC.Vdd=3.3

72 | PD0-OSC_IN.Mode=HSE-External-Oscillator

73 | PD0-OSC_IN.Signal=RCC_OSC_IN

74 | PD1-OSC_OUT.Mode=HSE-External-Oscillator

75 | PD1-OSC_OUT.Signal=RCC_OSC_OUT

76 | PinOutPanel.RotationAngle=0

77 | ProjectManager.AskForMigrate=true

78 | ProjectManager.BackupPrevious=false

79 | ProjectManager.CompilerOptimize=6

80 | ProjectManager.ComputerToolchain=false

81 | ProjectManager.CoupleFile=false

82 | ProjectManager.CustomerFirmwarePackage=

83 | ProjectManager.DefaultFWLocation=true

84 | ProjectManager.DeletePrevious=true

85 | ProjectManager.DeviceId=STM32F100RBTx

86 | ProjectManager.FirmwarePackage=STM32Cube FW_F1 V1.6.1

87 | ProjectManager.FreePins=false

88 | ProjectManager.HalAssertFull=false

89 | ProjectManager.HeapSize=0x200

90 | ProjectManager.KeepUserCode=true

91 | ProjectManager.LastFirmware=true

92 | ProjectManager.LibraryCopy=1

93 | ProjectManager.MainLocation=Src

94 | ProjectManager.PreviousToolchain=TrueSTUDIO

95 | ProjectManager.ProjectBuild=false

96 | ProjectManager.ProjectFileName=Bootloader.ioc

97 | ProjectManager.ProjectName=Bootloader

98 | ProjectManager.StackSize=0x400

99 | ProjectManager.TargetToolchain=TrueSTUDIO

100 | ProjectManager.ToolChainLocation=

101 | ProjectManager.UnderRoot=true

102 | ProjectManager.functionlistsort=1-MX_GPIO_Init-GPIO-false-HAL-true,2-SystemClock_Config-RCC-false-HAL-false,3-MX_USART1_UART_Init-USART1-false-HAL-true

103 | RCC.APB1Freq_Value=8000000

104 | RCC.APB2Freq_Value=8000000

105 | RCC.FamilyName=M

106 | RCC.IPParameters=APB1Freq_Value,APB2Freq_Value,FamilyName,PLLCLKFreq_Value,PLLMCOFreq_Value,SYSCLKSource,TimSysFreq_Value

107 | RCC.PLLCLKFreq_Value=8000000

108 | RCC.PLLMCOFreq_Value=4000000

109 | RCC.SYSCLKSource=RCC_SYSCLKSOURCE_HSE

110 | RCC.TimSysFreq_Value=8000000

111 | USART1.IPParameters=VirtualMode

112 | USART1.VirtualMode=VM_ASYNC

113 | VP_SYS_VS_Systick.Mode=SysTick

114 | VP_SYS_VS_Systick.Signal=SYS_VS_Systick

115 | board=STM32VLDISCOVERY

116 | boardIOC=true

117 |

--------------------------------------------------------------------------------

/README.md:

--------------------------------------------------------------------------------

1 | # stm32-bootloader

2 | UART bootloader for STM32 microcontroller.

3 |

4 | ### Table of contents

5 | - [Introduction](#introduction)

6 | - [How it works](#how-it-works)

7 | - [Overall](#overall)

8 | - [Memory map](#memory-map)

9 | - [Code](#code)

10 | - [How to use it](#how-to-use-it)

11 | - [Embedded](#embedded)

12 | - [PC](#pc)

13 | - [Porting](#porting)

14 | - [References](#references)

15 |

16 | ### Introduction

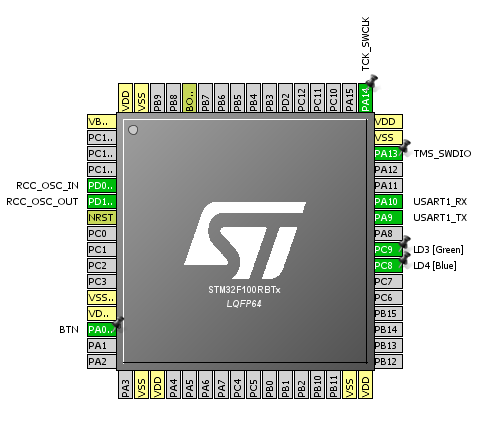

17 | A bootloader for STM32F100 (STM32VLDISCOVERY board) [[1]](#references) with UART and Xmodem protocol [[2]](#references)[[3]](#references).

18 | The software is created with Atollic trueSTUDIO and the drivers are generated with CubeMX.

19 |

20 | Main features:

21 | - UART & Xmodem protocol

22 | - CRC16 checksum

23 | - Supports 128 and 1024 bytes data length

24 |

25 | ### How it works

26 | #### Overall

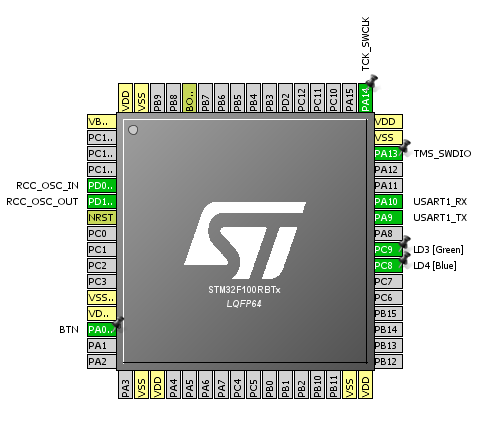

27 | The bootloader was developed for STM32VLDISCOVERY board, the only extra thing needed is an USB-UART module on PA10 (RX) and PA9 (TX) pins.

28 |

29 |

30 | *Figure 1. Pinout of the system.*

31 |

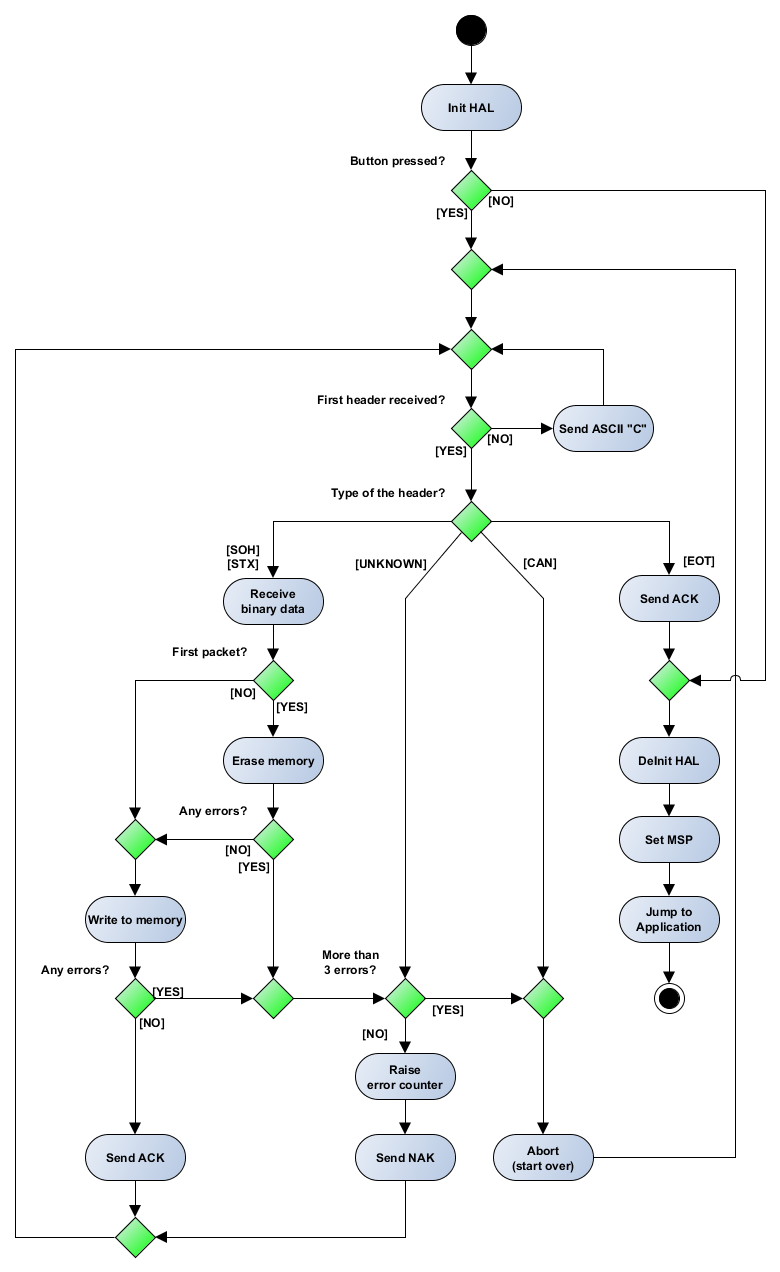

32 | After start-up, the system sends a welcome message through UART and checks if the user button is pressed. If it is pressed, then it stays in booatloader mode, turns on the green (PC9) LED and waits for a new binary file. If the button isn't pressed, then it jumps to the user application.

33 |

34 |

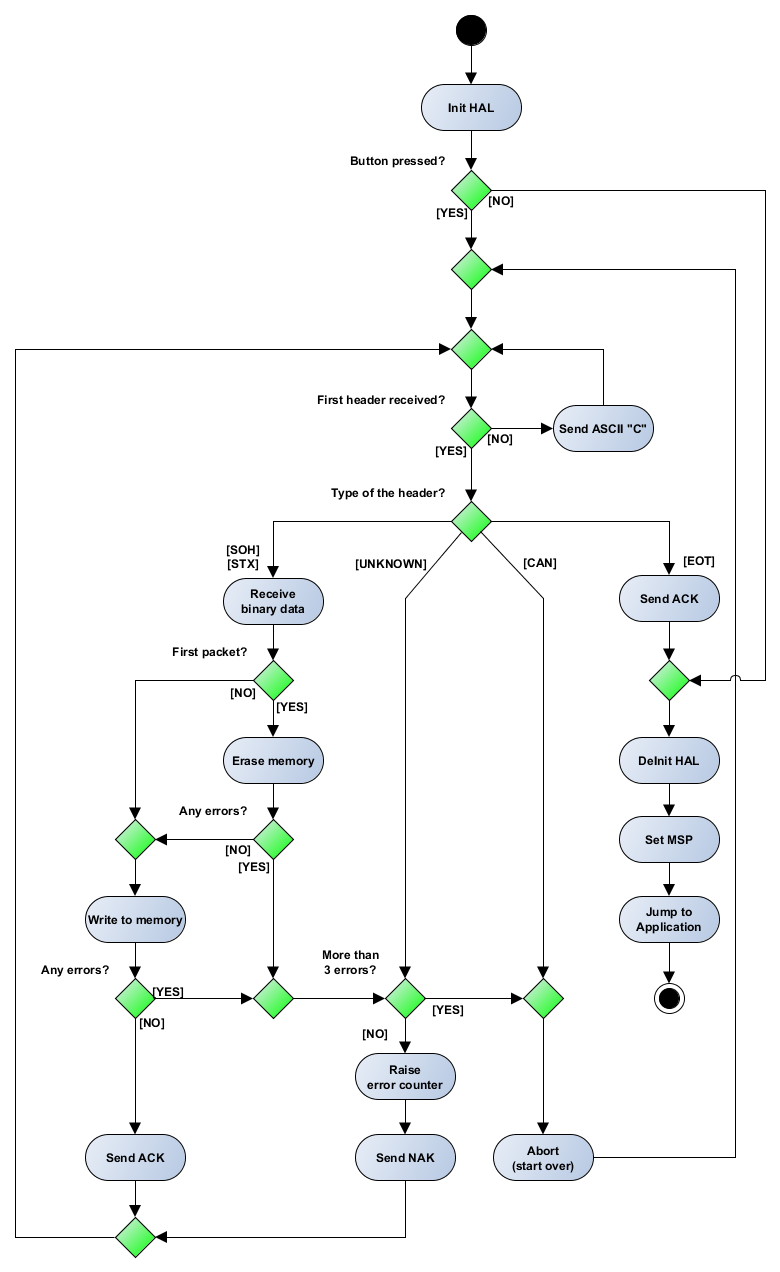

35 | *Figure 2. Brief overview of the workflow of the system.*

36 |

37 | The Xmodem protocol is clearly explained in the [references](#references).

38 |

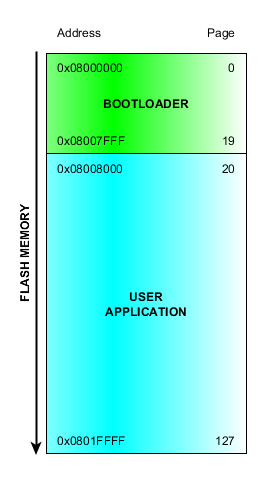

39 | #### Memory map

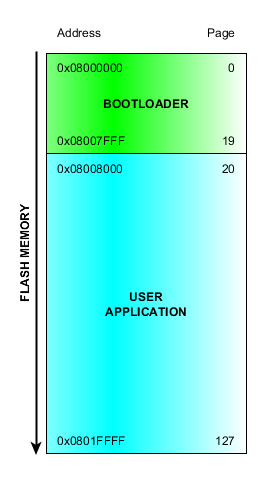

40 | The bootloader starts from 0x08000000 and the user application starts from 0x08008000.

41 |

42 |

43 | *Figure 3. The organization of the memory.*

44 |

45 | #### Code

46 | Every important code is inside the Src and Inc folders. main.c holds the button check, xmodem.c and .h hold the communication portocol, uart.c and .h are a layer between Xmodem and the generated HAL code, flash.c and .h have the writing/erasing/jumping related functions. Everything else is provided by ST.

47 | The code is fully commented, so it should be easy to understand.

48 |

49 | ### How to use it

50 | #### Embedded

51 | To use the bootloader, just get the softwares mentioned in the [Introduction](#introduction) and flash it.

52 |

53 | I included an example binary file called "blinky_test.bin" in the root folder. It blinks the blue (PC8) LED on the board.

54 | To make your own binary, you have to modify the memory location in the linker script (STM32F100RB_FLASH.ld):

55 | ```

56 | FLASH (rx) : ORIGIN = 0x8008000,

57 | ```

58 | And the vector table offset in system_stm32f1xx.c

59 | ```

60 | #define VECT_TAB_OFFSET 0x00008000U

61 | ```

62 | Last step is you have to generate a \*.bin file:

63 | ```

64 | arm-atollic-eabi-objcopy -O binary "input.elf" "output.bin"

65 | ```

66 |

67 | #### PC

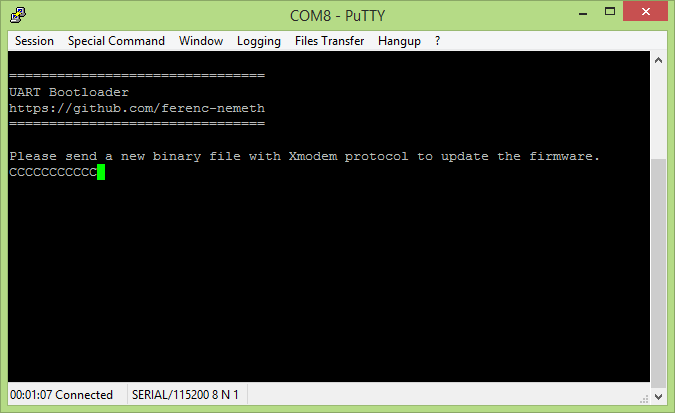

68 | To update the firmware, you need a terminal software, that supports Xmodem. I recommend PuTTY [[4]](#references) or Tera Term [[5]](#references).

69 |

70 | Configure them in the following way:

71 | - Baud rate: 115200

72 | - Data bits: 8

73 | - Parity: none

74 | - Stop bits: 1

75 |

76 | In PuTTY: select *Files Transfer* >> *Xmodem* (or *Xmodem 1K*) >> *Send* and then open the binary file.

77 |

78 |

79 | *Figure 4. PuTTY.*

80 |

81 | In Tera Term: select *File* >> *Transfer* >> *Xmodem* >> *Send* and then open the binary file.

82 |

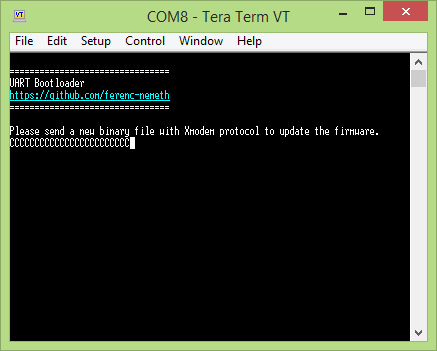

83 | *Figure 5. Tera Term.*

84 |

85 | In case everything was fine, then the output should be the same:

86 | ```

87 | ================================

88 | UART Bootloader

89 | https://github.com/ferenc-nemeth

90 | ================================

91 |

92 | Please send a new binary file with Xmodem protocol to update the firmware.

93 | CCCCCCC

94 | Firmware updated!

95 | Jumping to user application...

96 | ```

97 |

98 | #### Porting

99 | I included the *.ioc file, so the drivers can be regenerated for any ST microntroller (if it has similar memory structure).

100 | If you have a non-ST microntroller, then the xmodem protocol can be reused, but nothing else.

101 |

102 | ### References

103 | [1] [ST - Discovery kit with STM32F100RB MCU](https://www.st.com/en/evaluation-tools/stm32vldiscovery.html)

104 | [2] [Xmodem protocol with CRC](https://web.mit.edu/6.115/www/amulet/xmodem.htm)

105 | [3] [Chuck Forsberg - XMODEM/YMODEM PROTOCOL REFERENCE](http://www.blunk-electronic.de/train-z/pdf/xymodem.pdf)

106 | [4] [PuTTY](https://putty.org/)

107 | [5] [Tera Term](https://ttssh2.osdn.jp/)

108 |

109 |

--------------------------------------------------------------------------------

/STM32F100RB_FLASH.ld:

--------------------------------------------------------------------------------

1 | /*

2 | *****************************************************************************

3 | **

4 |

5 | ** File : stm32_flash.ld

6 | **

7 | ** Abstract : Linker script for STM32F100RB Device with

8 | ** 128KByte FLASH, 8KByte RAM

9 | **

10 | ** Set heap size, stack size and stack location according

11 | ** to application requirements.

12 | **

13 | ** Set memory bank area and size if external memory is used.

14 | **

15 | ** Target : STMicroelectronics STM32

16 | **

17 | ** Environment : Atollic TrueSTUDIO(R)

18 | **

19 | ** Distribution: The file is distributed as is, without any warranty

20 | ** of any kind.

21 | **

22 | ** (c)Copyright Atollic AB.

23 | ** You may use this file as-is or modify it according to the needs of your

24 | ** project. This file may only be built (assembled or compiled and linked)

25 | ** using the Atollic TrueSTUDIO(R) product. The use of this file together

26 | ** with other tools than Atollic TrueSTUDIO(R) is not permitted.

27 | **

28 | *****************************************************************************

29 | */

30 |

31 | /* Entry Point */

32 | ENTRY(Reset_Handler)

33 |

34 | /* Highest address of the user mode stack */

35 | _estack = 0x20002000; /* end of RAM */

36 | /* Generate a link error if heap and stack don't fit into RAM */

37 | _Min_Heap_Size = 0x200; /* required amount of heap */

38 | _Min_Stack_Size = 0x400; /* required amount of stack */

39 |

40 | /* Specify the memory areas */

41 | MEMORY

42 | {

43 | RAM (xrw) : ORIGIN = 0x20000000, LENGTH = 8K

44 | FLASH (rx) : ORIGIN = 0x8000000, LENGTH = 128K

45 | }

46 |

47 | /* Define output sections */

48 | SECTIONS

49 | {

50 | /* The startup code goes first into FLASH */

51 | .isr_vector :

52 | {

53 | . = ALIGN(4);

54 | KEEP(*(.isr_vector)) /* Startup code */

55 | . = ALIGN(4);

56 | } >FLASH

57 |

58 | /* The program code and other data goes into FLASH */

59 | .text :

60 | {

61 | . = ALIGN(4);

62 | *(.text) /* .text sections (code) */

63 | *(.text*) /* .text* sections (code) */

64 | *(.glue_7) /* glue arm to thumb code */

65 | *(.glue_7t) /* glue thumb to arm code */

66 | *(.eh_frame)

67 |

68 | KEEP (*(.init))

69 | KEEP (*(.fini))

70 |

71 | . = ALIGN(4);

72 | _etext = .; /* define a global symbols at end of code */

73 | } >FLASH

74 |

75 | /* Constant data goes into FLASH */

76 | .rodata :

77 | {

78 | . = ALIGN(4);

79 | *(.rodata) /* .rodata sections (constants, strings, etc.) */

80 | *(.rodata*) /* .rodata* sections (constants, strings, etc.) */

81 | . = ALIGN(4);

82 | } >FLASH

83 |

84 | .ARM.extab : { *(.ARM.extab* .gnu.linkonce.armextab.*) } >FLASH

85 | .ARM : {

86 | __exidx_start = .;

87 | *(.ARM.exidx*)

88 | __exidx_end = .;

89 | } >FLASH

90 |

91 | .preinit_array :

92 | {

93 | PROVIDE_HIDDEN (__preinit_array_start = .);

94 | KEEP (*(.preinit_array*))

95 | PROVIDE_HIDDEN (__preinit_array_end = .);

96 | } >FLASH

97 | .init_array :

98 | {

99 | PROVIDE_HIDDEN (__init_array_start = .);

100 | KEEP (*(SORT(.init_array.*)))

101 | KEEP (*(.init_array*))

102 | PROVIDE_HIDDEN (__init_array_end = .);

103 | } >FLASH

104 | .fini_array :

105 | {

106 | PROVIDE_HIDDEN (__fini_array_start = .);

107 | KEEP (*(SORT(.fini_array.*)))

108 | KEEP (*(.fini_array*))

109 | PROVIDE_HIDDEN (__fini_array_end = .);

110 | } >FLASH

111 |

112 | /* used by the startup to initialize data */

113 | _sidata = LOADADDR(.data);

114 |

115 | /* Initialized data sections goes into RAM, load LMA copy after code */

116 | .data :

117 | {

118 | . = ALIGN(4);

119 | _sdata = .; /* create a global symbol at data start */

120 | *(.data) /* .data sections */

121 | *(.data*) /* .data* sections */

122 |

123 | . = ALIGN(4);

124 | _edata = .; /* define a global symbol at data end */

125 | } >RAM AT> FLASH

126 |

127 |

128 | /* Uninitialized data section */

129 | . = ALIGN(4);

130 | .bss :

131 | {

132 | /* This is used by the startup in order to initialize the .bss secion */

133 | _sbss = .; /* define a global symbol at bss start */

134 | __bss_start__ = _sbss;

135 | *(.bss)

136 | *(.bss*)

137 | *(COMMON)

138 |

139 | . = ALIGN(4);

140 | _ebss = .; /* define a global symbol at bss end */

141 | __bss_end__ = _ebss;

142 | } >RAM

143 |

144 | /* User_heap_stack section, used to check that there is enough RAM left */

145 | ._user_heap_stack :

146 | {

147 | . = ALIGN(4);

148 | PROVIDE ( end = . );

149 | PROVIDE ( _end = . );

150 | . = . + _Min_Heap_Size;

151 | . = . + _Min_Stack_Size;

152 | . = ALIGN(4);

153 | } >RAM

154 |

155 |

156 |

157 | /* Remove information from the standard libraries */

158 | /DISCARD/ :

159 | {

160 | libc.a ( * )

161 | libm.a ( * )

162 | libgcc.a ( * )

163 | }

164 |

165 | .ARM.attributes 0 : { *(.ARM.attributes) }

166 | }

167 |

168 |

169 |

--------------------------------------------------------------------------------

/Src/stm32f1xx_hal_msp.c:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * File Name : stm32f1xx_hal_msp.c

4 | * Description : This file provides code for the MSP Initialization

5 | * and de-Initialization codes.

6 | ******************************************************************************

7 | ** This notice applies to any and all portions of this file

8 | * that are not between comment pairs USER CODE BEGIN and

9 | * USER CODE END. Other portions of this file, whether

10 | * inserted by the user or by software development tools

11 | * are owned by their respective copyright owners.

12 | *

13 | * COPYRIGHT(c) 2018 STMicroelectronics

14 | *

15 | * Redistribution and use in source and binary forms, with or without modification,

16 | * are permitted provided that the following conditions are met:

17 | * 1. Redistributions of source code must retain the above copyright notice,

18 | * this list of conditions and the following disclaimer.

19 | * 2. Redistributions in binary form must reproduce the above copyright notice,

20 | * this list of conditions and the following disclaimer in the documentation

21 | * and/or other materials provided with the distribution.

22 | * 3. Neither the name of STMicroelectronics nor the names of its contributors

23 | * may be used to endorse or promote products derived from this software

24 | * without specific prior written permission.

25 | *

26 | * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

27 | * AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE

28 | * IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE

29 | * DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE

30 | * FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL

31 | * DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR

32 | * SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER

33 | * CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY,

34 | * OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

35 | * OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

36 | *

37 | ******************************************************************************

38 | */

39 | /* Includes ------------------------------------------------------------------*/

40 | #include "stm32f1xx_hal.h"

41 |

42 | extern void _Error_Handler(char *, int);

43 | /* USER CODE BEGIN 0 */

44 |

45 | /* USER CODE END 0 */

46 | /**

47 | * Initializes the Global MSP.

48 | */

49 | void HAL_MspInit(void)

50 | {

51 | /* USER CODE BEGIN MspInit 0 */

52 |

53 | /* USER CODE END MspInit 0 */

54 |

55 | __HAL_RCC_AFIO_CLK_ENABLE();

56 | __HAL_RCC_PWR_CLK_ENABLE();

57 |

58 | HAL_NVIC_SetPriorityGrouping(NVIC_PRIORITYGROUP_4);

59 |

60 | /* System interrupt init*/

61 | /* MemoryManagement_IRQn interrupt configuration */

62 | HAL_NVIC_SetPriority(MemoryManagement_IRQn, 0, 0);

63 | /* BusFault_IRQn interrupt configuration */

64 | HAL_NVIC_SetPriority(BusFault_IRQn, 0, 0);

65 | /* UsageFault_IRQn interrupt configuration */

66 | HAL_NVIC_SetPriority(UsageFault_IRQn, 0, 0);

67 | /* SVCall_IRQn interrupt configuration */

68 | HAL_NVIC_SetPriority(SVCall_IRQn, 0, 0);

69 | /* DebugMonitor_IRQn interrupt configuration */

70 | HAL_NVIC_SetPriority(DebugMonitor_IRQn, 0, 0);

71 | /* PendSV_IRQn interrupt configuration */

72 | HAL_NVIC_SetPriority(PendSV_IRQn, 0, 0);

73 | /* SysTick_IRQn interrupt configuration */

74 | HAL_NVIC_SetPriority(SysTick_IRQn, 0, 0);

75 |

76 | /**NOJTAG: JTAG-DP Disabled and SW-DP Enabled

77 | */

78 | __HAL_AFIO_REMAP_SWJ_NOJTAG();

79 |

80 | /* USER CODE BEGIN MspInit 1 */

81 |

82 | /* USER CODE END MspInit 1 */

83 | }

84 |

85 | void HAL_UART_MspInit(UART_HandleTypeDef* huart)

86 | {

87 |

88 | GPIO_InitTypeDef GPIO_InitStruct;

89 | if(huart->Instance==USART1)

90 | {

91 | /* USER CODE BEGIN USART1_MspInit 0 */

92 |

93 | /* USER CODE END USART1_MspInit 0 */

94 | /* Peripheral clock enable */

95 | __HAL_RCC_USART1_CLK_ENABLE();

96 |

97 | /**USART1 GPIO Configuration

98 | PA9 ------> USART1_TX

99 | PA10 ------> USART1_RX

100 | */

101 | GPIO_InitStruct.Pin = GPIO_PIN_9;

102 | GPIO_InitStruct.Mode = GPIO_MODE_AF_PP;

103 | GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_HIGH;

104 | HAL_GPIO_Init(GPIOA, &GPIO_InitStruct);

105 |

106 | GPIO_InitStruct.Pin = GPIO_PIN_10;

107 | GPIO_InitStruct.Mode = GPIO_MODE_INPUT;

108 | GPIO_InitStruct.Pull = GPIO_NOPULL;

109 | HAL_GPIO_Init(GPIOA, &GPIO_InitStruct);

110 |

111 | /* USER CODE BEGIN USART1_MspInit 1 */

112 |

113 | /* USER CODE END USART1_MspInit 1 */

114 | }

115 |

116 | }

117 |

118 | void HAL_UART_MspDeInit(UART_HandleTypeDef* huart)

119 | {

120 |

121 | if(huart->Instance==USART1)

122 | {

123 | /* USER CODE BEGIN USART1_MspDeInit 0 */

124 |

125 | /* USER CODE END USART1_MspDeInit 0 */

126 | /* Peripheral clock disable */

127 | __HAL_RCC_USART1_CLK_DISABLE();

128 |

129 | /**USART1 GPIO Configuration

130 | PA9 ------> USART1_TX

131 | PA10 ------> USART1_RX

132 | */

133 | HAL_GPIO_DeInit(GPIOA, GPIO_PIN_9|GPIO_PIN_10);

134 |

135 | /* USER CODE BEGIN USART1_MspDeInit 1 */

136 |

137 | /* USER CODE END USART1_MspDeInit 1 */

138 | }

139 |

140 | }

141 |

142 | /* USER CODE BEGIN 1 */

143 |

144 | /* USER CODE END 1 */

145 |

146 | /**

147 | * @}

148 | */

149 |

150 | /**

151 | * @}

152 | */

153 |

154 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

155 |

--------------------------------------------------------------------------------

/Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_gpio_ex.c:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file stm32f1xx_hal_gpio_ex.c

4 | * @author MCD Application Team

5 | * @brief GPIO Extension HAL module driver.

6 | * This file provides firmware functions to manage the following

7 | * functionalities of the General Purpose Input/Output (GPIO) extension peripheral.

8 | * + Extended features functions

9 | *

10 | @verbatim

11 | ==============================================================================

12 | ##### GPIO Peripheral extension features #####

13 | ==============================================================================

14 | [..] GPIO module on STM32F1 family, manage also the AFIO register:

15 | (+) Possibility to use the EVENTOUT Cortex feature

16 |

17 | ##### How to use this driver #####