├── .gitignore

├── Drivers

├── LogoDxe

│ ├── Logo.bmp

│ ├── Logo.idf

│ ├── LogoDxeExtra.uni

│ ├── LogoExtra.uni

│ ├── LogoDxe.uni

│ ├── Logo.uni

│ ├── Logo.inf

│ ├── LogoDxe.inf

│ └── Logo.c

├── ConSplitterDxe

│ ├── ConSplitterDxeExtra.uni

│ ├── ConSplitterDxe.uni

│ └── ConSplitterDxe.inf

├── GraphicsConsoleDxe

│ ├── GraphicsConsoleDxeExtra.uni

│ ├── GraphicsConsoleDxe.uni

│ └── GraphicsConsoleDxe.inf

├── LedHeartbeatDxe

│ ├── LedHeartbeatDxe.inf

│ └── Heartbeat.c

├── PlatformSmbiosDxe

│ ├── PlatformSmbiosDxe.h

│ └── PlatformSmbiosDxe.inf

├── PciEmulation

│ ├── PciEmulation.inf

│ └── PciEmulation.c

├── LcdFbDxe

│ └── LcdFbDxe.inf

└── TimerDxe

│ └── TimerDxe.inf

├── Include

├── Resources

│ ├── ReleaseStampStub.h

│ ├── FbColor.h

│ ├── ReleaseInfo.h

│ └── font5x12.h

├── Device

│ ├── iMX6UsbPhy.h

│ ├── iMXIoMux.h

│ ├── iMX6ClkPwr.h

│ ├── regs-common.h

│ ├── iMXGpio.h

│ ├── MemoryMap.h

│ ├── common_epit.h

│ ├── iMX6IoMux.h

│ └── iMX6ClkPwr_ULL.h

└── Library

│ ├── iMX6Timer.h

│ └── FrameBufferSerialPortLib.h

├── AcpiTables

├── Facs.asl

├── Dsdt

│ ├── DSDT.asl

│ ├── Dsdt-I2c.asl

│ ├── Dsdt-Gpio.asl

│ ├── Dsdt-Usb.asl

│ ├── Dsdt-Platform.asl

│ ├── Dsdt-Uart.asl

│ └── Dsdt-Common.h

├── AcpiTables.inf

├── Madt.asl

├── Platform.h

├── Gtdt.aslc

├── Dbg2.aslc

└── Fadt.aslc

├── Library

├── FrameBufferSerialPortLib

│ └── FrameBufferSerialPortLib.inf

├── VirtualRealTimeClockLib

│ ├── VirtualRealTimeClockLib.inf

│ └── VirtualRealTimeClockLib.c

├── iMX6IoMuxLib

│ ├── iMX6IoMuxLib.inf

│ └── iMX6IoMux.c

├── UartSerialPortLib

│ └── UartSerialPortLib.inf

├── iMX6UsbPhyLib

│ └── iMX6UsbPhyLib.inf

├── iMX6ClkPwrLib

│ ├── iMX6ClkPwrLib.inf

│ └── iMX6ClkPwr_private.h

├── TimerLib

│ ├── TimerLib.inf

│ └── TimerLib.c

├── iMX6ULLResetSystemLib

│ ├── iMX6ULLResetSystemLib.inf

│ └── iMX6ULLResetSystemLib.c

├── PlatformLib

│ ├── PlatformLib.inf

│ ├── Arm

│ │ ├── ArmPlatformHelper.asm

│ │ └── ArmPlatformHelper.S

│ ├── ArmPlatformLib.c

│ └── ArmPlatformLibMem.c

├── PlatformBootManagerLib

│ ├── PlatformBm.h

│ └── PlatformBootManagerLib.inf

└── MemoryInitPeiLib

│ ├── MemoryInitPeiLib.inf

│ └── MemoryInitPeiLib.c

├── PrePi

├── Arm

│ ├── ArchPrePi.c

│ ├── ModuleEntryPoint.S

│ └── ModuleEntryPoint.asm

├── MainUniCore.c

├── PrePi.h

└── PeiUniCore.inf

├── README.md

├── PrimeG2Pkg.dec

├── CommonFdf.fdf.inc

└── PrimeG2.fdf

/.gitignore:

--------------------------------------------------------------------------------

1 | .DS_Store

2 | InternalPayload

--------------------------------------------------------------------------------

/Drivers/LogoDxe/Logo.bmp:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/imbushuo/PrimeG2Pkg/HEAD/Drivers/LogoDxe/Logo.bmp

--------------------------------------------------------------------------------

/Include/Resources/ReleaseStampStub.h:

--------------------------------------------------------------------------------

1 | #ifndef __RELEASE_STAMP_STUB_H__

2 | #define __RELEASE_STAMP_STUB_H__

3 |

4 | // These values will be overwritten by build script.

5 | #define __IMPL_COMMIT_ID__ "Unknown Commit"

6 | #define __RELEASE_DATE__ "06/10/2018"

7 | #define __BUILD_OWNER__ "Unknown@Unknown"

8 | #define __EDK2_RELEASE__ "Unknown Commit"

9 |

10 | #endif

11 |

--------------------------------------------------------------------------------

/Include/Resources/FbColor.h:

--------------------------------------------------------------------------------

1 | #ifndef _FB_COLOR_H_

2 | #define _FB_COLOR_H_

3 |

4 | #define FB_BGRA8888_BLACK 0xff000000

5 | #define FB_BGRA8888_WHITE 0xffffffff

6 | #define FB_BGRA8888_CYAN 0xff00ffff

7 | #define FB_BGRA8888_BLUE 0xff0000ff

8 | #define FB_BGRA8888_SILVER 0xffc0c0c0

9 | #define FB_BGRA8888_YELLOW 0xffffff00

10 | #define FB_BGRA8888_ORANGE 0xffffa500

11 | #define FB_BGRA8888_RED 0xffff0000

12 | #define FB_BGRA8888_GREEN 0xff00ff00

13 |

14 | #endif

--------------------------------------------------------------------------------

/Include/Resources/ReleaseInfo.h:

--------------------------------------------------------------------------------

1 | #ifndef __SMBIOS_RELEASE_INFO_H__

2 | #define __SMBIOS_RELEASE_INFO_H__

3 | #ifdef __IMPL_COMMIT_ID__

4 | #undef __IMPL_COMMIT_ID__

5 | #endif

6 | #define __IMPL_COMMIT_ID__ "b874b97e"

7 | #ifdef __RELEASE_DATE__

8 | #undef __RELEASE_DATE__

9 | #endif

10 | #define __RELEASE_DATE__ "09/06/2019"

11 | #ifdef __BUILD_OWNER__

12 | #undef __BUILD_OWNER__

13 | #endif

14 | #define __BUILD_OWNER__ "binwang@bc-macbookpro-osx"

15 | #ifdef __EDK2_RELEASE__

16 | #undef __EDK2_RELEASE__

17 | #endif

18 | #define __EDK2_RELEASE__ "4e0f920d"

19 | #endif

20 |

--------------------------------------------------------------------------------

/Drivers/LogoDxe/Logo.idf:

--------------------------------------------------------------------------------

1 | // /** @file

2 | // Platform Logo image definition file.

3 | //

4 | // Copyright (c) 2016 - 2018, Intel Corporation. All rights reserved.

5 | //

6 | // This program and the accompanying materials

7 | // are licensed and made available under the terms and conditions of the BSD License

8 | // which accompanies this distribution. The full text of the license may be found at

9 | // http://opensource.org/licenses/bsd-license.php

10 | // THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | // WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | //

13 | // **/

14 |

15 | #image IMG_LOGO Logo.bmp

16 |

--------------------------------------------------------------------------------

/Include/Device/iMX6UsbPhy.h:

--------------------------------------------------------------------------------

1 | /** @file

2 | *

3 | * Copyright (c) 2018 Microsoft Corporation. All rights reserved.

4 | *

5 | * This program and the accompanying materials

6 | * are licensed and made available under the terms and conditions of the BSD License

7 | * which accompanies this distribution. The full text of the license may be found at

8 | * http://opensource.org/licenses/bsd-license.php

9 | *

10 | * THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | * WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | *

13 | **/

14 |

15 | #ifndef _IMX6_USB_PHY_H_

16 | #define _IMX6_USB_PHY_H_

17 |

18 | EFI_STATUS ImxUsbPhyInit (IMX_USBPHY_ID ImxUsbPhyId);

19 |

20 | #endif // _IMX6_USB_PHY_H_

21 |

--------------------------------------------------------------------------------

/Drivers/LogoDxe/LogoDxeExtra.uni:

--------------------------------------------------------------------------------

1 | // /** @file

2 | // Logo Localized Strings and Content

3 | //

4 | // Copyright (c) 2016, Intel Corporation. All rights reserved.

5 | //

6 | // This program and the accompanying materials

7 | // are licensed and made available under the terms and conditions of the BSD License

8 | // which accompanies this distribution. The full text of the license may be found at

9 | // http://opensource.org/licenses/bsd-license.php

10 | // THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | // WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | //

13 | // **/

14 |

15 | #string STR_PROPERTIES_MODULE_NAME

16 | #language en-US

17 | "Logo Image File"

18 |

19 |

20 |

--------------------------------------------------------------------------------

/Drivers/LogoDxe/LogoExtra.uni:

--------------------------------------------------------------------------------

1 | // /** @file

2 | // Logo Localized Strings and Content

3 | //

4 | // Copyright (c) 2013 - 2014, Intel Corporation. All rights reserved.

5 | //

6 | // This program and the accompanying materials

7 | // are licensed and made available under the terms and conditions of the BSD License

8 | // which accompanies this distribution. The full text of the license may be found at

9 | // http://opensource.org/licenses/bsd-license.php

10 | // THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | // WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | //

13 | // **/

14 |

15 | #string STR_PROPERTIES_MODULE_NAME

16 | #language en-US

17 | "Logo Image File"

18 |

19 |

20 |

--------------------------------------------------------------------------------

/Include/Library/iMX6Timer.h:

--------------------------------------------------------------------------------

1 | /** @file

2 | *

3 | * Copyright (c) 2018 Microsoft Corporation. All rights reserved.

4 | *

5 | * This program and the accompanying materials

6 | * are licensed and made available under the terms and conditions of the BSD License

7 | * which accompanies this distribution. The full text of the license may be found at

8 | * http://opensource.org/licenses/bsd-license.php

9 | *

10 | * THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | * WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | *

13 | **/

14 |

15 | #ifndef _IMX6_TIMER_H_

16 | #define _IMX6_TIMER_H_

17 |

18 | RETURN_STATUS

19 | EFIAPI

20 | TimerConstructor (

21 | VOID

22 | );

23 |

24 | #endif /* _IMX6_TIMER_H_ */

25 |

--------------------------------------------------------------------------------

/AcpiTables/Facs.asl:

--------------------------------------------------------------------------------

1 | [000h 0000 4] Signature : "FACS"

2 | [004h 0004 4] Length : 00000040

3 | [008h 0008 4] Hardware Signature : 00000000

4 | [00Ch 0012 4] 32 Firmware Waking Vector : 00000000

5 | [010h 0016 4] Global Lock : 00000000

6 | [014h 0020 4] Flags (decoded below) : 00000000

7 | S4BIOS Support Present : 0

8 | 64-bit Wake Supported (V2) : 0

9 | [018h 0024 8] 64 Firmware Waking Vector : 0000000000000000

10 | [020h 0032 1] Version : 02

11 | [021h 0033 3] Reserved : 000000

12 | [024h 0036 4] OspmFlags (decoded below) : 00000000

13 | 64-bit Wake Env Required (V2) : 0

14 |

--------------------------------------------------------------------------------

/Drivers/ConSplitterDxe/ConSplitterDxeExtra.uni:

--------------------------------------------------------------------------------

1 | // /** @file

2 | // ConSplitterDxe Localized Strings and Content

3 | //

4 | // Copyright (c) 2013 - 2014, Intel Corporation. All rights reserved.

5 | //

6 | // This program and the accompanying materials

7 | // are licensed and made available under the terms and conditions of the BSD License

8 | // which accompanies this distribution. The full text of the license may be found at

9 | // http://opensource.org/licenses/bsd-license.php

10 | // THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | // WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | //

13 | // **/

14 |

15 | #string STR_PROPERTIES_MODULE_NAME

16 | #language en-US

17 | "Console Splitter DXE Driver"

18 |

19 |

20 |

--------------------------------------------------------------------------------

/Drivers/GraphicsConsoleDxe/GraphicsConsoleDxeExtra.uni:

--------------------------------------------------------------------------------

1 | // /** @file

2 | // GraphicsConsoleDxe Localized Strings and Content

3 | //

4 | // Copyright (c) 2013 - 2014, Intel Corporation. All rights reserved.

5 | //

6 | // This program and the accompanying materials

7 | // are licensed and made available under the terms and conditions of the BSD License

8 | // which accompanies this distribution. The full text of the license may be found at

9 | // http://opensource.org/licenses/bsd-license.php

10 | // THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | // WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | //

13 | // **/

14 |

15 | #string STR_PROPERTIES_MODULE_NAME

16 | #language en-US

17 | "Graphics Console DXE Driver"

18 |

19 |

20 |

--------------------------------------------------------------------------------

/Library/FrameBufferSerialPortLib/FrameBufferSerialPortLib.inf:

--------------------------------------------------------------------------------

1 | [Defines]

2 | INF_VERSION = 0x00010005

3 | BASE_NAME = FrameBufferSerialPortLib

4 | MODULE_TYPE = BASE

5 | VERSION_STRING = 1.0

6 | LIBRARY_CLASS = SerialPortLib

7 |

8 | [Sources.common]

9 | FrameBufferSerialPortLib.c

10 |

11 | [Packages]

12 | MdePkg/MdePkg.dec

13 | ArmPkg/ArmPkg.dec

14 | PrimeG2Pkg/PrimeG2Pkg.dec

15 |

16 | [LibraryClasses]

17 | ArmLib

18 | PcdLib

19 | IoLib

20 | HobLib

21 | CompilerIntrinsicsLib

22 | CacheMaintenanceLib

23 | BaseMemoryLib

24 |

25 | [Pcd]

26 | gPrimeG2PkgTokenSpaceGuid.PcdLcdIfBaseAddress

27 | gPrimeG2PkgTokenSpaceGuid.PcdFrameBufferWidth

28 | gPrimeG2PkgTokenSpaceGuid.PcdFrameBufferHeight

29 | gPrimeG2PkgTokenSpaceGuid.PcdEnableScreenSerial

--------------------------------------------------------------------------------

/PrePi/Arm/ArchPrePi.c:

--------------------------------------------------------------------------------

1 | /** @file

2 | *

3 | * Copyright (c) 2011 - 2013, ARM Limited. All rights reserved.

4 | *

5 | * This program and the accompanying materials

6 | * are licensed and made available under the terms and conditions of the BSD License

7 | * which accompanies this distribution. The full text of the license may be found at

8 | * http://opensource.org/licenses/bsd-license.php

9 | *

10 | * THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | * WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | *

13 | **/

14 |

15 | #include "PrePi.h"

16 |

17 | VOID

18 | ArchInitialize (

19 | VOID

20 | )

21 | {

22 | // Enable program flow prediction, if supported.

23 | ArmEnableBranchPrediction ();

24 |

25 | if (FixedPcdGet32 (PcdVFPEnabled)) {

26 | ArmEnableVFP ();

27 | }

28 | }

29 |

30 |

--------------------------------------------------------------------------------

/AcpiTables/Dsdt/DSDT.asl:

--------------------------------------------------------------------------------

1 | /*

2 | * iMX6 ULL DSDT

3 | *

4 | * Copyright (c) 2018 Microsoft Corporation. All rights reserved.

5 | *

6 | * This program and the accompanying materials

7 | * are licensed and made available under the terms and conditions of the BSD License

8 | * which accompanies this distribution. The full text of the license may be found at

9 | * http://opensource.org/licenses/bsd-license.php

10 | *

11 | * THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

12 | * WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

13 | *

14 | */

15 | #include "Dsdt-Common.h"

16 |

17 | DefinitionBlock ("DSDT.aml", "DSDT", 5, "MSFT", "EDK2", 1)

18 | {

19 | Scope (\_SB_)

20 | {

21 | include("Dsdt-Platform.asl")

22 | include("Dsdt-Gpio.asl")

23 | include("Dsdt-I2c.asl")

24 | include("Dsdt-Uart.asl")

25 | include("Dsdt-Usb.asl")

26 | } // \_SB_

27 | }

28 |

--------------------------------------------------------------------------------

/AcpiTables/Dsdt/Dsdt-I2c.asl:

--------------------------------------------------------------------------------

1 | /** @file

2 | *

3 | * Copyright (c) 2018 Microsoft Corporation. All rights reserved.

4 | *

5 | * This program and the accompanying materials

6 | * are licensed and made available under the terms and conditions of the BSD License

7 | * which accompanies this distribution. The full text of the license may be found at

8 | * http://opensource.org/licenses/bsd-license.php

9 | *

10 | * THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | * WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | *

13 | **/

14 |

15 | Device (I2C1)

16 | {

17 | Name (_HID, "NXP0104")

18 | Name (_UID, 0x1)

19 |

20 | Method (_STA) {

21 | Return (0xf)

22 | }

23 |

24 | Name (_CRS, ResourceTemplate () {

25 | MEMORY32FIXED (ReadWrite, 0x021A0000, 0x14, )

26 | Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) { 68 }

27 | })

28 | }

29 |

30 |

--------------------------------------------------------------------------------

/Include/Device/iMXIoMux.h:

--------------------------------------------------------------------------------

1 | /** @file

2 | *

3 | * Copyright (c) 2018 Microsoft Corporation. All rights reserved.

4 | *

5 | * This program and the accompanying materials

6 | * are licensed and made available under the terms and conditions of the BSD License

7 | * which accompanies this distribution. The full text of the license may be found at

8 | * http://opensource.org/licenses/bsd-license.php

9 | *

10 | * THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | * WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | *

13 | **/

14 |

15 | #ifndef _IMX_IO_MUX_H_

16 | #define _IMX_IO_MUX_H_

17 |

18 | #define IMX_IOMUX_PAD_DEFINE(CtlRegOffset, MuxRegOffset) \

19 | ((((CtlRegOffset) & 0xffff) << 16) | ((MuxRegOffset) & 0xffff))

20 |

21 | #define IMX_IOMUX_PAD_CTL_OFFSET(ImxPadVal) ((ImxPadVal) >> 16)

22 | #define IMX_IOMUX_PAD_MUX_OFFSET(ImxPadVal) ((ImxPadVal) & 0xffff)

23 |

24 | #endif // _IMX_IO_MUX_H_

25 |

--------------------------------------------------------------------------------

/Include/Library/FrameBufferSerialPortLib.h:

--------------------------------------------------------------------------------

1 | #ifndef _FRAMEBUFFER_SERIALPORT_LIB_H_

2 | #define _FRAMEBUFFER_SERIALPORT_LIB_H_

3 |

4 | #include

5 |

6 | typedef struct _FBCON_POSITION {

7 | INTN x;

8 | INTN y;

9 | } FBCON_POSITION, *PFBCON_POSITION;

10 |

11 | typedef struct _FBCON_COLOR {

12 | UINTN Foreground;

13 | UINTN Background;

14 | } FBCON_COLOR, *PFBCON_COLOR;

15 |

16 | enum FbConMsgType {

17 | /* type for menu */

18 | FBCON_COMMON_MSG = 0,

19 | FBCON_UNLOCK_TITLE_MSG,

20 | FBCON_TITLE_MSG,

21 | FBCON_SUBTITLE_MSG,

22 |

23 | /* type for warning */

24 | FBCON_YELLOW_MSG,

25 | FBCON_ORANGE_MSG,

26 | FBCON_RED_MSG,

27 | FBCON_GREEN_MSG,

28 |

29 | /* and the select message's background */

30 | FBCON_SELECT_MSG_BG_COLOR,

31 | };

32 |

33 | void ResetFb(void);

34 |

35 | UINTN

36 | EFIAPI

37 | SerialPortWriteCritical(IN UINT8 *Buffer, IN UINTN NumberOfBytes);

38 |

39 | #endif

40 |

--------------------------------------------------------------------------------

/README.md:

--------------------------------------------------------------------------------

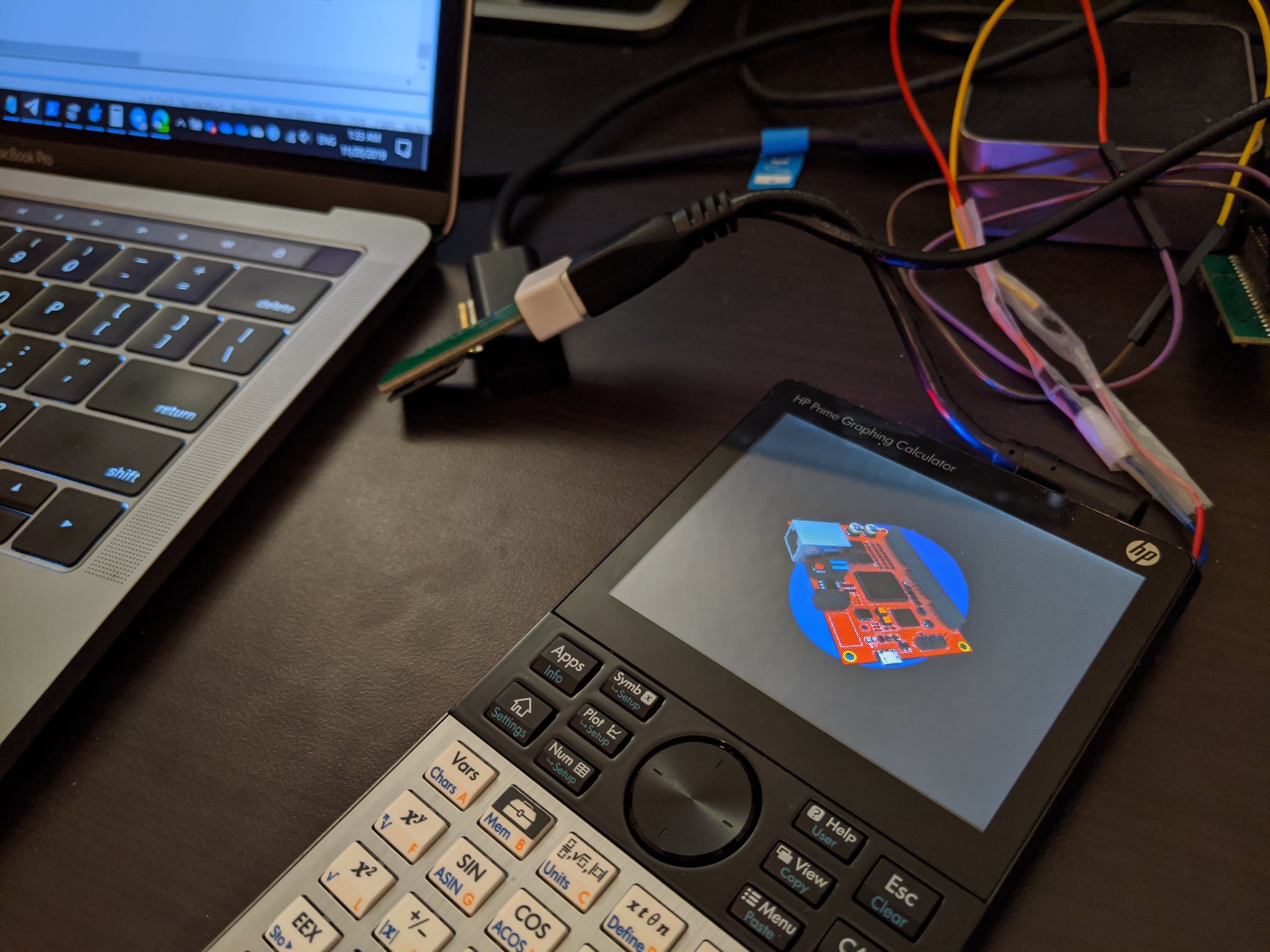

1 | # PrimeG2Pkg: UEFI for HP Prime G2 calculator

2 |

3 | I will write a better README later.

4 |

5 |

6 |

7 |

8 |

9 | ## Current Status

10 |

11 | Capable of booting Windows and Linux. USB Host is functional but external VBus supply is required currently.

12 |

13 | ## Boot

14 |

15 | You need a few tools from [prinux](https://github.com/zephray/prinux) and my [U-Boot](https://github.com/imbushuo/uboot).

16 |

17 | ## License

18 |

19 | GPLv2

20 |

--------------------------------------------------------------------------------

/Drivers/LedHeartbeatDxe/LedHeartbeatDxe.inf:

--------------------------------------------------------------------------------

1 | [Defines]

2 | INF_VERSION = 0x00010005

3 | BASE_NAME = LedHeartbeatDxe

4 | FILE_GUID = 78fe9d61-2f48-4ff3-aec0-3a9fd0e10333

5 | MODULE_TYPE = DXE_DRIVER

6 | VERSION_STRING = 1.0

7 | ENTRY_POINT = HeartbeatInitialize

8 |

9 | [Sources.common]

10 | Heartbeat.c

11 |

12 | [Packages]

13 | MdePkg/MdePkg.dec

14 | ArmPkg/ArmPkg.dec

15 | EmbeddedPkg/EmbeddedPkg.dec

16 | PrimeG2Pkg/PrimeG2Pkg.dec

17 |

18 | [BuildOptions.AARCH64]

19 | GCC:*_*_*_CC_FLAGS = -Werror -Wno-error=unused-variable

20 |

21 | [LibraryClasses]

22 | UefiDriverEntryPoint

23 | IoLib

24 | TimerLib

25 | BaseLib

26 | DebugLib

27 | PrintLib

28 | iMX6IoMuxLib

29 |

30 | [Protocols]

31 | gEfiTimerArchProtocolGuid

32 |

33 | [Guids]

34 | gEfiEventExitBootServicesGuid

35 |

36 | [Pcd]

37 | giMXPlatformTokenSpaceGuid.PcdGpioBankMemoryRange

38 |

39 | [Depex]

40 | gEfiTimerArchProtocolGuid

--------------------------------------------------------------------------------

/Drivers/LogoDxe/LogoDxe.uni:

--------------------------------------------------------------------------------

1 | // /** @file

2 | // The default logo bitmap picture shown on setup screen.

3 | //

4 | // This module provides the default logo bitmap picture shown on setup screen, through EDKII Platform Logo protocol.

5 | //

6 | // Copyright (c) 2016, Intel Corporation. All rights reserved.

7 | //

8 | // This program and the accompanying materials

9 | // are licensed and made available under the terms and conditions of the BSD License

10 | // which accompanies this distribution. The full text of the license may be found at

11 | // http://opensource.org/licenses/bsd-license.php

12 | // THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

13 | // WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

14 | //

15 | // **/

16 |

17 |

18 | #string STR_MODULE_ABSTRACT #language en-US "Provides the default logo bitmap picture shown on setup screen."

19 |

20 | #string STR_MODULE_DESCRIPTION #language en-US "This module provides the default logo bitmap picture shown on setup screen, through EDKII Platform Logo protocol."

21 |

22 |

--------------------------------------------------------------------------------

/PrePi/MainUniCore.c:

--------------------------------------------------------------------------------

1 | /** @file

2 | *

3 | * Copyright (c) 2011, ARM Limited. All rights reserved.

4 | *

5 | * This program and the accompanying materials

6 | * are licensed and made available under the terms and conditions of the BSD License

7 | * which accompanies this distribution. The full text of the license may be found at

8 | * http://opensource.org/licenses/bsd-license.php

9 | *

10 | * THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | * WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | *

13 | **/

14 |

15 | #include "PrePi.h"

16 |

17 | VOID

18 | PrimaryMain (

19 | IN UINTN UefiMemoryBase,

20 | IN UINTN StacksBase,

21 | IN UINT64 StartTimeStamp

22 | )

23 | {

24 | PrePiMain (UefiMemoryBase, StacksBase, StartTimeStamp);

25 |

26 | // We must never return

27 | ASSERT(FALSE);

28 | }

29 |

30 | VOID

31 | SecondaryMain (

32 | IN UINTN MpId

33 | )

34 | {

35 | // We must never get into this function on UniCore system

36 | ASSERT(FALSE);

37 | }

38 |

39 |

--------------------------------------------------------------------------------

/Drivers/GraphicsConsoleDxe/GraphicsConsoleDxe.uni:

--------------------------------------------------------------------------------

1 | // /** @file

2 | // Console support on graphic devices.

3 | //

4 | // This driver will install Simple Text Output protocol by consuming Graphices Output

5 | // protocol or UGA Draw protocol on graphic devices.

6 | //

7 | // Copyright (c) 2006 - 2014, Intel Corporation. All rights reserved.

8 | //

9 | // This program and the accompanying materials

10 | // are licensed and made available under the terms and conditions of the BSD License

11 | // which accompanies this distribution. The full text of the license may be found at

12 | // http://opensource.org/licenses/bsd-license.php

13 | // THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

14 | // WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

15 | //

16 | // **/

17 |

18 |

19 | #string STR_MODULE_ABSTRACT #language en-US "Console support on graphic devices"

20 |

21 | #string STR_MODULE_DESCRIPTION #language en-US "This driver will install SimpleTextOutputProtocol by consuming GraphicesOutput\n"

22 | "Protocol or UgaDrawProtocol on graphics devices."

23 |

24 |

--------------------------------------------------------------------------------

/Drivers/LogoDxe/Logo.uni:

--------------------------------------------------------------------------------

1 | // /** @file

2 | // The default logo bitmap picture shown on setup screen, which is corresponding to gEfiDefaultBmpLogoGuid.

3 | //

4 | // This module provides the default logo bitmap picture shown on setup screen, which corresponds to gEfiDefaultBmpLogoGuid.

5 | //

6 | // Copyright (c) 2006 - 2014, Intel Corporation. All rights reserved.

7 | //

8 | // This program and the accompanying materials

9 | // are licensed and made available under the terms and conditions of the BSD License

10 | // which accompanies this distribution. The full text of the license may be found at

11 | // http://opensource.org/licenses/bsd-license.php

12 | // THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

13 | // WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

14 | //

15 | // **/

16 |

17 |

18 | #string STR_MODULE_ABSTRACT #language en-US "Provides the default logo bitmap picture shown on setup screen, which corresponds to gEfiDefaultBmpLogoGuid"

19 |

20 | #string STR_MODULE_DESCRIPTION #language en-US "This module provides the default logo bitmap picture shown on setup screen, which corresponds to gEfiDefaultBmpLogoGuid."

21 |

22 |

--------------------------------------------------------------------------------

/Library/VirtualRealTimeClockLib/VirtualRealTimeClockLib.inf:

--------------------------------------------------------------------------------

1 | ## @file

2 | #

3 | # Copyright (c) 2018 Microsoft Corporation. All rights reserved.

4 | #

5 | # This program and the accompanying materials

6 | # are licensed and made available under the terms and conditions of the BSD License

7 | # which accompanies this distribution. The full text of the license may be found at

8 | # http://opensource.org/licenses/bsd-license.php

9 | #

10 | # THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | # WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | #

13 | ##

14 |

15 | [Defines]

16 | INF_VERSION = 0x0001001A

17 | BASE_NAME = VirtualRealTimeClockLib

18 | FILE_GUID = 1E27D461-78F3-4F7D-B1C2-F72384F13A6E

19 | MODULE_TYPE = BASE

20 | VERSION_STRING = 1.0

21 | LIBRARY_CLASS = RealTimeClockLib

22 |

23 | [Sources.common]

24 | VirtualRealTimeClockLib.c

25 |

26 | [Packages]

27 | ArmPkg/ArmPkg.dec

28 | EmbeddedPkg/EmbeddedPkg.dec

29 | MdePkg/MdePkg.dec

30 |

31 | [LibraryClasses]

32 | DebugLib

33 | IoLib

34 | TimerLib

35 |

36 | [FixedPcd]

37 | gArmTokenSpaceGuid.PcdArmArchTimerFreqInHz

--------------------------------------------------------------------------------

/Library/iMX6IoMuxLib/iMX6IoMuxLib.inf:

--------------------------------------------------------------------------------

1 | ## @file

2 | #

3 | # Copyright (c) 2018 Microsoft Corporation. All rights reserved.

4 | #

5 | # This program and the accompanying materials

6 | # are licensed and made available under the terms and conditions of the BSD License

7 | # which accompanies this distribution. The full text of the license may be found at

8 | # http://opensource.org/licenses/bsd-license.php

9 | #

10 | # THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | # WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | #

13 | ##

14 |

15 | [Defines]

16 | INF_VERSION = 0x0001001A

17 | BASE_NAME = iMX6IoMuxLib

18 | FILE_GUID = FA41BEF0-0666-4C07-9EC3-47F61C36EDBE

19 | MODULE_TYPE = BASE

20 | VERSION_STRING = 1.0

21 | LIBRARY_CLASS = iMX6IoMuxLib

22 |

23 | [Packages]

24 | ArmPkg/ArmPkg.dec

25 | EmbeddedPkg/EmbeddedPkg.dec

26 | MdeModulePkg/MdeModulePkg.dec

27 | MdePkg/MdePkg.dec

28 | PrimeG2Pkg/PrimeG2Pkg.dec

29 |

30 | [LibraryClasses]

31 | BaseMemoryLib

32 | DebugLib

33 | IoLib

34 | TimerLib

35 |

36 | [Sources.common]

37 | iMX6IoMux.c

38 |

39 | [FixedPcd]

40 | giMXPlatformTokenSpaceGuid.PcdGpioBankMemoryRange

--------------------------------------------------------------------------------

/Library/UartSerialPortLib/UartSerialPortLib.inf:

--------------------------------------------------------------------------------

1 | ## @file

2 | #

3 | # Copyright (c) 2018 Microsoft Corporation. All rights reserved.

4 | #

5 | # This program and the accompanying materials

6 | # are licensed and made available under the terms and conditions of the BSD License

7 | # which accompanies this distribution. The full text of the license may be found at

8 | # http://opensource.org/licenses/bsd-license.php

9 | #

10 | # THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | # WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | #

13 | ##

14 |

15 | [Defines]

16 | INF_VERSION = 0x0001001A

17 | BASE_NAME = SerialPortLib

18 | FILE_GUID = C22D85E6-8B3E-4c05-AA5B-5732F3ACD055

19 | MODULE_TYPE = BASE

20 | VERSION_STRING = 1.0

21 | LIBRARY_CLASS = SerialPortLib

22 |

23 | [Sources.common]

24 | UartSerialPortLib.c

25 |

26 | [LibraryClasses]

27 | ArmLib

28 | BaseMemoryLib

29 | CacheMaintenanceLib

30 | IoLib

31 | PcdLib

32 | TimerLib

33 |

34 | [Packages]

35 | ArmPkg/ArmPkg.dec

36 | ArmPlatformPkg/ArmPlatformPkg.dec

37 | MdePkg/MdePkg.dec

38 | PrimeG2Pkg/PrimeG2Pkg.dec

39 |

40 | [FixedPcd]

41 | giMXPlatformTokenSpaceGuid.PcdSerialRegisterBase

42 |

--------------------------------------------------------------------------------

/Drivers/LogoDxe/Logo.inf:

--------------------------------------------------------------------------------

1 | ## @file

2 | # The default logo bitmap picture shown on setup screen, which is corresponding to gEfiDefaultBmpLogoGuid.

3 | #

4 | # Copyright (c) 2006 - 2014, Intel Corporation. All rights reserved.

5 | #

6 | # This program and the accompanying materials

7 | # are licensed and made available under the terms and conditions of the BSD License

8 | # which accompanies this distribution. The full text of the license may be found at

9 | # http://opensource.org/licenses/bsd-license.php

10 | # THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | # WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | #

13 | #

14 | ##

15 |

16 | [Defines]

17 | INF_VERSION = 0x00010005

18 | BASE_NAME = Logo

19 | MODULE_UNI_FILE = Logo.uni

20 | FILE_GUID = 7BB28B99-61BB-11D5-9A5D-0090273FC14D

21 | MODULE_TYPE = USER_DEFINED

22 | VERSION_STRING = 1.0

23 |

24 | #

25 | # The following information is for reference only and not required by the build tools.

26 | #

27 | # VALID_ARCHITECTURES = IA32 X64 IPF EBC ARM AARCH64

28 | #

29 |

30 | [Binaries]

31 | BIN|Logo.bmp|*

32 |

33 | [UserExtensions.TianoCore."ExtraFiles"]

34 | LogoExtra.uni

35 |

--------------------------------------------------------------------------------

/Library/iMX6UsbPhyLib/iMX6UsbPhyLib.inf:

--------------------------------------------------------------------------------

1 | ## @file

2 | #

3 | # Copyright (c) 2018 Microsoft Corporation. All rights reserved.

4 | #

5 | # This program and the accompanying materials

6 | # are licensed and made available under the terms and conditions of the BSD License

7 | # which accompanies this distribution. The full text of the license may be found at

8 | # http://opensource.org/licenses/bsd-license.php

9 | #

10 | # THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | # WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | #

13 | ##

14 |

15 | [Defines]

16 | INF_VERSION = 0x00010005

17 | BASE_NAME = iMX6UsbPhyLib

18 | FILE_GUID = 463989D1-27DC-4AE7-92AE-C7E28C1C605D

19 | MODULE_TYPE = BASE

20 | VERSION_STRING = 1.0

21 | LIBRARY_CLASS = iMX6UsbPhyLib

22 |

23 | [Packages]

24 | MdePkg/MdePkg.dec

25 | MdeModulePkg/MdeModulePkg.dec

26 | EmbeddedPkg/EmbeddedPkg.dec

27 | ArmPkg/ArmPkg.dec

28 | ArmPlatformPkg/ArmPlatformPkg.dec

29 | PrimeG2Pkg/PrimeG2Pkg.dec

30 |

31 | [LibraryClasses]

32 | BaseMemoryLib

33 | DebugLib

34 | IoLib

35 | TimerLib

36 | iMX6IoMuxLib

37 |

38 | [Sources.common]

39 | iMX6UsbPhy.c

40 |

41 | [FixedPcd]

42 | giMXPlatformTokenSpaceGuid.PcdGpioBankMemoryRange

43 |

--------------------------------------------------------------------------------

/Drivers/PlatformSmbiosDxe/PlatformSmbiosDxe.h:

--------------------------------------------------------------------------------

1 | /** @file

2 | *

3 | * Copyright (c) 2015, ARM Limited. All rights reserved.

4 | * Copyright (c) 2018 Microsoft Corporation. All rights reserved.

5 | *

6 | * This program and the accompanying materials

7 | * are licensed and made available under the terms and conditions of the BSD License

8 | * which accompanies this distribution. The full text of the license may be found at

9 | * http://opensource.org/licenses/bsd-license.php

10 | *

11 | * THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

12 | * WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

13 | *

14 | **/

15 |

16 | #ifndef _PLATFORM_SMBIOS_DXE_H_

17 | #define _PLATFORM_SMBIOS_DXE_H_

18 |

19 | #define OCOTP_BANK_0_WORD_1 0x021BC410

20 | #define OCOTP_BANK_0_WORD_2 0x021BC420

21 |

22 | #define GLOBAL_PAGE_SIGNATURE 0x474C424C // 'GLBL'

23 |

24 | enum SMBIOS_REFRENCE_HANDLES {

25 | SMBIOS_HANDLE_BOARD = 0x1000,

26 | SMBIOS_HANDLE_CHASSIS,

27 | SMBIOS_HANDLE_PROCESSOR,

28 | SMBIOS_HANDLE_L1I,

29 | SMBIOS_HANDLE_L1D,

30 | SMBIOS_HANDLE_L2U,

31 | SMBIOS_HANDLE_MEMORY_ARRAY,

32 | SMBIOS_HANDLE_MEMORY_DEVICE

33 | };

34 |

35 | typedef struct {

36 | UINT32 Signature;

37 | UINT8 Revision;

38 | UINT8 reserved[3];

39 | UINT8 Mac0Id;

40 | UINT8 Mac0Valid;

41 | UINT8 MacAddress[6];

42 | } GLOBAL_PAGE_DATA;

43 |

44 | #endif /* _PLATFORM_SMBIOS_DXE_H_ */

45 |

--------------------------------------------------------------------------------

/Library/iMX6ClkPwrLib/iMX6ClkPwrLib.inf:

--------------------------------------------------------------------------------

1 | ## @file

2 | #

3 | # Copyright (c) 2018 Microsoft Corporation. All rights reserved.

4 | #

5 | # This program and the accompanying materials

6 | # are licensed and made available under the terms and conditions of the BSD License

7 | # which accompanies this distribution. The full text of the license may be found at

8 | # http://opensource.org/licenses/bsd-license.php

9 | #

10 | # THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | # WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | #

13 | ##

14 |

15 | [Defines]

16 | INF_VERSION = 0x0001001A

17 | BASE_NAME = iMX6ClkPwrLib

18 | FILE_GUID = 8DB4B460-9201-435A-B86A-24B58CED9A9E

19 | MODULE_TYPE = BASE

20 | VERSION_STRING = 1.0

21 | LIBRARY_CLASS = iMX6ClkPwrLib

22 |

23 | [Packages]

24 | ArmPkg/ArmPkg.dec

25 | ArmPlatformPkg/ArmPlatformPkg.dec

26 | EmbeddedPkg/EmbeddedPkg.dec

27 | MdeModulePkg/MdeModulePkg.dec

28 | MdePkg/MdePkg.dec

29 | PrimeG2Pkg/PrimeG2Pkg.dec

30 |

31 | [LibraryClasses]

32 | BaseMemoryLib

33 | DebugLib

34 | iMX6IoMuxLib

35 | IoLib

36 | TimerLib

37 |

38 | [Sources.common]

39 | iMX6ClkPwr.c

40 |

41 | [FeaturePcd]

42 | gPrimeG2PkgTokenSpaceGuid.PcdLvdsEnable

43 |

44 | [FixedPcd]

45 | giMXPlatformTokenSpaceGuid.PcdGpioBankMemoryRange

46 |

--------------------------------------------------------------------------------

/Drivers/PciEmulation/PciEmulation.inf:

--------------------------------------------------------------------------------

1 | #

2 | # Copyright (C) Microsoft. All rights reserved

3 | #

4 | #%HEADER%

5 | /** @file

6 |

7 | Copyright (c) 2009 Apple, Inc. All rights reserved.

8 |

9 | This document is the property of Apple, Inc.

10 | It is considered confidential and proprietary.

11 |

12 | This document may not be reproduced or transmitted in any form,

13 | in whole or in part, without the express written permission of

14 | Apple, Inc.

15 |

16 | **/

17 |

18 | [Defines]

19 | INF_VERSION = 0x00010005

20 | BASE_NAME = PciEmulation

21 | FILE_GUID = E87C242E-7341-46d7-B84B-593BC6E4F3E8

22 | MODULE_TYPE = DXE_DRIVER

23 | VERSION_STRING = 1.0

24 | ENTRY_POINT = PciEmulationEntryPoint

25 |

26 | [Sources.common]

27 | PciEmulation.c

28 |

29 | [Packages]

30 | EmbeddedPkg/EmbeddedPkg.dec

31 | MdeModulePkg/MdeModulePkg.dec

32 | MdePkg/MdePkg.dec

33 | PrimeG2Pkg/PrimeG2Pkg.dec

34 |

35 | [LibraryClasses]

36 | NonDiscoverableDeviceRegistrationLib

37 | UefiDriverEntryPoint

38 | iMX6IoMuxLib

39 | iMX6UsbPhyLib

40 | iMX6ClkPwrLib

41 |

42 | [Protocols]

43 |

44 | [Pcd]

45 | gPrimeG2PkgTokenSpaceGuid.PcdEHCIBase

46 | gPrimeG2PkgTokenSpaceGuid.PcdEHCILength

47 | gPrimeG2PkgTokenSpaceGuid.PcdIsUsbPortOTG

48 | gPrimeG2PkgTokenSpaceGuid.PcdUSBOTGBase

49 | giMXPlatformTokenSpaceGuid.PcdGpioBankMemoryRange

50 |

51 | [Depex]

52 | TRUE

53 |

--------------------------------------------------------------------------------

/Drivers/LcdFbDxe/LcdFbDxe.inf:

--------------------------------------------------------------------------------

1 | # SimpleFbDxe.inf: Implements Simple FrameBuffer in UEFI.

2 |

3 | [Defines]

4 | INF_VERSION = 0x00010005

5 | BASE_NAME = SimpleFbDxe

6 | FILE_GUID = dcfd1e6d-788d-4ffc-8e1b-ca2f75651a92

7 | MODULE_TYPE = DXE_DRIVER

8 | VERSION_STRING = 1.0

9 | ENTRY_POINT = SimpleFbDxeInitialize

10 |

11 | [Sources.common]

12 | SimpleFbDxe.c

13 |

14 | [Packages]

15 | MdePkg/MdePkg.dec

16 | MdeModulePkg/MdeModulePkg.dec

17 | EmbeddedPkg/EmbeddedPkg.dec

18 | ArmPkg/ArmPkg.dec

19 | PrimeG2Pkg/PrimeG2Pkg.dec

20 |

21 | [LibraryClasses]

22 | BaseLib

23 | ReportStatusCodeLib

24 | UefiLib

25 | UefiBootServicesTableLib

26 | UefiDriverEntryPoint

27 | BaseMemoryLib

28 | DebugLib

29 | CompilerIntrinsicsLib

30 | CacheMaintenanceLib

31 | FrameBufferBltLib

32 | PcdLib

33 | IoLib

34 |

35 | [Protocols]

36 | gEfiGraphicsOutputProtocolGuid ## PRODUCES

37 | gEfiCpuArchProtocolGuid

38 |

39 | [FixedPcd]

40 | gPrimeG2PkgTokenSpaceGuid.PcdFrameBufferWidth

41 | gPrimeG2PkgTokenSpaceGuid.PcdFrameBufferHeight

42 | gPrimeG2PkgTokenSpaceGuid.PcdLcdIfBaseAddress

43 |

44 | [Guids]

45 | gEfiMdeModulePkgTokenSpaceGuid

46 |

47 | [Pcd]

48 | gEfiMdeModulePkgTokenSpaceGuid.PcdVideoHorizontalResolution

49 | gEfiMdeModulePkgTokenSpaceGuid.PcdVideoVerticalResolution

50 |

51 | [Depex]

52 | gEfiCpuArchProtocolGuid

53 |

--------------------------------------------------------------------------------

/Drivers/TimerDxe/TimerDxe.inf:

--------------------------------------------------------------------------------

1 | #/** @file

2 | #

3 | # Copyright (c) 2009, Apple Inc. All rights reserved.

4 | # Copyright (c) 2018 Microsoft Corporation. All rights reserved.

5 | #

6 | # All rights reserved. This program and the accompanying materials

7 | # are licensed and made available under the terms and conditions of the BSD License

8 | # which accompanies this distribution. The full text of the license may be found at

9 | # http://opensource.org/licenses/bsd-license.php

10 | #

11 | # THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

12 | # WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

13 | #

14 | #**/

15 |

16 | [Defines]

17 | INF_VERSION = 0x0001001A

18 | BASE_NAME = iMX6TimerDxe

19 | FILE_GUID = 7CAF576F-F1D9-4104-A922-CB64537FD7AE

20 | MODULE_TYPE = DXE_DRIVER

21 | VERSION_STRING = 1.0

22 | ENTRY_POINT = TimerInitialize

23 |

24 | [Sources.common]

25 | Timer.c

26 |

27 | [Packages]

28 | ArmPkg/ArmPkg.dec

29 | EmbeddedPkg/EmbeddedPkg.dec

30 | MdePkg/MdePkg.dec

31 | PrimeG2Pkg/PrimeG2Pkg.dec

32 |

33 | [LibraryClasses]

34 | BaseLib

35 | BaseMemoryLib

36 | DebugLib

37 | IoLib

38 | PerformanceLib

39 | UefiBootServicesTableLib

40 | UefiDriverEntryPoint

41 | UefiLib

42 | UefiRuntimeServicesTableLib

43 |

44 | [Guids]

45 |

46 | [Protocols]

47 | gEfiTimerArchProtocolGuid

48 | gHardwareInterruptProtocolGuid

49 |

50 | [Pcd.common]

51 | gEmbeddedTokenSpaceGuid.PcdTimerPeriod

52 |

53 | [Depex]

54 | gHardwareInterruptProtocolGuid

55 |

--------------------------------------------------------------------------------

/Library/TimerLib/TimerLib.inf:

--------------------------------------------------------------------------------

1 | ## @file

2 | #

3 | # NULL instance of Timer Library as a template.

4 | #

5 | # A non-functional instance of the Timer Library that can be used as a template

6 | # for the implementation of a functional timer library instance. This library

7 | # instance can also be used to test build DXE, Runtime, DXE SAL, and DXE SMM

8 | # modules that require timer services as well as EBC modules that require

9 | # timer services.

10 | #

11 | # Copyright (c) 2018 Microsoft Corporation. All rights reserved.

12 | # Copyright (c) 2007 - 2008, Intel Corporation.

13 | #

14 | # This program and the accompanying materials

15 | # are licensed and made available under the terms and conditions of the BSD License

16 | # which accompanies this distribution. The full text of the license may be found at

17 | # http://opensource.org/licenses/bsd-license.php

18 | #

19 | # THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

20 | # WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

21 | #

22 | ##

23 |

24 | [Defines]

25 | INF_VERSION = 0x0001001A

26 | BASE_NAME = iMX6TimerLib

27 | FILE_GUID = 2956C1A6-6FF8-4763-9FD8-D45892E025E3

28 | MODULE_TYPE = BASE

29 | VERSION_STRING = 1.0

30 | LIBRARY_CLASS = TimerLib

31 |

32 | [Sources.common]

33 | TimerLib.c

34 |

35 | [Packages]

36 | ArmPkg/ArmPkg.dec

37 | MdePkg/MdePkg.dec

38 | PrimeG2Pkg/PrimeG2Pkg.dec

39 |

40 | [LibraryClasses]

41 | DebugLib

42 | IoLib

43 |

44 | [Pcd]

45 | gArmTokenSpaceGuid.PcdArmArchTimerFreqInHz

--------------------------------------------------------------------------------

/Library/iMX6ULLResetSystemLib/iMX6ULLResetSystemLib.inf:

--------------------------------------------------------------------------------

1 | #/** @file

2 | # Reset System lib using iMX6 registers

3 | #

4 | # Copyright (c) 2008, Apple Inc. All rights reserved.

5 | # Copyright (c) 2014, Linaro Ltd. All rights reserved.

6 | # Copyright (c) 2014, ARM Ltd. All rights reserved.

7 | # Copyright (c) 2019, Bingxing Wang. All rights reserved.

8 | #

9 | # This program and the accompanying materials

10 | # are licensed and made available under the terms and conditions of the BSD License

11 | # which accompanies this distribution. The full text of the license may be found at

12 | # http://opensource.org/licenses/bsd-license.php

13 | # THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

14 | # WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

15 | #

16 | #

17 | #**/

18 |

19 | [Defines]

20 | INF_VERSION = 0x00010005

21 | BASE_NAME = iMX6ULLResetSystemLib

22 | FILE_GUID = b764ad02-18db-4c86-802f-5a3f14c124cf

23 | MODULE_TYPE = BASE

24 | VERSION_STRING = 1.0

25 | LIBRARY_CLASS = EfiResetSystemLib

26 |

27 | [Sources]

28 | iMX6ULLResetSystemLib.c

29 |

30 | [Packages]

31 | ArmPkg/ArmPkg.dec

32 | MdePkg/MdePkg.dec

33 | EmbeddedPkg/EmbeddedPkg.dec

34 | PrimeG2Pkg/PrimeG2Pkg.dec

35 |

36 | [Guids]

37 | gEfiEventVirtualAddressChangeGuid

38 |

39 | [LibraryClasses]

40 | ArmLib

41 | DebugLib

42 | BaseLib

43 | IoLib

44 | UefiBootServicesTableLib

45 | UefiRuntimeServicesTableLib

46 | DxeServicesTableLib

--------------------------------------------------------------------------------

/Library/PlatformLib/PlatformLib.inf:

--------------------------------------------------------------------------------

1 | #/* @file

2 | # Copyright (c) 2011-2012, ARM Limited. All rights reserved.

3 | #

4 | # This program and the accompanying materials

5 | # are licensed and made available under the terms and conditions of the BSD License

6 | # which accompanies this distribution. The full text of the license may be found at

7 | # http://opensource.org/licenses/bsd-license.php

8 | #

9 | # THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

10 | # WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

11 | #

12 | #*/

13 |

14 | [Defines]

15 | INF_VERSION = 0x00010005

16 | BASE_NAME = ArmPlatformLibNull

17 | FILE_GUID = cb494bad-23ff-427e-8608-d7e138d3363b

18 | MODULE_TYPE = BASE

19 | VERSION_STRING = 1.0

20 | LIBRARY_CLASS = ArmPlatformLib

21 |

22 | [Packages]

23 | MdePkg/MdePkg.dec

24 | MdeModulePkg/MdeModulePkg.dec

25 | ArmPkg/ArmPkg.dec

26 | ArmPlatformPkg/ArmPlatformPkg.dec

27 | PrimeG2Pkg/PrimeG2Pkg.dec

28 |

29 | [LibraryClasses]

30 | ArmLib

31 | DebugLib

32 | IoLib

33 | TimerLib

34 |

35 | [Sources.common]

36 | ArmPlatformLib.c

37 | ArmPlatformLibMem.c

38 |

39 | [Sources.Arm]

40 | Arm/ArmPlatformHelper.S | GCC

41 | Arm/ArmPlatformHelper.asm | RVCT

42 |

43 | [FixedPcd]

44 | gArmTokenSpaceGuid.PcdArmPrimaryCoreMask

45 | gArmTokenSpaceGuid.PcdArmPrimaryCore

46 | gPrimeG2PkgTokenSpaceGuid.PcdLcdIfBaseAddress

47 | gPrimeG2PkgTokenSpaceGuid.PcdFrameBufferWidth

48 | gPrimeG2PkgTokenSpaceGuid.PcdFrameBufferHeight

49 |

50 | [Ppis]

51 | gArmMpCoreInfoPpiGuid

52 |

--------------------------------------------------------------------------------

/AcpiTables/Dsdt/Dsdt-Gpio.asl:

--------------------------------------------------------------------------------

1 | /** @file

2 | *

3 | * Copyright (c) 2018 Microsoft Corporation. All rights reserved.

4 | *

5 | * This program and the accompanying materials

6 | * are licensed and made available under the terms and conditions of the BSD License

7 | * which accompanies this distribution. The full text of the license may be found at

8 | * http://opensource.org/licenses/bsd-license.php

9 | *

10 | * THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | * WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | *

13 | **/

14 |

15 | Device (GPIO)

16 | {

17 | Name (_HID, "NXP0103")

18 | Name (_UID, 0x0)

19 |

20 | Method (_STA) {

21 | Return (0xf)

22 | }

23 |

24 | Name (_CRS, ResourceTemplate () {

25 | // GPIO1-7

26 | MEMORY32FIXED (ReadWrite, 0x0209C000, 0x1C000, )

27 |

28 | // IOMUXC

29 | MEMORY32FIXED (ReadWrite, 0x020E0000, 0x4000, )

30 |

31 | // GPIO1 0-15, 16-31

32 | Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) { 98, 99 }

33 |

34 | // GPIO2 0-15, 16-31

35 | Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) { 100, 101 }

36 |

37 | // GPIO3 0-15, 16-31

38 | Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) { 102, 103 }

39 |

40 | // GPIO4 0-15, 16-31

41 | Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) { 104, 105 }

42 |

43 | // GPIO5 0-15, 16-31

44 | Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) { 106, 107 }

45 |

46 | // GPIO6 0-15, 16-31

47 | Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) { 108, 109 }

48 |

49 | // GPIO7 0-15, 16-31

50 | Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) { 110, 111 }

51 | })

52 |

53 | OperationRegion (OTGP, GeneralPurposeIO, Zero, One)

54 | }

55 |

--------------------------------------------------------------------------------

/AcpiTables/AcpiTables.inf:

--------------------------------------------------------------------------------

1 | ## @file

2 | # Component description file for PlatformAcpiTables module.

3 | #

4 | # ACPI table data and ASL sources required to boot the platform.

5 | #

6 | # Copyright (c) 2018 Microsoft Corporation. All rights reserved.

7 | #

8 | # This program and the accompanying materials

9 | # are licensed and made available under the terms and conditions of the BSD License

10 | # which accompanies this distribution. The full text of the license may be found at

11 | # http://opensource.org/licenses/bsd-license.php

12 | #

13 | # THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

14 | # WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

15 | #

16 | ##

17 |

18 | [Defines]

19 | INF_VERSION = 0x0001001A

20 | BASE_NAME = PlatformAcpiTables

21 | FILE_GUID = 7E374E25-8E01-4FEE-87F2-390C23C606CD

22 | MODULE_TYPE = USER_DEFINED

23 | VERSION_STRING = 1.0

24 |

25 | [Sources]

26 | Dsdt/DSDT.asl

27 | Csrt.aslc

28 | Dbg2.aslc

29 | Fadt.aslc

30 | Madt.asl

31 | Facs.asl

32 | Gtdt.aslc

33 |

34 | [BuildOptions.ARM]

35 | GCC:*_*_*_CC_FLAGS = -Wno-missing-braces

36 |

37 | [Packages]

38 | ArmPkg/ArmPkg.dec

39 | ArmPlatformPkg/ArmPlatformPkg.dec

40 | EmbeddedPkg/EmbeddedPkg.dec

41 | MdeModulePkg/MdeModulePkg.dec

42 | MdePkg/MdePkg.dec

43 | PrimeG2Pkg/PrimeG2Pkg.dec

44 |

45 | [FixedPcd]

46 | gArmPlatformTokenSpaceGuid.PcdCoreCount

47 | gArmTokenSpaceGuid.PcdGicDistributorBase

48 | gArmTokenSpaceGuid.PcdGicInterruptInterfaceBase

49 | giMXPlatformTokenSpaceGuid.PcdKdUartInstance

50 |

51 | gArmTokenSpaceGuid.PcdArmArchTimerVirtIntrNum

52 | gArmTokenSpaceGuid.PcdArmArchTimerHypIntrNum

53 | gArmTokenSpaceGuid.PcdArmArchTimerSecIntrNum

54 | gArmTokenSpaceGuid.PcdArmArchTimerIntrNum

--------------------------------------------------------------------------------

/AcpiTables/Dsdt/Dsdt-Usb.asl:

--------------------------------------------------------------------------------

1 | /** @file

2 | *

3 | * iMX6 ULL EHCI USB Controllers

4 | *

5 | * Copyright (c) 2018 Microsoft Corporation. All rights reserved.

6 | *

7 | * This program and the accompanying materials

8 | * are licensed and made available under the terms and conditions of the BSD License

9 | * which accompanies this distribution. The full text of the license may be found at

10 | * http://opensource.org/licenses/bsd-license.php

11 | *

12 | * THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

13 | * WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

14 | *

15 | **/

16 |

17 | // Pre-configured to USB Host mode

18 | Device (USB0) {

19 | Name(_HID, "PNP0D20")

20 | Name(_UID, 0x0)

21 |

22 | Name (_S0W, 0x0) // D0 is the lowest supported state to wake itself up

23 | Method (_STA) {

24 | Return (0xf)

25 | }

26 |

27 | Method (_CRS, 0x0, Serialized) {

28 | Name (RBUF, ResourceTemplate () {

29 | MEMORY32FIXED(ReadWrite, 0x02184100, 0x100, )

30 | Interrupt (ResourceConsumer, Level, ActiveHigh, SharedAndWake) { 75 }

31 | })

32 | Return(RBUF)

33 | }

34 |

35 | OperationRegion (OTGM, SystemMemory, 0x02184100, 0x100)

36 | Field (OTGM, WordAcc, NoLock, Preserve) {

37 | Offset (0x84), // skip to register 84h

38 | PTSC, 32, // port status control

39 | Offset (0xA8), // skip to register A8h

40 | DSBM, 32, // UOG_USBMOD

41 | }

42 |

43 | Name (REG, 0x0) // Declare register read variable

44 | Method (_UBF, 0x0, Serialized) {

45 | // Reset handled by driver so no reset required here

46 | Store (0x03, DSBM); // set host mode & little endian

47 | Store (PTSC, REG); // read PORTSC status

48 | Store (OR (REG, 0x2), PTSC); // clear current PORTSC status

49 | }

50 | }

51 |

--------------------------------------------------------------------------------

/Drivers/PlatformSmbiosDxe/PlatformSmbiosDxe.inf:

--------------------------------------------------------------------------------

1 | #/** @file

2 | #

3 | # Copyright (c) 2013 Linaro.org

4 | # Copyright (c) 2018 Microsoft Corporation. All rights reserved.

5 | #

6 | # This program and the accompanying materials

7 | # are licensed and made available under the terms and conditions of the BSD License

8 | # which accompanies this distribution. The full text of the license may be found at

9 | # http://opensource.org/licenses/bsd-license.php

10 | #

11 | # THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

12 | # WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

13 | #

14 | #**/

15 |

16 | [Defines]

17 | INF_VERSION = 0x0001001A

18 | BASE_NAME = PlatformSmbiosDxe

19 | FILE_GUID = 3847D23F-1D95-4772-B60C-4BBFBC4D532F

20 | MODULE_TYPE = DXE_DRIVER

21 | VERSION_STRING = 1.0

22 | ENTRY_POINT = PlatformSmbiosDriverEntryPoint

23 |

24 | [Sources]

25 | PlatformSmbiosDxe.c

26 |

27 | [Packages]

28 | ArmPkg/ArmPkg.dec

29 | ArmPlatformPkg/ArmPlatformPkg.dec

30 | MdeModulePkg/MdeModulePkg.dec

31 | MdePkg/MdePkg.dec

32 | PrimeG2Pkg/PrimeG2Pkg.dec

33 |

34 | [LibraryClasses]

35 | ArmLib

36 | BaseLib

37 | BaseMemoryLib

38 | DebugLib

39 | IoLib

40 | MemoryAllocationLib

41 | PrintLib

42 | UefiBootServicesTableLib

43 | UefiDriverEntryPoint

44 | UefiLib

45 |

46 | [Protocols]

47 | gEfiSmbiosProtocolGuid # PROTOCOL SOMETIMES_CONSUMED

48 |

49 | [Guids]

50 |

51 | [FixedPcd]

52 | gArmPlatformTokenSpaceGuid.PcdCoreCount

53 | gArmTokenSpaceGuid.PcdFdSize

54 | gArmTokenSpaceGuid.PcdSystemMemorySize

55 | gArmTokenSpaceGuid.PcdSystemMemoryBase

56 | gEfiMdeModulePkgTokenSpaceGuid.PcdFirmwareRevision

57 | gEfiMdeModulePkgTokenSpaceGuid.PcdFirmwareVendor

58 | giMXPlatformTokenSpaceGuid.PcdSystemUuid

59 | giMXPlatformTokenSpaceGuid.PcdPhysicalMemoryMaximumCapacity

60 |

61 | [Depex]

62 | gEfiSmbiosProtocolGuid

63 |

--------------------------------------------------------------------------------

/Drivers/LogoDxe/LogoDxe.inf:

--------------------------------------------------------------------------------

1 | ## @file

2 | # The default logo bitmap picture shown on setup screen.

3 | #

4 | # Copyright (c) 2016 - 2017, Intel Corporation. All rights reserved.

5 | #

6 | # This program and the accompanying materials

7 | # are licensed and made available under the terms and conditions of the BSD License

8 | # which accompanies this distribution. The full text of the license may be found at

9 | # http://opensource.org/licenses/bsd-license.php

10 | # THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | # WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | #

13 | #

14 | ##

15 |

16 | [Defines]

17 | INF_VERSION = 0x00010005

18 | BASE_NAME = LogoDxe

19 | MODULE_UNI_FILE = LogoDxe.uni

20 | FILE_GUID = F74D20EE-37E7-48FC-97F7-9B1047749C69

21 | MODULE_TYPE = DXE_DRIVER

22 | VERSION_STRING = 1.0

23 |

24 | ENTRY_POINT = InitializeLogo

25 | #

26 | # This flag specifies whether HII resource section is generated into PE image.

27 | #

28 | UEFI_HII_RESOURCE_SECTION = TRUE

29 |

30 | #

31 | # The following information is for reference only and not required by the build tools.

32 | #

33 | # VALID_ARCHITECTURES = IA32 X64

34 | #

35 |

36 | [Sources]

37 | Logo.bmp

38 | Logo.c

39 | Logo.idf

40 |

41 | [Packages]

42 | MdeModulePkg/MdeModulePkg.dec

43 | MdePkg/MdePkg.dec

44 |

45 | [LibraryClasses]

46 | UefiBootServicesTableLib

47 | UefiDriverEntryPoint

48 | DebugLib

49 |

50 | [Protocols]

51 | gEfiHiiDatabaseProtocolGuid ## CONSUMES

52 | gEfiHiiImageExProtocolGuid ## CONSUMES

53 | gEfiHiiPackageListProtocolGuid ## PRODUCES CONSUMES

54 | gEdkiiPlatformLogoProtocolGuid ## PRODUCES

55 |

56 | [Depex]

57 | gEfiHiiDatabaseProtocolGuid AND

58 | gEfiHiiImageExProtocolGuid

59 |

60 | [UserExtensions.TianoCore."ExtraFiles"]

61 | LogoDxeExtra.uni

62 |

--------------------------------------------------------------------------------

/Library/PlatformLib/Arm/ArmPlatformHelper.asm:

--------------------------------------------------------------------------------

1 | //

2 | // Copyright (c) 2012-2013, ARM Limited. All rights reserved.

3 | //

4 | // This program and the accompanying materials

5 | // are licensed and made available under the terms and conditions of the BSD License

6 | // which accompanies this distribution. The full text of the license may be found at

7 | // http://opensource.org/licenses/bsd-license.php

8 | //

9 | // THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

10 | // WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

11 | //

12 | //

13 |

14 | #include

15 |

16 | INCLUDE AsmMacroIoLib.inc

17 |

18 | EXPORT ArmPlatformPeiBootAction

19 | EXPORT ArmPlatformGetCorePosition

20 | EXPORT ArmPlatformGetPrimaryCoreMpId

21 | EXPORT ArmPlatformIsPrimaryCore

22 |

23 | IMPORT _gPcd_FixedAtBuild_PcdArmPrimaryCore

24 | IMPORT _gPcd_FixedAtBuild_PcdArmPrimaryCoreMask

25 |

26 | PRESERVE8

27 | AREA ArmPlatformNullHelper, CODE, READONLY

28 |

29 | ArmPlatformPeiBootAction FUNCTION

30 | mrc p15, 0, r0, c1, c0, 0

31 | bic r0, r0, #2

32 | mcr p15, 0, r0, c1, c0, 0

33 | bx lr

34 | ENDFUNC

35 |

36 | //UINTN

37 | //ArmPlatformGetCorePosition (

38 | // IN UINTN MpId

39 | // );

40 | ArmPlatformGetCorePosition FUNCTION

41 | and r1, r0, #ARM_CORE_MASK

42 | and r0, r0, #ARM_CLUSTER_MASK

43 | add r0, r1, r0, LSR #7

44 | bx lr

45 | ENDFUNC

46 |

47 | //UINTN

48 | //ArmPlatformGetPrimaryCoreMpId (

49 | // VOID

50 | // );

51 | ArmPlatformGetPrimaryCoreMpId FUNCTION

52 | mov32 r0, FixedPcdGet32(PcdArmPrimaryCore)

53 | bx lr

54 | ENDFUNC

55 |

56 | //UINTN

57 | //ArmPlatformIsPrimaryCore (

58 | // IN UINTN MpId

59 | // );

60 | ArmPlatformIsPrimaryCore FUNCTION

61 | mov32 r1, FixedPcdGet32(PcdArmPrimaryCoreMask)

62 | and r0, r0, r1

63 | mov32 r1, FixedPcdGet32(PcdArmPrimaryCore)

64 | cmp r0, r1

65 | moveq r0, #1

66 | movne r0, #0

67 | bx lr

68 | ENDFUNC

69 |

70 | END

71 |

72 |

--------------------------------------------------------------------------------

/AcpiTables/Dsdt/Dsdt-Platform.asl:

--------------------------------------------------------------------------------

1 | /** @file

2 | *

3 | * Copyright (c) 2018 Microsoft Corporation. All rights reserved.

4 | *

5 | * This program and the accompanying materials

6 | * are licensed and made available under the terms and conditions of the BSD License

7 | * which accompanies this distribution. The full text of the license may be found at

8 | * http://opensource.org/licenses/bsd-license.php

9 | *

10 | * THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

11 | * WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

12 | *

13 | **/

14 |

15 | OperationRegion (GLBL, SystemMemory, 0x10817000, 0x10)

16 | Field (GLBL, AnyAcc, Nolock, Preserve)

17 | {

18 | Offset (0), // Miscellaneous Dynamic Registers:

19 | SIGN, 32, // Global Page Signature 'GLBL'

20 | REVN, 8, // Revision

21 | , 8, // Reserved

22 | , 8, // Reserved

23 | , 8, // Reserved

24 | M0ID, 8, // MAC 0 ID

25 | MC0V, 8, // MAC 0 Valid

26 | MC0L, 32, // MAC Address 0 Low

27 | MC0H, 16, // MAC Address 0 High

28 | }

29 |

30 | Device (CPU0)

31 | {

32 | Name (_HID, "ACPI0007")

33 | Name (_UID, 0x0)

34 |

35 | Method (_STA) {

36 | Return (0xf)

37 | }

38 | }

39 |

40 | // Timers HAL extension

41 | Device (EPIT)

42 | {

43 | Name (_HID, "NXP0101")

44 | Name (_UID, 0x0)

45 |

46 | Method (_STA) {

47 | Return (0xf)

48 | }

49 | }

50 |

51 | // Platform Extension Plugin

52 | /*Device (PEP0)

53 | {

54 | Name (_HID, "NXP0102")

55 | Name (_UID, 0x0)

56 |

57 | Method (_STA) {

58 | Return (0xf)

59 | }

60 | Name (_CRS, ResourceTemplate () {

61 | // CCM request 1

62 | Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) { 119 }

63 |

64 | // CCM request 2

65 | Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) { 120 }

66 |

67 | // GPC request 1

68 | Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) { 121 }

69 |

70 | // UART1

71 | Interrupt (ResourceConsumer, Level, ActiveHigh, Shared) { 58 }

72 | })

73 | }*/

74 |

--------------------------------------------------------------------------------

/Library/PlatformLib/Arm/ArmPlatformHelper.S:

--------------------------------------------------------------------------------

1 | //

2 | // Copyright (c) 2012-2013, ARM Limited. All rights reserved.

3 | //

4 | // This program and the accompanying materials

5 | // are licensed and made available under the terms and conditions of the BSD License

6 | // which accompanies this distribution. The full text of the license may be found at

7 | // http://opensource.org/licenses/bsd-license.php

8 | //

9 | // THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

10 | // WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

11 | //

12 | //

13 |

14 | #include

15 | #include

16 |

17 | ASM_FUNC(ArmPlatformPeiBootAction)

18 | // Disable L2 cache

19 | mrc p15, 0, r0, c1, c0, 1

20 | bic r0, r0, #0x00000002

21 | mcr p15, 0, r0, c1, c0, 1

22 | // Disable Strict alignment checking & Enable Instruction cache

23 | mrc p15, 0, r0, c1, c0, 0

24 | bic r0, r0, #0x00002300 /* clear bits 13, 9:8 (--V- --RS) */

25 | bic r0, r0, #0x00000005 /* clear bits 0, 2 (---- -C-M) */

26 | bic r0, r0, #0x00000002 /* Clear bit 1 (Alignment faults) */

27 | orr r0, r0, #0x00001000 /* set bit 12 (I) enable I-Cache */

28 | mcr p15, 0, r0, c1, c0, 0

29 | bx lr

30 |

31 | //UINTN

32 | //ArmPlatformGetCorePosition (

33 | // IN UINTN MpId

34 | // );

35 | ASM_FUNC(ArmPlatformGetCorePosition)

36 | and r1, r0, #ARM_CORE_MASK

37 | and r0, r0, #ARM_CLUSTER_MASK

38 | add r0, r1, r0, LSR #7

39 | bx lr

40 |

41 | //UINTN

42 | //ArmPlatformGetPrimaryCoreMpId (

43 | // VOID

44 | // );

45 | ASM_FUNC(ArmPlatformGetPrimaryCoreMpId)

46 | MOV32 (r0, FixedPcdGet32 (PcdArmPrimaryCore))

47 | bx lr

48 |

49 | //UINTN

50 | //ArmPlatformIsPrimaryCore (

51 | // IN UINTN MpId

52 | // );

53 | ASM_FUNC(ArmPlatformIsPrimaryCore)

54 | MOV32 (r1, FixedPcdGet32 (PcdArmPrimaryCoreMask))

55 | and r0, r0, r1

56 | MOV32 (r1, FixedPcdGet32 (PcdArmPrimaryCore))

57 | cmp r0, r1

58 | moveq r0, #1

59 | movne r0, #0

60 | bx lr

61 |

--------------------------------------------------------------------------------

/Library/PlatformBootManagerLib/PlatformBm.h:

--------------------------------------------------------------------------------

1 | /** @file

2 | Head file for BDS Platform specific code

3 |

4 | Copyright (C) 2015-2016, Red Hat, Inc.

5 | Copyright (c) 2004 - 2008, Intel Corporation. All rights reserved.

6 | Copyright (c) 2016, Linaro Ltd. All rights reserved.

7 |

8 | This program and the accompanying materials are licensed and made available

9 | under the terms and conditions of the BSD License which accompanies this

10 | distribution. The full text of the license may be found at

11 | http://opensource.org/licenses/bsd-license.php

12 |

13 | THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS, WITHOUT

14 | WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

15 |

16 | **/

17 |

18 | #ifndef _PLATFORM_BM_H_

19 | #define _PLATFORM_BM_H_

20 |

21 | #include

22 | #include

23 | #include

24 | #include

25 | #include

26 | #include

27 | #include

28 | #include

29 |

30 | /**

31 | Use SystemTable Conout to stop video based Simple Text Out consoles from

32 | going to the video device. Put up LogoFile on every video device that is a

33 | console.

34 |

35 | @param[in] LogoFile File name of logo to display on the center of the

36 | screen.

37 |

38 | @retval EFI_SUCCESS ConsoleControl has been flipped to graphics and logo

39 | displayed.

40 | @retval EFI_UNSUPPORTED Logo not found

41 | **/

42 | EFI_STATUS

43 | EnableQuietBoot (

44 | IN EFI_GUID *LogoFile

45 | );

46 |

47 | /**

48 | Use SystemTable Conout to turn on video based Simple Text Out consoles. The

49 | Simple Text Out screens will now be synced up with all non video output

50 | devices

51 |

52 | @retval EFI_SUCCESS UGA devices are back in text mode and synced up.

53 | **/

54 | EFI_STATUS

55 | DisableQuietBoot (

56 | VOID

57 | );

58 |

59 | #endif // _PLATFORM_BM_H_

60 |

--------------------------------------------------------------------------------

/Drivers/ConSplitterDxe/ConSplitterDxe.uni:

--------------------------------------------------------------------------------

1 | // /** @file

2 | // This driver provides multi console supports.

3 | //

4 | // This driver acts as a virtual console, takes over the console I/O control from selected

5 | // standard console devices, and transmits console I/O to related console device drivers.

6 | // Consplitter could install Graphics Output protocol and/or UGA Draw protocol in system

7 | // table according PCD settings(PcdConOutGopSupport, and PcdConOutUgaSupport). It always

8 | // consumes Graphics Output protocol which is produced by display device, and consumes UGA Draw

9 | // protocol which is produced by display device according to PcdUgaConsumeSupport value.

10 | // Note: If only UGA Draw protocol is installed in system, PcdUgaConsumeSupport should be

11 | // set to TRUE.

12 | //

13 | // Copyright (c) 2006 - 2014, Intel Corporation. All rights reserved.

14 | //

15 | // This program and the accompanying materials

16 | // are licensed and made available under the terms and conditions of the BSD License

17 | // which accompanies this distribution. The full text of the license may be found at

18 | // http://opensource.org/licenses/bsd-license.php

19 | // THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

20 | // WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

21 | //

22 | // **/

23 |

24 |

25 | #string STR_MODULE_ABSTRACT #language en-US "Provides multi console support"

26 |

27 | #string STR_MODULE_DESCRIPTION #language en-US "This driver acts as a virtual console, takes over the console I/O control from selected standard console devices, and transmits console I/O to related console device drivers. Consplitter could install Graphics Output protocol and/or UGA Draw protocol in system table according PCD settings(PcdConOutGopSupport, and PcdConOutUgaSupport). It always consumes Graphics Output protocol, which is produced by display device, and consumes UGA Draw protocol, which is produced by display device according to PcdUgaConsumeSupport value. Note: If only UGA Draw protocol is installed in system, PcdUgaConsumeSupport should be set to TRUE."

28 |

29 |

--------------------------------------------------------------------------------

/Include/Device/iMX6ClkPwr.h:

--------------------------------------------------------------------------------

1 | /** @file

2 | *

3 | * Copyright (c) 2018 Microsoft Corporation. All rights reserved.

4 | * Copyright 2018 NXP

5 | *

6 | * This program and the accompanying materials

7 | * are licensed and made available under the terms and conditions of the BSD License

8 | * which accompanies this distribution. The full text of the license may be found at

9 | * http://opensource.org/licenses/bsd-license.php

10 | *

11 | * THE PROGRAM IS DISTRIBUTED UNDER THE BSD LICENSE ON AN "AS IS" BASIS,

12 | * WITHOUT WARRANTIES OR REPRESENTATIONS OF ANY KIND, EITHER EXPRESS OR IMPLIED.

13 | *

14 | **/

15 |

16 | #ifndef _IMX6_CLK_PWR_H_

17 | #define _IMX6_CLK_PWR_H_

18 |

19 | // The valid value for PLL loop divider is 27-54 so define the range of valid

20 | // frequency for PLL5 below before divider is applied.

21 | #define PLL5_MIN_FREQ 648000000

22 | #define PLL5_MAX_FREQ 1296000000

23 |

24 | #include "iMX6ClkPwr_ULL.h"

25 |

26 | typedef enum {

27 | IMX_CLOCK_GATE_STATE_OFF = 0x0,

28 | IMX_CLOCK_GATE_STATE_ON_RUN = 0x1,

29 | IMX_CLOCK_GATE_STATE_ON = 0x3,

30 | } IMX_CLOCK_GATE_STATE;

31 |

32 | typedef struct {

33 | UINT32 Frequency;

34 | IMX_CLK Parent;

35 | } IMX_CLOCK_INFO;

36 |

37 | VOID

38 | ImxClkPwrSetClockGate (

39 | IN IMX_CLK_GATE ClockGate,

40 | IN IMX_CLOCK_GATE_STATE State

41 | );

42 |

43 | // Set multiple clock gates to a given state

44 | VOID

45 | ImxClkPwrSetClockGates (

46 | IN CONST IMX_CLK_GATE *ClockGateList,

47 | IN UINTN ClockGateCount,

48 | IN IMX_CLOCK_GATE_STATE State

49 | );

50 |

51 | IMX_CLOCK_GATE_STATE

52 | ImxClkPwrGetClockGate (

53 | IN IMX_CLK_GATE ClockGate

54 | );

55 |

56 | EFI_STATUS

57 | ImxClkPwrGetClockInfo (

58 | IN IMX_CLK ClockId,

59 | OUT IMX_CLOCK_INFO *ClockInfo

60 | );

61 |

62 | EFI_STATUS

63 | ImxClkPwrGpuEnable (

64 | );

65 |

66 | EFI_STATUS