├── .gitignore

├── LICENSE

├── README.md

├── bin

├── debug

│ ├── .git-empty

│ └── helloworld_1_0.map

└── release

│ └── .git-empty

├── helloworld.qbs

├── img

├── compiler.png

├── debugger.png

├── device.png

├── kit.png

├── openocd-gdb.png

└── plugin.png

├── lib

└── STM32F4xx

│ ├── Include

│ ├── arm_common_tables.h

│ ├── arm_const_structs.h

│ ├── arm_math.h

│ ├── core_cm0.h

│ ├── core_cm0plus.h

│ ├── core_cm3.h

│ ├── core_cm4.h

│ ├── core_cm7.h

│ ├── core_cmFunc.h

│ ├── core_cmInstr.h

│ ├── core_cmSimd.h

│ ├── core_sc000.h

│ └── core_sc300.h

│ ├── STM32F4xx_StdPeriph_Driver

│ ├── Release_Notes.html

│ ├── inc

│ │ ├── misc.h

│ │ ├── stm32f4xx_adc.h

│ │ ├── stm32f4xx_can.h

│ │ ├── stm32f4xx_cec.h

│ │ ├── stm32f4xx_crc.h

│ │ ├── stm32f4xx_cryp.h

│ │ ├── stm32f4xx_dac.h

│ │ ├── stm32f4xx_dbgmcu.h

│ │ ├── stm32f4xx_dcmi.h

│ │ ├── stm32f4xx_dma.h

│ │ ├── stm32f4xx_dma2d.h

│ │ ├── stm32f4xx_dsi.h

│ │ ├── stm32f4xx_exti.h

│ │ ├── stm32f4xx_flash.h

│ │ ├── stm32f4xx_flash_ramfunc.h

│ │ ├── stm32f4xx_fmc.h

│ │ ├── stm32f4xx_fmpi2c.h

│ │ ├── stm32f4xx_fsmc.h

│ │ ├── stm32f4xx_gpio.h

│ │ ├── stm32f4xx_hash.h

│ │ ├── stm32f4xx_i2c.h

│ │ ├── stm32f4xx_iwdg.h

│ │ ├── stm32f4xx_lptim.h

│ │ ├── stm32f4xx_ltdc.h

│ │ ├── stm32f4xx_pwr.h

│ │ ├── stm32f4xx_qspi.h

│ │ ├── stm32f4xx_rcc.h

│ │ ├── stm32f4xx_rng.h

│ │ ├── stm32f4xx_rtc.h

│ │ ├── stm32f4xx_sai.h

│ │ ├── stm32f4xx_sdio.h

│ │ ├── stm32f4xx_spdifrx.h

│ │ ├── stm32f4xx_spi.h

│ │ ├── stm32f4xx_syscfg.h

│ │ ├── stm32f4xx_tim.h

│ │ ├── stm32f4xx_usart.h

│ │ └── stm32f4xx_wwdg.h

│ └── src

│ │ ├── misc.c

│ │ ├── stm32f4xx_adc.c

│ │ ├── stm32f4xx_can.c

│ │ ├── stm32f4xx_cec.c

│ │ ├── stm32f4xx_crc.c

│ │ ├── stm32f4xx_cryp.c

│ │ ├── stm32f4xx_cryp_aes.c

│ │ ├── stm32f4xx_cryp_des.c

│ │ ├── stm32f4xx_cryp_tdes.c

│ │ ├── stm32f4xx_dac.c

│ │ ├── stm32f4xx_dbgmcu.c

│ │ ├── stm32f4xx_dcmi.c

│ │ ├── stm32f4xx_dma.c

│ │ ├── stm32f4xx_dma2d.c

│ │ ├── stm32f4xx_dsi.c

│ │ ├── stm32f4xx_exti.c

│ │ ├── stm32f4xx_flash.c

│ │ ├── stm32f4xx_flash_ramfunc.c

│ │ ├── stm32f4xx_fmc.c

│ │ ├── stm32f4xx_fmpi2c.c

│ │ ├── stm32f4xx_fsmc.c

│ │ ├── stm32f4xx_gpio.c

│ │ ├── stm32f4xx_hash.c

│ │ ├── stm32f4xx_hash_md5.c

│ │ ├── stm32f4xx_hash_sha1.c

│ │ ├── stm32f4xx_i2c.c

│ │ ├── stm32f4xx_iwdg.c

│ │ ├── stm32f4xx_lptim.c

│ │ ├── stm32f4xx_ltdc.c

│ │ ├── stm32f4xx_pwr.c

│ │ ├── stm32f4xx_qspi.c

│ │ ├── stm32f4xx_rcc.c

│ │ ├── stm32f4xx_rng.c

│ │ ├── stm32f4xx_rtc.c

│ │ ├── stm32f4xx_sai.c

│ │ ├── stm32f4xx_sdio.c

│ │ ├── stm32f4xx_spdifrx.c

│ │ ├── stm32f4xx_spi.c

│ │ ├── stm32f4xx_syscfg.c

│ │ ├── stm32f4xx_tim.c

│ │ ├── stm32f4xx_usart.c

│ │ └── stm32f4xx_wwdg.c

│ ├── Startup

│ ├── startup_stm32f401xx.s

│ ├── startup_stm32f40_41xxx.s

│ ├── startup_stm32f40xx.s

│ ├── startup_stm32f427_437xx.s

│ ├── startup_stm32f427x.s

│ └── startup_stm32f429_439xx.s

│ ├── dummylib.c

│ ├── stm32f407_std.ld

│ ├── stm32f4x7_eth.c

│ ├── stm32f4x7_eth.h

│ ├── stm32f4x7_eth_bsp.c

│ ├── stm32f4x7_eth_bsp.h

│ ├── stm32f4x7_eth_conf.h

│ ├── stm32f4x7_eth_conf_template.h

│ ├── stm32f4xx.h

│ ├── system_stm32f4xx.c

│ └── system_stm32f4xx.h

├── project

├── prj.qbs

└── qbs

│ └── imports

│ ├── FileExtension.js

│ └── Stm32f4Application.qbs

└── src

└── main.c

/.gitignore:

--------------------------------------------------------------------------------

1 | # C++ objects and libs

2 |

3 | *.slo

4 | *.lo

5 | *.o

6 | *.a

7 | *.la

8 | *.lai

9 | *.so

10 | *.dll

11 | *.dylib

12 |

13 | # Qt-es

14 |

15 | /.qmake.cache

16 | /.qmake.stash

17 | *.pro.user

18 | *.pro.user.*

19 | *.qbs.user

20 | *.qbs.user.*

21 | *.moc

22 | moc_*.cpp

23 | qrc_*.cpp

24 | ui_*.h

25 | Makefile*

26 | *build-*

27 |

28 | # QtCreator

29 |

30 | *.autosave

31 |

32 | #QtCtreator Qml

33 | *.qmlproject.user

34 | *.qmlproject.user.*

35 |

--------------------------------------------------------------------------------

/README.md:

--------------------------------------------------------------------------------

1 | This reposistory is an example Qt Creator for use with ARM Cortex m-devices. This readme will describe a tutorial to set this all up.

2 | The main reason for creating this reposistory is to answer [this question thoroughly on StackExchange Electronics](http://electronics.stackexchange.com/questions/212018/creating-a-qt-project-for-an-arm-stm32-microcontroller/212077#212077)

3 |

4 | Requisites:

5 |

6 | - Qt Creator (download from QT site)

7 | - ARM GCC (Ubuntu: apt-get install gcc-arm-none-eabi)

8 | - GDB source archive (download from [archive](http://ftp.gnu.org/gnu/gdb/))

9 | - OpenOCD (Ubuntu: apt-get install openocd)

10 |

11 | I used versions: Qt Creator 3.6.0, ARM GCC 4.8.2-14ubuntu1+6, ARM GDB 7.6/7.10 with python support and OpenOCD 0.7.0.

12 |

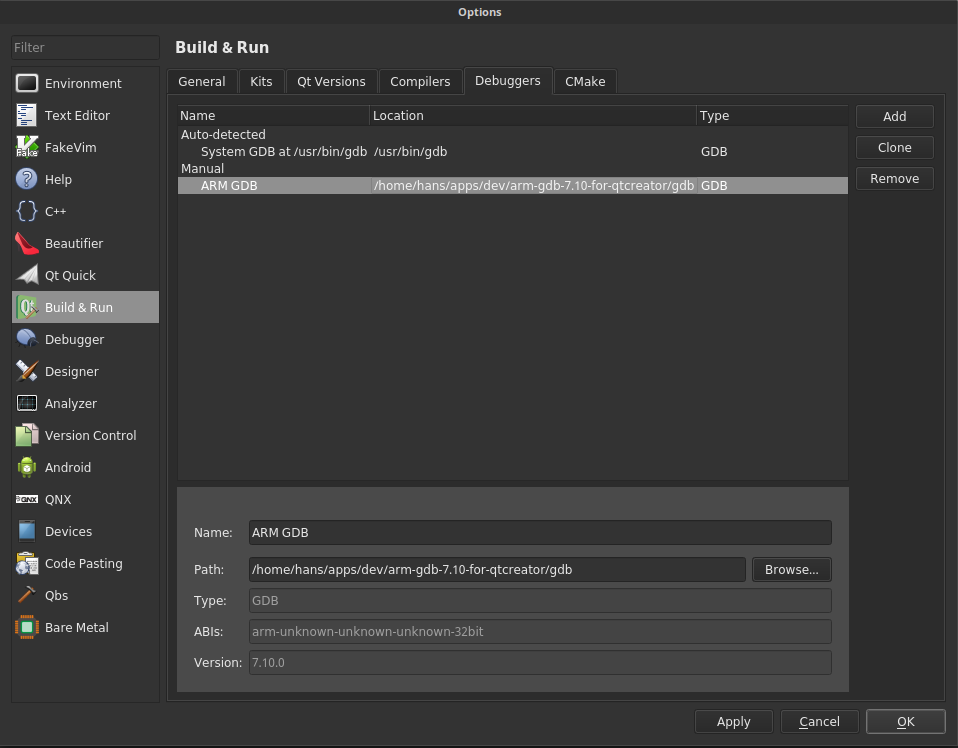

13 | 1) Install Qt Creator. Open Help -> About Plugins. Find category Device Support and check BareMetal.

14 |

15 |

16 | 2) Go to Tools -> Options. There are a few settings we need to create and adjust in order to compile for an ARM Cortex controller.

17 |

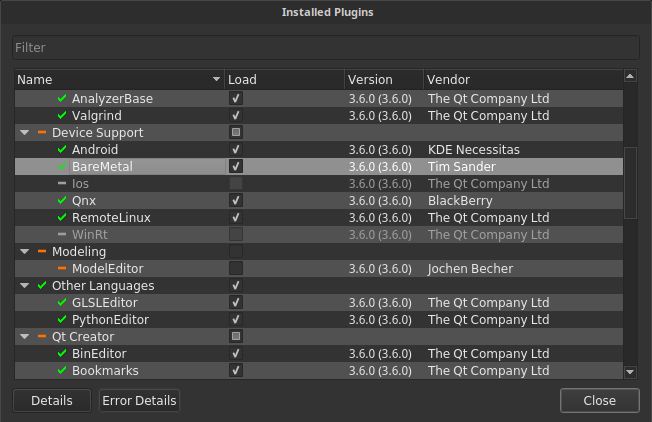

18 | a) Go to "Bare Metal" (last category) - add a debugger of your choice. I personally use OpenOCD. At this point you can set the connection to gdb and it's port, as well as init commands. The standard commands are set for STM32F4xx chips - but I guess you can modify it to work with any ARM Cortex controller.

19 |

20 |

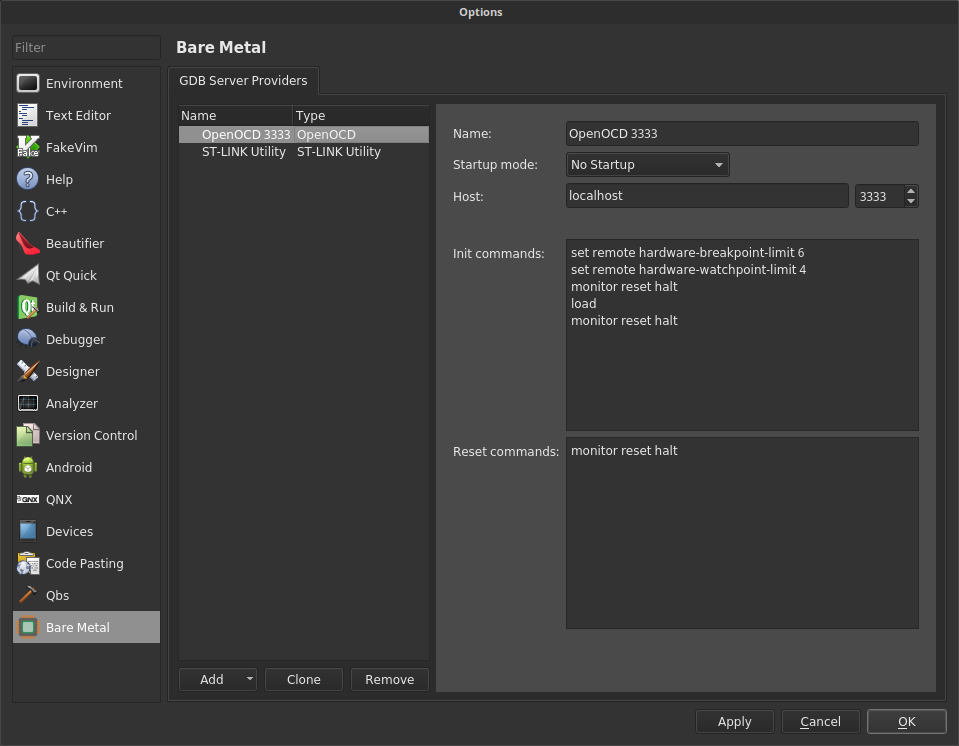

21 | b) Go to "Devices". Add a new device, choose Bare Metal and the GDB provider you have just created. There is nothing else to setup here.

22 |

23 |

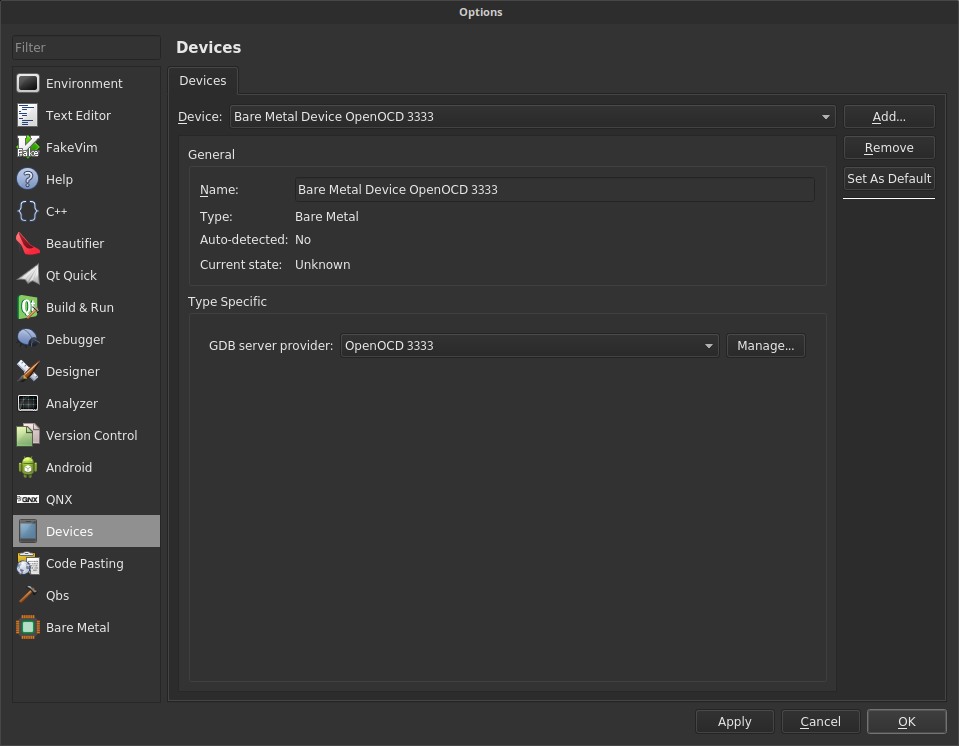

24 | c) Go to "Build & Run" - tab Debuggers. This has been the most trickiest thing to do.

25 |

26 | You need an arm gdb version **with python scripting support**. At the time (about 9 months back when I write this post) the binaries in Ubuntu repo does not have this option. You can save a lot of time/hassle by checking if this has changed.

27 |

28 | Nevertheless if you do need to compile GDB with python support, here is how to do it. Download GDB from the [download archives](http://ftp.gnu.org/gnu/gdb/). I still use GDB-7.6 which seems to work fine, but for this tutorial I have recompiled it for GDB-7.10.

29 |

30 | Extract the source archive. Open in terminal and run "./configure --with-python --target=arm-elf". This sets up the make environment for ARM targets with python scripting enabled. Then run make. This takes a while, depending on your system speed. Unfortunately you may be a bit on your own once the compilation stops because of dependency issues. Don't be afraid - this happened to me on my first try too and I figured it out with a bunch of google searches!

31 | If python fails, make sure to install the python2.x-dev package (check your version no - likely 2.7). Assuming compilation went well, you can find the gdb executable in the main directory.

32 |

33 | If you're on Mac, the process will likely be similar. But I am not familiar with OSX.

34 | If you're on Windows, sorry you will need to google a bit on how to do this with Mingw or whatever (honestly I don't know). Or maybe find binaries that have this support enabled.

35 |

36 | Once you acquired a gdb executable, call it e.g. "ARM GDB" and set the path to it. I personally don't bother to place it in /usr/bin/, but I guess you could.

37 |

38 | This window will throw an error if you use a gdb executable that is not compiled with Python Scripting.

39 |

40 |

41 | d) Tab "Build & Run" - "Compilers"

42 |

43 | Create a new "GCC compiler" and call it "ARM GCC". For path use "/usr/bin/arm-none-eabi-gcc". The "ABI" is not really important, I have just set it to arm-unknown-unknown-unknown-32bit.

44 |

45 | e) Tab "Build & Run" - "Kits". Add a new kit, I called mine "ARM Bare Metal".

46 | Device type: "Bare Metal"

47 | Device: point to the Device you have created with it's OpenOCD/St link GDB server

48 | Sysroot: leave it empty

49 | Compiler: ARM GCC

50 | Debugger: ARM GDB

51 | Qt Version: None - You obviously cannot run the QT runtime on a Cortex m4!

52 | Cmake tool: unused

53 |

54 |

55 |

56 | Make sure there are no warnings in any of the Build & Run tabs

57 |

58 | 3) Make your make/qmake/QBS project. This reposistory contains an example QBS project for the STM32F4 discovery. It contains the CMSIS library, linker script as well as an (outdated?) ethernet library for the STM32F407.

59 |

60 | On left side go to tab "projects" and at left-top add the "ARM Bare Metal" kit. This should work without errors.

61 | Your project may start out with a desktop kit. Replacing usually does not work. In that case add an ARM kit and then remove the desktop one.

62 |

63 | 4) Start your OpenOcd server. I use a STM32F4 discovery for development, and also off-board programming to my own STM32 boards. For any STM32F40x/STM32F41x targets run:

64 |

65 | openocd -f board/stm32f4discovery.cfg

66 |

67 | This starts a gdb server at port 3333 and a telnet server (for OpenOCD commands) at 4444. As a shortcut I create a few .sh files in my home directory for a quick startup of a GDB server.

68 |

69 | 5) Start the debug session. It should program and run now! :)

70 |

71 | You can set breakpoints, step through code, even move PC back, watch call stack, variables (locals / watch), and disassembly. I'm really quited please with this, but obviously it lacks a few things like:

72 |

73 | 1) "Register view". Yes it has one, but that's just the CPU registers. I want register view of my peripherals as well.

74 | 2) Download progress or more detailed info about connection state. You need to refer to openocd for this.

75 |

--------------------------------------------------------------------------------

/bin/debug/.git-empty:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/nlhans/qt-baremetal/c18a010c0cd4b711e5bd58f136a6252e073479b8/bin/debug/.git-empty

--------------------------------------------------------------------------------

/bin/release/.git-empty:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/nlhans/qt-baremetal/c18a010c0cd4b711e5bd58f136a6252e073479b8/bin/release/.git-empty

--------------------------------------------------------------------------------

/helloworld.qbs:

--------------------------------------------------------------------------------

1 | import qbs

2 |

3 | Project {

4 | qbsSearchPaths: "/home/hans/projects/Software/qt-baremetal/project/qbs"

5 |

6 | references: [

7 | "project/prj.qbs"

8 | ]

9 | }

10 |

--------------------------------------------------------------------------------

/img/compiler.png:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/nlhans/qt-baremetal/c18a010c0cd4b711e5bd58f136a6252e073479b8/img/compiler.png

--------------------------------------------------------------------------------

/img/debugger.png:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/nlhans/qt-baremetal/c18a010c0cd4b711e5bd58f136a6252e073479b8/img/debugger.png

--------------------------------------------------------------------------------

/img/device.png:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/nlhans/qt-baremetal/c18a010c0cd4b711e5bd58f136a6252e073479b8/img/device.png

--------------------------------------------------------------------------------

/img/kit.png:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/nlhans/qt-baremetal/c18a010c0cd4b711e5bd58f136a6252e073479b8/img/kit.png

--------------------------------------------------------------------------------

/img/openocd-gdb.png:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/nlhans/qt-baremetal/c18a010c0cd4b711e5bd58f136a6252e073479b8/img/openocd-gdb.png

--------------------------------------------------------------------------------

/img/plugin.png:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/nlhans/qt-baremetal/c18a010c0cd4b711e5bd58f136a6252e073479b8/img/plugin.png

--------------------------------------------------------------------------------

/lib/STM32F4xx/Include/arm_common_tables.h:

--------------------------------------------------------------------------------

1 | /* ----------------------------------------------------------------------

2 | * Copyright (C) 2010-2014 ARM Limited. All rights reserved.

3 | *

4 | * $Date: 31. July 2014

5 | * $Revision: V1.4.4

6 | *

7 | * Project: CMSIS DSP Library

8 | * Title: arm_common_tables.h

9 | *

10 | * Description: This file has extern declaration for common tables like Bitreverse, reciprocal etc which are used across different functions

11 | *

12 | * Target Processor: Cortex-M4/Cortex-M3

13 | *

14 | * Redistribution and use in source and binary forms, with or without

15 | * modification, are permitted provided that the following conditions

16 | * are met:

17 | * - Redistributions of source code must retain the above copyright

18 | * notice, this list of conditions and the following disclaimer.

19 | * - Redistributions in binary form must reproduce the above copyright

20 | * notice, this list of conditions and the following disclaimer in

21 | * the documentation and/or other materials provided with the

22 | * distribution.

23 | * - Neither the name of ARM LIMITED nor the names of its contributors

24 | * may be used to endorse or promote products derived from this

25 | * software without specific prior written permission.

26 | *

27 | * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

28 | * "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

29 | * LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS

30 | * FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE

31 | * COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT,

32 | * INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING,

33 | * BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES;

34 | * LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER

35 | * CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT

36 | * LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN

37 | * ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE

38 | * POSSIBILITY OF SUCH DAMAGE.

39 | * -------------------------------------------------------------------- */

40 |

41 | #ifndef _ARM_COMMON_TABLES_H

42 | #define _ARM_COMMON_TABLES_H

43 |

44 | #include "arm_math.h"

45 |

46 | extern const uint16_t armBitRevTable[1024];

47 | extern const q15_t armRecipTableQ15[64];

48 | extern const q31_t armRecipTableQ31[64];

49 | //extern const q31_t realCoefAQ31[1024];

50 | //extern const q31_t realCoefBQ31[1024];

51 | extern const float32_t twiddleCoef_16[32];

52 | extern const float32_t twiddleCoef_32[64];

53 | extern const float32_t twiddleCoef_64[128];

54 | extern const float32_t twiddleCoef_128[256];

55 | extern const float32_t twiddleCoef_256[512];

56 | extern const float32_t twiddleCoef_512[1024];

57 | extern const float32_t twiddleCoef_1024[2048];

58 | extern const float32_t twiddleCoef_2048[4096];

59 | extern const float32_t twiddleCoef_4096[8192];

60 | #define twiddleCoef twiddleCoef_4096

61 | extern const q31_t twiddleCoef_16_q31[24];

62 | extern const q31_t twiddleCoef_32_q31[48];

63 | extern const q31_t twiddleCoef_64_q31[96];

64 | extern const q31_t twiddleCoef_128_q31[192];

65 | extern const q31_t twiddleCoef_256_q31[384];

66 | extern const q31_t twiddleCoef_512_q31[768];

67 | extern const q31_t twiddleCoef_1024_q31[1536];

68 | extern const q31_t twiddleCoef_2048_q31[3072];

69 | extern const q31_t twiddleCoef_4096_q31[6144];

70 | extern const q15_t twiddleCoef_16_q15[24];

71 | extern const q15_t twiddleCoef_32_q15[48];

72 | extern const q15_t twiddleCoef_64_q15[96];

73 | extern const q15_t twiddleCoef_128_q15[192];

74 | extern const q15_t twiddleCoef_256_q15[384];

75 | extern const q15_t twiddleCoef_512_q15[768];

76 | extern const q15_t twiddleCoef_1024_q15[1536];

77 | extern const q15_t twiddleCoef_2048_q15[3072];

78 | extern const q15_t twiddleCoef_4096_q15[6144];

79 | extern const float32_t twiddleCoef_rfft_32[32];

80 | extern const float32_t twiddleCoef_rfft_64[64];

81 | extern const float32_t twiddleCoef_rfft_128[128];

82 | extern const float32_t twiddleCoef_rfft_256[256];

83 | extern const float32_t twiddleCoef_rfft_512[512];

84 | extern const float32_t twiddleCoef_rfft_1024[1024];

85 | extern const float32_t twiddleCoef_rfft_2048[2048];

86 | extern const float32_t twiddleCoef_rfft_4096[4096];

87 |

88 |

89 | /* floating-point bit reversal tables */

90 | #define ARMBITREVINDEXTABLE__16_TABLE_LENGTH ((uint16_t)20 )

91 | #define ARMBITREVINDEXTABLE__32_TABLE_LENGTH ((uint16_t)48 )

92 | #define ARMBITREVINDEXTABLE__64_TABLE_LENGTH ((uint16_t)56 )

93 | #define ARMBITREVINDEXTABLE_128_TABLE_LENGTH ((uint16_t)208 )

94 | #define ARMBITREVINDEXTABLE_256_TABLE_LENGTH ((uint16_t)440 )

95 | #define ARMBITREVINDEXTABLE_512_TABLE_LENGTH ((uint16_t)448 )

96 | #define ARMBITREVINDEXTABLE1024_TABLE_LENGTH ((uint16_t)1800)

97 | #define ARMBITREVINDEXTABLE2048_TABLE_LENGTH ((uint16_t)3808)

98 | #define ARMBITREVINDEXTABLE4096_TABLE_LENGTH ((uint16_t)4032)

99 |

100 | extern const uint16_t armBitRevIndexTable16[ARMBITREVINDEXTABLE__16_TABLE_LENGTH];

101 | extern const uint16_t armBitRevIndexTable32[ARMBITREVINDEXTABLE__32_TABLE_LENGTH];

102 | extern const uint16_t armBitRevIndexTable64[ARMBITREVINDEXTABLE__64_TABLE_LENGTH];

103 | extern const uint16_t armBitRevIndexTable128[ARMBITREVINDEXTABLE_128_TABLE_LENGTH];

104 | extern const uint16_t armBitRevIndexTable256[ARMBITREVINDEXTABLE_256_TABLE_LENGTH];

105 | extern const uint16_t armBitRevIndexTable512[ARMBITREVINDEXTABLE_512_TABLE_LENGTH];

106 | extern const uint16_t armBitRevIndexTable1024[ARMBITREVINDEXTABLE1024_TABLE_LENGTH];

107 | extern const uint16_t armBitRevIndexTable2048[ARMBITREVINDEXTABLE2048_TABLE_LENGTH];

108 | extern const uint16_t armBitRevIndexTable4096[ARMBITREVINDEXTABLE4096_TABLE_LENGTH];

109 |

110 | /* fixed-point bit reversal tables */

111 | #define ARMBITREVINDEXTABLE_FIXED___16_TABLE_LENGTH ((uint16_t)12 )

112 | #define ARMBITREVINDEXTABLE_FIXED___32_TABLE_LENGTH ((uint16_t)24 )

113 | #define ARMBITREVINDEXTABLE_FIXED___64_TABLE_LENGTH ((uint16_t)56 )

114 | #define ARMBITREVINDEXTABLE_FIXED__128_TABLE_LENGTH ((uint16_t)112 )

115 | #define ARMBITREVINDEXTABLE_FIXED__256_TABLE_LENGTH ((uint16_t)240 )

116 | #define ARMBITREVINDEXTABLE_FIXED__512_TABLE_LENGTH ((uint16_t)480 )

117 | #define ARMBITREVINDEXTABLE_FIXED_1024_TABLE_LENGTH ((uint16_t)992 )

118 | #define ARMBITREVINDEXTABLE_FIXED_2048_TABLE_LENGTH ((uint16_t)1984)

119 | #define ARMBITREVINDEXTABLE_FIXED_4096_TABLE_LENGTH ((uint16_t)4032)

120 |

121 | extern const uint16_t armBitRevIndexTable_fixed_16[ARMBITREVINDEXTABLE_FIXED___16_TABLE_LENGTH];

122 | extern const uint16_t armBitRevIndexTable_fixed_32[ARMBITREVINDEXTABLE_FIXED___32_TABLE_LENGTH];

123 | extern const uint16_t armBitRevIndexTable_fixed_64[ARMBITREVINDEXTABLE_FIXED___64_TABLE_LENGTH];

124 | extern const uint16_t armBitRevIndexTable_fixed_128[ARMBITREVINDEXTABLE_FIXED__128_TABLE_LENGTH];

125 | extern const uint16_t armBitRevIndexTable_fixed_256[ARMBITREVINDEXTABLE_FIXED__256_TABLE_LENGTH];

126 | extern const uint16_t armBitRevIndexTable_fixed_512[ARMBITREVINDEXTABLE_FIXED__512_TABLE_LENGTH];

127 | extern const uint16_t armBitRevIndexTable_fixed_1024[ARMBITREVINDEXTABLE_FIXED_1024_TABLE_LENGTH];

128 | extern const uint16_t armBitRevIndexTable_fixed_2048[ARMBITREVINDEXTABLE_FIXED_2048_TABLE_LENGTH];

129 | extern const uint16_t armBitRevIndexTable_fixed_4096[ARMBITREVINDEXTABLE_FIXED_4096_TABLE_LENGTH];

130 |

131 | /* Tables for Fast Math Sine and Cosine */

132 | extern const float32_t sinTable_f32[FAST_MATH_TABLE_SIZE + 1];

133 | extern const q31_t sinTable_q31[FAST_MATH_TABLE_SIZE + 1];

134 | extern const q15_t sinTable_q15[FAST_MATH_TABLE_SIZE + 1];

135 |

136 | #endif /* ARM_COMMON_TABLES_H */

137 |

--------------------------------------------------------------------------------

/lib/STM32F4xx/Include/arm_const_structs.h:

--------------------------------------------------------------------------------

1 | /* ----------------------------------------------------------------------

2 | * Copyright (C) 2010-2014 ARM Limited. All rights reserved.

3 | *

4 | * $Date: 31. July 2014

5 | * $Revision: V1.4.4

6 | *

7 | * Project: CMSIS DSP Library

8 | * Title: arm_const_structs.h

9 | *

10 | * Description: This file has constant structs that are initialized for

11 | * user convenience. For example, some can be given as

12 | * arguments to the arm_cfft_f32() function.

13 | *

14 | * Target Processor: Cortex-M4/Cortex-M3

15 | *

16 | * Redistribution and use in source and binary forms, with or without

17 | * modification, are permitted provided that the following conditions

18 | * are met:

19 | * - Redistributions of source code must retain the above copyright

20 | * notice, this list of conditions and the following disclaimer.

21 | * - Redistributions in binary form must reproduce the above copyright

22 | * notice, this list of conditions and the following disclaimer in

23 | * the documentation and/or other materials provided with the

24 | * distribution.

25 | * - Neither the name of ARM LIMITED nor the names of its contributors

26 | * may be used to endorse or promote products derived from this

27 | * software without specific prior written permission.

28 | *

29 | * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

30 | * "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

31 | * LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS

32 | * FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE

33 | * COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT,

34 | * INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING,

35 | * BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES;

36 | * LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER

37 | * CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT

38 | * LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN

39 | * ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE

40 | * POSSIBILITY OF SUCH DAMAGE.

41 | * -------------------------------------------------------------------- */

42 |

43 | #ifndef _ARM_CONST_STRUCTS_H

44 | #define _ARM_CONST_STRUCTS_H

45 |

46 | #include "arm_math.h"

47 | #include "arm_common_tables.h"

48 |

49 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len16;

50 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len32;

51 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len64;

52 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len128;

53 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len256;

54 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len512;

55 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len1024;

56 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len2048;

57 | extern const arm_cfft_instance_f32 arm_cfft_sR_f32_len4096;

58 |

59 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len16;

60 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len32;

61 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len64;

62 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len128;

63 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len256;

64 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len512;

65 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len1024;

66 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len2048;

67 | extern const arm_cfft_instance_q31 arm_cfft_sR_q31_len4096;

68 |

69 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len16;

70 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len32;

71 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len64;

72 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len128;

73 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len256;

74 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len512;

75 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len1024;

76 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len2048;

77 | extern const arm_cfft_instance_q15 arm_cfft_sR_q15_len4096;

78 |

79 | #endif

80 |

--------------------------------------------------------------------------------

/lib/STM32F4xx/STM32F4xx_StdPeriph_Driver/Release_Notes.html:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/nlhans/qt-baremetal/c18a010c0cd4b711e5bd58f136a6252e073479b8/lib/STM32F4xx/STM32F4xx_StdPeriph_Driver/Release_Notes.html

--------------------------------------------------------------------------------

/lib/STM32F4xx/STM32F4xx_StdPeriph_Driver/inc/misc.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file misc.h

4 | * @author MCD Application Team

5 | * @version V1.6.1

6 | * @date 21-October-2015

7 | * @brief This file contains all the functions prototypes for the miscellaneous

8 | * firmware library functions (add-on to CMSIS functions).

9 | ******************************************************************************

10 | * @attention

11 | *

12 | * © COPYRIGHT 2015 STMicroelectronics

13 | *

14 | * Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

15 | * You may not use this file except in compliance with the License.

16 | * You may obtain a copy of the License at:

17 | *

18 | * http://www.st.com/software_license_agreement_liberty_v2

19 | *

20 | * Unless required by applicable law or agreed to in writing, software

21 | * distributed under the License is distributed on an "AS IS" BASIS,

22 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

23 | * See the License for the specific language governing permissions and

24 | * limitations under the License.

25 | *

26 | ******************************************************************************

27 | */

28 |

29 | /* Define to prevent recursive inclusion -------------------------------------*/

30 | #ifndef __MISC_H

31 | #define __MISC_H

32 |

33 | #ifdef __cplusplus

34 | extern "C" {

35 | #endif

36 |

37 | /* Includes ------------------------------------------------------------------*/

38 | #include "stm32f4xx.h"

39 |

40 | /** @addtogroup STM32F4xx_StdPeriph_Driver

41 | * @{

42 | */

43 |

44 | /** @addtogroup MISC

45 | * @{

46 | */

47 |

48 | /* Exported types ------------------------------------------------------------*/

49 |

50 | /**

51 | * @brief NVIC Init Structure definition

52 | */

53 |

54 | typedef struct

55 | {

56 | uint8_t NVIC_IRQChannel; /*!< Specifies the IRQ channel to be enabled or disabled.

57 | This parameter can be an enumerator of @ref IRQn_Type

58 | enumeration (For the complete STM32 Devices IRQ Channels

59 | list, please refer to stm32f4xx.h file) */

60 |

61 | uint8_t NVIC_IRQChannelPreemptionPriority; /*!< Specifies the pre-emption priority for the IRQ channel

62 | specified in NVIC_IRQChannel. This parameter can be a value

63 | between 0 and 15 as described in the table @ref MISC_NVIC_Priority_Table

64 | A lower priority value indicates a higher priority */

65 |

66 | uint8_t NVIC_IRQChannelSubPriority; /*!< Specifies the subpriority level for the IRQ channel specified

67 | in NVIC_IRQChannel. This parameter can be a value

68 | between 0 and 15 as described in the table @ref MISC_NVIC_Priority_Table

69 | A lower priority value indicates a higher priority */

70 |

71 | FunctionalState NVIC_IRQChannelCmd; /*!< Specifies whether the IRQ channel defined in NVIC_IRQChannel

72 | will be enabled or disabled.

73 | This parameter can be set either to ENABLE or DISABLE */

74 | } NVIC_InitTypeDef;

75 |

76 | /* Exported constants --------------------------------------------------------*/

77 |

78 | /** @defgroup MISC_Exported_Constants

79 | * @{

80 | */

81 |

82 | /** @defgroup MISC_Vector_Table_Base

83 | * @{

84 | */

85 |

86 | #define NVIC_VectTab_RAM ((uint32_t)0x20000000)

87 | #define NVIC_VectTab_FLASH ((uint32_t)0x08000000)

88 | #define IS_NVIC_VECTTAB(VECTTAB) (((VECTTAB) == NVIC_VectTab_RAM) || \

89 | ((VECTTAB) == NVIC_VectTab_FLASH))

90 | /**

91 | * @}

92 | */

93 |

94 | /** @defgroup MISC_System_Low_Power

95 | * @{

96 | */

97 |

98 | #define NVIC_LP_SEVONPEND ((uint8_t)0x10)

99 | #define NVIC_LP_SLEEPDEEP ((uint8_t)0x04)

100 | #define NVIC_LP_SLEEPONEXIT ((uint8_t)0x02)

101 | #define IS_NVIC_LP(LP) (((LP) == NVIC_LP_SEVONPEND) || \

102 | ((LP) == NVIC_LP_SLEEPDEEP) || \

103 | ((LP) == NVIC_LP_SLEEPONEXIT))

104 | /**

105 | * @}

106 | */

107 |

108 | /** @defgroup MISC_Preemption_Priority_Group

109 | * @{

110 | */

111 |

112 | #define NVIC_PriorityGroup_0 ((uint32_t)0x700) /*!< 0 bits for pre-emption priority

113 | 4 bits for subpriority */

114 | #define NVIC_PriorityGroup_1 ((uint32_t)0x600) /*!< 1 bits for pre-emption priority

115 | 3 bits for subpriority */

116 | #define NVIC_PriorityGroup_2 ((uint32_t)0x500) /*!< 2 bits for pre-emption priority

117 | 2 bits for subpriority */

118 | #define NVIC_PriorityGroup_3 ((uint32_t)0x400) /*!< 3 bits for pre-emption priority

119 | 1 bits for subpriority */

120 | #define NVIC_PriorityGroup_4 ((uint32_t)0x300) /*!< 4 bits for pre-emption priority

121 | 0 bits for subpriority */

122 |

123 | #define IS_NVIC_PRIORITY_GROUP(GROUP) (((GROUP) == NVIC_PriorityGroup_0) || \

124 | ((GROUP) == NVIC_PriorityGroup_1) || \

125 | ((GROUP) == NVIC_PriorityGroup_2) || \

126 | ((GROUP) == NVIC_PriorityGroup_3) || \

127 | ((GROUP) == NVIC_PriorityGroup_4))

128 |

129 | #define IS_NVIC_PREEMPTION_PRIORITY(PRIORITY) ((PRIORITY) < 0x10)

130 |

131 | #define IS_NVIC_SUB_PRIORITY(PRIORITY) ((PRIORITY) < 0x10)

132 |

133 | #define IS_NVIC_OFFSET(OFFSET) ((OFFSET) < 0x000FFFFF)

134 |

135 | /**

136 | * @}

137 | */

138 |

139 | /** @defgroup MISC_SysTick_clock_source

140 | * @{

141 | */

142 |

143 | #define SysTick_CLKSource_HCLK_Div8 ((uint32_t)0xFFFFFFFB)

144 | #define SysTick_CLKSource_HCLK ((uint32_t)0x00000004)

145 | #define IS_SYSTICK_CLK_SOURCE(SOURCE) (((SOURCE) == SysTick_CLKSource_HCLK) || \

146 | ((SOURCE) == SysTick_CLKSource_HCLK_Div8))

147 | /**

148 | * @}

149 | */

150 |

151 | /**

152 | * @}

153 | */

154 |

155 | /* Exported macro ------------------------------------------------------------*/

156 | /* Exported functions --------------------------------------------------------*/

157 |

158 | void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup);

159 | void NVIC_Init(NVIC_InitTypeDef* NVIC_InitStruct);

160 | void NVIC_SetVectorTable(uint32_t NVIC_VectTab, uint32_t Offset);

161 | void NVIC_SystemLPConfig(uint8_t LowPowerMode, FunctionalState NewState);

162 | void SysTick_CLKSourceConfig(uint32_t SysTick_CLKSource);

163 |

164 | #ifdef __cplusplus

165 | }

166 | #endif

167 |

168 | #endif /* __MISC_H */

169 |

170 | /**

171 | * @}

172 | */

173 |

174 | /**

175 | * @}

176 | */

177 |

178 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

179 |

--------------------------------------------------------------------------------

/lib/STM32F4xx/STM32F4xx_StdPeriph_Driver/inc/stm32f4xx_crc.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file stm32f4xx_crc.h

4 | * @author MCD Application Team

5 | * @version V1.6.1

6 | * @date 21-October-2015

7 | * @brief This file contains all the functions prototypes for the CRC firmware

8 | * library.

9 | ******************************************************************************

10 | * @attention

11 | *

12 | * © COPYRIGHT 2015 STMicroelectronics

13 | *

14 | * Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

15 | * You may not use this file except in compliance with the License.

16 | * You may obtain a copy of the License at:

17 | *

18 | * http://www.st.com/software_license_agreement_liberty_v2

19 | *

20 | * Unless required by applicable law or agreed to in writing, software

21 | * distributed under the License is distributed on an "AS IS" BASIS,

22 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

23 | * See the License for the specific language governing permissions and

24 | * limitations under the License.

25 | *

26 | ******************************************************************************

27 | */

28 |

29 | /* Define to prevent recursive inclusion -------------------------------------*/

30 | #ifndef __STM32F4xx_CRC_H

31 | #define __STM32F4xx_CRC_H

32 |

33 | #ifdef __cplusplus

34 | extern "C" {

35 | #endif

36 |

37 | /* Includes ------------------------------------------------------------------*/

38 | #include "stm32f4xx.h"

39 |

40 | /** @addtogroup STM32F4xx_StdPeriph_Driver

41 | * @{

42 | */

43 |

44 | /** @addtogroup CRC

45 | * @{

46 | */

47 |

48 | /* Exported types ------------------------------------------------------------*/

49 | /* Exported constants --------------------------------------------------------*/

50 |

51 | /** @defgroup CRC_Exported_Constants

52 | * @{

53 | */

54 |

55 | /**

56 | * @}

57 | */

58 |

59 | /* Exported macro ------------------------------------------------------------*/

60 | /* Exported functions --------------------------------------------------------*/

61 |

62 | void CRC_ResetDR(void);

63 | uint32_t CRC_CalcCRC(uint32_t Data);

64 | uint32_t CRC_CalcBlockCRC(uint32_t pBuffer[], uint32_t BufferLength);

65 | uint32_t CRC_GetCRC(void);

66 | void CRC_SetIDRegister(uint8_t IDValue);

67 | uint8_t CRC_GetIDRegister(void);

68 |

69 | #ifdef __cplusplus

70 | }

71 | #endif

72 |

73 | #endif /* __STM32F4xx_CRC_H */

74 |

75 | /**

76 | * @}

77 | */

78 |

79 | /**

80 | * @}

81 | */

82 |

83 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

84 |

--------------------------------------------------------------------------------

/lib/STM32F4xx/STM32F4xx_StdPeriph_Driver/inc/stm32f4xx_dbgmcu.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file stm32f4xx_dbgmcu.h

4 | * @author MCD Application Team

5 | * @version V1.6.1

6 | * @date 21-October-2015

7 | * @brief This file contains all the functions prototypes for the DBGMCU firmware library.

8 | ******************************************************************************

9 | * @attention

10 | *

11 | * © COPYRIGHT 2015 STMicroelectronics

12 | *

13 | * Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

14 | * You may not use this file except in compliance with the License.

15 | * You may obtain a copy of the License at:

16 | *

17 | * http://www.st.com/software_license_agreement_liberty_v2

18 | *

19 | * Unless required by applicable law or agreed to in writing, software

20 | * distributed under the License is distributed on an "AS IS" BASIS,

21 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

22 | * See the License for the specific language governing permissions and

23 | * limitations under the License.

24 | *

25 | ******************************************************************************

26 | */

27 |

28 | /* Define to prevent recursive inclusion -------------------------------------*/

29 | #ifndef __STM32F4xx_DBGMCU_H

30 | #define __STM32F4xx_DBGMCU_H

31 |

32 | #ifdef __cplusplus

33 | extern "C" {

34 | #endif

35 |

36 | /* Includes ------------------------------------------------------------------*/

37 | #include "stm32f4xx.h"

38 |

39 | /** @addtogroup STM32F4xx_StdPeriph_Driver

40 | * @{

41 | */

42 |

43 | /** @addtogroup DBGMCU

44 | * @{

45 | */

46 |

47 | /* Exported types ------------------------------------------------------------*/

48 | /* Exported constants --------------------------------------------------------*/

49 |

50 | /** @defgroup DBGMCU_Exported_Constants

51 | * @{

52 | */

53 | #define DBGMCU_SLEEP ((uint32_t)0x00000001)

54 | #define DBGMCU_STOP ((uint32_t)0x00000002)

55 | #define DBGMCU_STANDBY ((uint32_t)0x00000004)

56 | #define IS_DBGMCU_PERIPH(PERIPH) ((((PERIPH) & 0xFFFFFFF8) == 0x00) && ((PERIPH) != 0x00))

57 |

58 | #define DBGMCU_TIM2_STOP ((uint32_t)0x00000001)

59 | #define DBGMCU_TIM3_STOP ((uint32_t)0x00000002)

60 | #define DBGMCU_TIM4_STOP ((uint32_t)0x00000004)

61 | #define DBGMCU_TIM5_STOP ((uint32_t)0x00000008)

62 | #define DBGMCU_TIM6_STOP ((uint32_t)0x00000010)

63 | #define DBGMCU_TIM7_STOP ((uint32_t)0x00000020)

64 | #define DBGMCU_TIM12_STOP ((uint32_t)0x00000040)

65 | #define DBGMCU_TIM13_STOP ((uint32_t)0x00000080)

66 | #define DBGMCU_TIM14_STOP ((uint32_t)0x00000100)

67 | #define DBGMCU_RTC_STOP ((uint32_t)0x00000400)

68 | #define DBGMCU_WWDG_STOP ((uint32_t)0x00000800)

69 | #define DBGMCU_IWDG_STOP ((uint32_t)0x00001000)

70 | #define DBGMCU_I2C1_SMBUS_TIMEOUT ((uint32_t)0x00200000)

71 | #define DBGMCU_I2C2_SMBUS_TIMEOUT ((uint32_t)0x00400000)

72 | #define DBGMCU_I2C3_SMBUS_TIMEOUT ((uint32_t)0x00800000)

73 | #define DBGMCU_CAN1_STOP ((uint32_t)0x02000000)

74 | #define DBGMCU_CAN2_STOP ((uint32_t)0x04000000)

75 | #define IS_DBGMCU_APB1PERIPH(PERIPH) ((((PERIPH) & 0xF91FE200) == 0x00) && ((PERIPH) != 0x00))

76 |

77 | #define DBGMCU_TIM1_STOP ((uint32_t)0x00000001)

78 | #define DBGMCU_TIM8_STOP ((uint32_t)0x00000002)

79 | #define DBGMCU_TIM9_STOP ((uint32_t)0x00010000)

80 | #define DBGMCU_TIM10_STOP ((uint32_t)0x00020000)

81 | #define DBGMCU_TIM11_STOP ((uint32_t)0x00040000)

82 | #define IS_DBGMCU_APB2PERIPH(PERIPH) ((((PERIPH) & 0xFFF8FFFC) == 0x00) && ((PERIPH) != 0x00))

83 | /**

84 | * @}

85 | */

86 |

87 | /* Exported macro ------------------------------------------------------------*/

88 | /* Exported functions --------------------------------------------------------*/

89 | uint32_t DBGMCU_GetREVID(void);

90 | uint32_t DBGMCU_GetDEVID(void);

91 | void DBGMCU_Config(uint32_t DBGMCU_Periph, FunctionalState NewState);

92 | void DBGMCU_APB1PeriphConfig(uint32_t DBGMCU_Periph, FunctionalState NewState);

93 | void DBGMCU_APB2PeriphConfig(uint32_t DBGMCU_Periph, FunctionalState NewState);

94 |

95 | #ifdef __cplusplus

96 | }

97 | #endif

98 |

99 | #endif /* __STM32F4xx_DBGMCU_H */

100 |

101 | /**

102 | * @}

103 | */

104 |

105 | /**

106 | * @}

107 | */

108 |

109 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

110 |

--------------------------------------------------------------------------------

/lib/STM32F4xx/STM32F4xx_StdPeriph_Driver/inc/stm32f4xx_exti.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file stm32f4xx_exti.h

4 | * @author MCD Application Team

5 | * @version V1.6.1

6 | * @date 21-October-2015

7 | * @brief This file contains all the functions prototypes for the EXTI firmware

8 | * library.

9 | ******************************************************************************

10 | * @attention

11 | *

12 | * © COPYRIGHT 2015 STMicroelectronics

13 | *

14 | * Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

15 | * You may not use this file except in compliance with the License.

16 | * You may obtain a copy of the License at:

17 | *

18 | * http://www.st.com/software_license_agreement_liberty_v2

19 | *

20 | * Unless required by applicable law or agreed to in writing, software

21 | * distributed under the License is distributed on an "AS IS" BASIS,

22 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

23 | * See the License for the specific language governing permissions and

24 | * limitations under the License.

25 | *

26 | ******************************************************************************

27 | */

28 |

29 | /* Define to prevent recursive inclusion -------------------------------------*/

30 | #ifndef __STM32F4xx_EXTI_H

31 | #define __STM32F4xx_EXTI_H

32 |

33 | #ifdef __cplusplus

34 | extern "C" {

35 | #endif

36 |

37 | /* Includes ------------------------------------------------------------------*/

38 | #include "stm32f4xx.h"

39 |

40 | /** @addtogroup STM32F4xx_StdPeriph_Driver

41 | * @{

42 | */

43 |

44 | /** @addtogroup EXTI

45 | * @{

46 | */

47 |

48 | /* Exported types ------------------------------------------------------------*/

49 |

50 | /**

51 | * @brief EXTI mode enumeration

52 | */

53 |

54 | typedef enum

55 | {

56 | EXTI_Mode_Interrupt = 0x00,

57 | EXTI_Mode_Event = 0x04

58 | }EXTIMode_TypeDef;

59 |

60 | #define IS_EXTI_MODE(MODE) (((MODE) == EXTI_Mode_Interrupt) || ((MODE) == EXTI_Mode_Event))

61 |

62 | /**

63 | * @brief EXTI Trigger enumeration

64 | */

65 |

66 | typedef enum

67 | {

68 | EXTI_Trigger_Rising = 0x08,

69 | EXTI_Trigger_Falling = 0x0C,

70 | EXTI_Trigger_Rising_Falling = 0x10

71 | }EXTITrigger_TypeDef;

72 |

73 | #define IS_EXTI_TRIGGER(TRIGGER) (((TRIGGER) == EXTI_Trigger_Rising) || \

74 | ((TRIGGER) == EXTI_Trigger_Falling) || \

75 | ((TRIGGER) == EXTI_Trigger_Rising_Falling))

76 | /**

77 | * @brief EXTI Init Structure definition

78 | */

79 |

80 | typedef struct

81 | {

82 | uint32_t EXTI_Line; /*!< Specifies the EXTI lines to be enabled or disabled.

83 | This parameter can be any combination value of @ref EXTI_Lines */

84 |

85 | EXTIMode_TypeDef EXTI_Mode; /*!< Specifies the mode for the EXTI lines.

86 | This parameter can be a value of @ref EXTIMode_TypeDef */

87 |

88 | EXTITrigger_TypeDef EXTI_Trigger; /*!< Specifies the trigger signal active edge for the EXTI lines.

89 | This parameter can be a value of @ref EXTITrigger_TypeDef */

90 |

91 | FunctionalState EXTI_LineCmd; /*!< Specifies the new state of the selected EXTI lines.

92 | This parameter can be set either to ENABLE or DISABLE */

93 | }EXTI_InitTypeDef;

94 |

95 | /* Exported constants --------------------------------------------------------*/

96 |

97 | /** @defgroup EXTI_Exported_Constants

98 | * @{

99 | */

100 |

101 | /** @defgroup EXTI_Lines

102 | * @{

103 | */

104 |

105 | #define EXTI_Line0 ((uint32_t)0x00001) /*!< External interrupt line 0 */

106 | #define EXTI_Line1 ((uint32_t)0x00002) /*!< External interrupt line 1 */

107 | #define EXTI_Line2 ((uint32_t)0x00004) /*!< External interrupt line 2 */

108 | #define EXTI_Line3 ((uint32_t)0x00008) /*!< External interrupt line 3 */

109 | #define EXTI_Line4 ((uint32_t)0x00010) /*!< External interrupt line 4 */

110 | #define EXTI_Line5 ((uint32_t)0x00020) /*!< External interrupt line 5 */

111 | #define EXTI_Line6 ((uint32_t)0x00040) /*!< External interrupt line 6 */

112 | #define EXTI_Line7 ((uint32_t)0x00080) /*!< External interrupt line 7 */

113 | #define EXTI_Line8 ((uint32_t)0x00100) /*!< External interrupt line 8 */

114 | #define EXTI_Line9 ((uint32_t)0x00200) /*!< External interrupt line 9 */

115 | #define EXTI_Line10 ((uint32_t)0x00400) /*!< External interrupt line 10 */

116 | #define EXTI_Line11 ((uint32_t)0x00800) /*!< External interrupt line 11 */

117 | #define EXTI_Line12 ((uint32_t)0x01000) /*!< External interrupt line 12 */

118 | #define EXTI_Line13 ((uint32_t)0x02000) /*!< External interrupt line 13 */

119 | #define EXTI_Line14 ((uint32_t)0x04000) /*!< External interrupt line 14 */

120 | #define EXTI_Line15 ((uint32_t)0x08000) /*!< External interrupt line 15 */

121 | #define EXTI_Line16 ((uint32_t)0x10000) /*!< External interrupt line 16 Connected to the PVD Output */

122 | #define EXTI_Line17 ((uint32_t)0x20000) /*!< External interrupt line 17 Connected to the RTC Alarm event */

123 | #define EXTI_Line18 ((uint32_t)0x40000) /*!< External interrupt line 18 Connected to the USB OTG FS Wakeup from suspend event */

124 | #define EXTI_Line19 ((uint32_t)0x80000) /*!< External interrupt line 19 Connected to the Ethernet Wakeup event */

125 | #define EXTI_Line20 ((uint32_t)0x00100000) /*!< External interrupt line 20 Connected to the USB OTG HS (configured in FS) Wakeup event */

126 | #define EXTI_Line21 ((uint32_t)0x00200000) /*!< External interrupt line 21 Connected to the RTC Tamper and Time Stamp events */

127 | #define EXTI_Line22 ((uint32_t)0x00400000) /*!< External interrupt line 22 Connected to the RTC Wakeup event */

128 | #define EXTI_Line23 ((uint32_t)0x00800000) /*!< External interrupt line 23 Connected to the LPTIM Wakeup event */

129 |

130 |

131 | #define IS_EXTI_LINE(LINE) ((((LINE) & (uint32_t)0xFF800000) == 0x00) && ((LINE) != (uint16_t)0x00))

132 |

133 | #define IS_GET_EXTI_LINE(LINE) (((LINE) == EXTI_Line0) || ((LINE) == EXTI_Line1) || \

134 | ((LINE) == EXTI_Line2) || ((LINE) == EXTI_Line3) || \

135 | ((LINE) == EXTI_Line4) || ((LINE) == EXTI_Line5) || \

136 | ((LINE) == EXTI_Line6) || ((LINE) == EXTI_Line7) || \

137 | ((LINE) == EXTI_Line8) || ((LINE) == EXTI_Line9) || \

138 | ((LINE) == EXTI_Line10) || ((LINE) == EXTI_Line11) || \

139 | ((LINE) == EXTI_Line12) || ((LINE) == EXTI_Line13) || \

140 | ((LINE) == EXTI_Line14) || ((LINE) == EXTI_Line15) || \

141 | ((LINE) == EXTI_Line16) || ((LINE) == EXTI_Line17) || \

142 | ((LINE) == EXTI_Line18) || ((LINE) == EXTI_Line19) || \

143 | ((LINE) == EXTI_Line20) || ((LINE) == EXTI_Line21) ||\

144 | ((LINE) == EXTI_Line22) || ((LINE) == EXTI_Line23))

145 |

146 | /**

147 | * @}

148 | */

149 |

150 | /**

151 | * @}

152 | */

153 |

154 | /* Exported macro ------------------------------------------------------------*/

155 | /* Exported functions --------------------------------------------------------*/

156 |

157 | /* Function used to set the EXTI configuration to the default reset state *****/

158 | void EXTI_DeInit(void);

159 |

160 | /* Initialization and Configuration functions *********************************/

161 | void EXTI_Init(EXTI_InitTypeDef* EXTI_InitStruct);

162 | void EXTI_StructInit(EXTI_InitTypeDef* EXTI_InitStruct);

163 | void EXTI_GenerateSWInterrupt(uint32_t EXTI_Line);

164 |

165 | /* Interrupts and flags management functions **********************************/

166 | FlagStatus EXTI_GetFlagStatus(uint32_t EXTI_Line);

167 | void EXTI_ClearFlag(uint32_t EXTI_Line);

168 | ITStatus EXTI_GetITStatus(uint32_t EXTI_Line);

169 | void EXTI_ClearITPendingBit(uint32_t EXTI_Line);

170 |

171 | #ifdef __cplusplus

172 | }

173 | #endif

174 |

175 | #endif /* __STM32F4xx_EXTI_H */

176 |

177 | /**

178 | * @}

179 | */

180 |

181 | /**

182 | * @}

183 | */

184 |

185 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

186 |

--------------------------------------------------------------------------------

/lib/STM32F4xx/STM32F4xx_StdPeriph_Driver/inc/stm32f4xx_flash_ramfunc.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file stm32f4xx_flash_ramfunc.h

4 | * @author MCD Application Team

5 | * @version V1.6.1

6 | * @date 21-October-2015

7 | * @brief Header file of FLASH RAMFUNC driver.

8 | ******************************************************************************

9 | * @attention

10 | *

11 | * © COPYRIGHT 2015 STMicroelectronics

12 | *

13 | * Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

14 | * You may not use this file except in compliance with the License.

15 | * You may obtain a copy of the License at:

16 | *

17 | * http://www.st.com/software_license_agreement_liberty_v2

18 | *

19 | * Unless required by applicable law or agreed to in writing, software

20 | * distributed under the License is distributed on an "AS IS" BASIS,

21 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

22 | * See the License for the specific language governing permissions and

23 | * limitations under the License.

24 | *

25 | ******************************************************************************

26 | */

27 |

28 |

29 | /* Define to prevent recursive inclusion -------------------------------------*/

30 | #ifndef __STM32F4xx_FLASH_RAMFUNC_H

31 | #define __STM32F4xx_FLASH_RAMFUNC_H

32 |

33 | #ifdef __cplusplus

34 | extern "C" {

35 | #endif

36 |

37 | /* Includes ------------------------------------------------------------------*/

38 | #include "stm32f4xx.h"

39 |

40 | /** @addtogroup STM32F4xx_StdPeriph_Driver

41 | * @{

42 | */

43 |

44 | /** @addtogroup FLASH RAMFUNC

45 | * @{

46 | */

47 |

48 | /* Exported types ------------------------------------------------------------*/

49 | /* Private define ------------------------------------------------------------*/

50 | /**

51 | * @brief __RAM_FUNC definition

52 | */

53 | #if defined ( __CC_ARM )

54 | /* ARM Compiler

55 | ------------

56 | RAM functions are defined using the toolchain options.

57 | Functions that are executed in RAM should reside in a separate source module.

58 | Using the 'Options for File' dialog you can simply change the 'Code / Const'

59 | area of a module to a memory space in physical RAM.

60 | Available memory areas are declared in the 'Target' tab of the 'Options for Target'

61 | dialog.

62 | */

63 | #define __RAM_FUNC void

64 |

65 | #elif defined ( __ICCARM__ )

66 | /* ICCARM Compiler

67 | ---------------

68 | RAM functions are defined using a specific toolchain keyword "__ramfunc".

69 | */

70 | #define __RAM_FUNC __ramfunc void

71 |

72 | #elif defined ( __GNUC__ )

73 | /* GNU Compiler

74 | ------------

75 | RAM functions are defined using a specific toolchain attribute

76 | "__attribute__((section(".RamFunc")))".

77 | */

78 | #define __RAM_FUNC void __attribute__((section(".RamFunc")))

79 |

80 | #endif

81 | /* Exported constants --------------------------------------------------------*/

82 | /* Exported macro ------------------------------------------------------------*/

83 | /* Exported functions --------------------------------------------------------*/

84 | __RAM_FUNC FLASH_FlashInterfaceCmd(FunctionalState NewState);

85 | __RAM_FUNC FLASH_FlashSleepModeCmd(FunctionalState NewState);

86 |

87 |

88 | #ifdef __cplusplus

89 | }

90 | #endif

91 |

92 | #endif /* __STM32F4xx_FLASH_RAMFUNC_H */

93 |

94 | /**

95 | * @}

96 | */

97 |

98 | /**

99 | * @}

100 | */

101 |

102 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

103 |

104 |

--------------------------------------------------------------------------------

/lib/STM32F4xx/STM32F4xx_StdPeriph_Driver/inc/stm32f4xx_hash.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file stm32f4xx_hash.h

4 | * @author MCD Application Team

5 | * @version V1.6.1

6 | * @date 21-October-2015

7 | * @brief This file contains all the functions prototypes for the HASH

8 | * firmware library.

9 | ******************************************************************************

10 | * @attention

11 | *

12 | * © COPYRIGHT 2015 STMicroelectronics

13 | *

14 | * Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

15 | * You may not use this file except in compliance with the License.

16 | * You may obtain a copy of the License at:

17 | *

18 | * http://www.st.com/software_license_agreement_liberty_v2

19 | *

20 | * Unless required by applicable law or agreed to in writing, software

21 | * distributed under the License is distributed on an "AS IS" BASIS,

22 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

23 | * See the License for the specific language governing permissions and

24 | * limitations under the License.

25 | *

26 | ******************************************************************************

27 | */

28 |

29 | /* Define to prevent recursive inclusion -------------------------------------*/

30 | #ifndef __STM32F4xx_HASH_H

31 | #define __STM32F4xx_HASH_H

32 |

33 | #ifdef __cplusplus

34 | extern "C" {

35 | #endif

36 |

37 | /* Includes ------------------------------------------------------------------*/

38 | #include "stm32f4xx.h"

39 |

40 | /** @addtogroup STM32F4xx_StdPeriph_Driver

41 | * @{

42 | */

43 |

44 | /** @addtogroup HASH

45 | * @{

46 | */

47 |

48 | /* Exported types ------------------------------------------------------------*/

49 |

50 | /**

51 | * @brief HASH Init structure definition

52 | */

53 | typedef struct

54 | {

55 | uint32_t HASH_AlgoSelection; /*!< SHA-1, SHA-224, SHA-256 or MD5. This parameter

56 | can be a value of @ref HASH_Algo_Selection */

57 | uint32_t HASH_AlgoMode; /*!< HASH or HMAC. This parameter can be a value

58 | of @ref HASH_processor_Algorithm_Mode */

59 | uint32_t HASH_DataType; /*!< 32-bit data, 16-bit data, 8-bit data or

60 | bit string. This parameter can be a value of

61 | @ref HASH_Data_Type */

62 | uint32_t HASH_HMACKeyType; /*!< HMAC Short key or HMAC Long Key. This parameter

63 | can be a value of @ref HASH_HMAC_Long_key_only_for_HMAC_mode */

64 | }HASH_InitTypeDef;

65 |

66 | /**

67 | * @brief HASH message digest result structure definition

68 | */

69 | typedef struct

70 | {

71 | uint32_t Data[8]; /*!< Message digest result : 8x 32bit wors for SHA-256,

72 | 7x 32bit wors for SHA-224,

73 | 5x 32bit words for SHA-1 or

74 | 4x 32bit words for MD5 */

75 | } HASH_MsgDigest;

76 |

77 | /**

78 | * @brief HASH context swapping structure definition

79 | */

80 | typedef struct

81 | {

82 | uint32_t HASH_IMR;

83 | uint32_t HASH_STR;

84 | uint32_t HASH_CR;

85 | uint32_t HASH_CSR[54];

86 | }HASH_Context;

87 |

88 | /* Exported constants --------------------------------------------------------*/

89 |

90 | /** @defgroup HASH_Exported_Constants

91 | * @{

92 | */

93 |

94 | /** @defgroup HASH_Algo_Selection

95 | * @{

96 | */

97 | #define HASH_AlgoSelection_SHA1 ((uint32_t)0x0000) /*!< HASH function is SHA1 */

98 | #define HASH_AlgoSelection_SHA224 HASH_CR_ALGO_1 /*!< HASH function is SHA224 */

99 | #define HASH_AlgoSelection_SHA256 HASH_CR_ALGO /*!< HASH function is SHA256 */

100 | #define HASH_AlgoSelection_MD5 HASH_CR_ALGO_0 /*!< HASH function is MD5 */

101 |

102 | #define IS_HASH_ALGOSELECTION(ALGOSELECTION) (((ALGOSELECTION) == HASH_AlgoSelection_SHA1) || \

103 | ((ALGOSELECTION) == HASH_AlgoSelection_SHA224) || \

104 | ((ALGOSELECTION) == HASH_AlgoSelection_SHA256) || \

105 | ((ALGOSELECTION) == HASH_AlgoSelection_MD5))

106 | /**

107 | * @}

108 | */

109 |

110 | /** @defgroup HASH_processor_Algorithm_Mode

111 | * @{

112 | */

113 | #define HASH_AlgoMode_HASH ((uint32_t)0x00000000) /*!< Algorithm is HASH */

114 | #define HASH_AlgoMode_HMAC HASH_CR_MODE /*!< Algorithm is HMAC */

115 |

116 | #define IS_HASH_ALGOMODE(ALGOMODE) (((ALGOMODE) == HASH_AlgoMode_HASH) || \

117 | ((ALGOMODE) == HASH_AlgoMode_HMAC))

118 | /**

119 | * @}

120 | */

121 |

122 | /** @defgroup HASH_Data_Type

123 | * @{

124 | */

125 | #define HASH_DataType_32b ((uint32_t)0x0000) /*!< 32-bit data. No swapping */

126 | #define HASH_DataType_16b HASH_CR_DATATYPE_0 /*!< 16-bit data. Each half word is swapped */

127 | #define HASH_DataType_8b HASH_CR_DATATYPE_1 /*!< 8-bit data. All bytes are swapped */

128 | #define HASH_DataType_1b HASH_CR_DATATYPE /*!< 1-bit data. In the word all bits are swapped */

129 |

130 | #define IS_HASH_DATATYPE(DATATYPE) (((DATATYPE) == HASH_DataType_32b)|| \

131 | ((DATATYPE) == HASH_DataType_16b)|| \

132 | ((DATATYPE) == HASH_DataType_8b) || \

133 | ((DATATYPE) == HASH_DataType_1b))

134 | /**

135 | * @}

136 | */

137 |

138 | /** @defgroup HASH_HMAC_Long_key_only_for_HMAC_mode

139 | * @{

140 | */

141 | #define HASH_HMACKeyType_ShortKey ((uint32_t)0x00000000) /*!< HMAC Key is <= 64 bytes */

142 | #define HASH_HMACKeyType_LongKey HASH_CR_LKEY /*!< HMAC Key is > 64 bytes */

143 |

144 | #define IS_HASH_HMAC_KEYTYPE(KEYTYPE) (((KEYTYPE) == HASH_HMACKeyType_ShortKey) || \

145 | ((KEYTYPE) == HASH_HMACKeyType_LongKey))

146 | /**

147 | * @}

148 | */

149 |

150 | /** @defgroup Number_of_valid_bits_in_last_word_of_the_message

151 | * @{

152 | */

153 | #define IS_HASH_VALIDBITSNUMBER(VALIDBITS) ((VALIDBITS) <= 0x1F)

154 |

155 | /**

156 | * @}

157 | */

158 |

159 | /** @defgroup HASH_interrupts_definition

160 | * @{

161 | */

162 | #define HASH_IT_DINI HASH_IMR_DINIM /*!< A new block can be entered into the input buffer (DIN) */

163 | #define HASH_IT_DCI HASH_IMR_DCIM /*!< Digest calculation complete */

164 |

165 | #define IS_HASH_IT(IT) ((((IT) & (uint32_t)0xFFFFFFFC) == 0x00000000) && ((IT) != 0x00000000))

166 | #define IS_HASH_GET_IT(IT) (((IT) == HASH_IT_DINI) || ((IT) == HASH_IT_DCI))

167 |

168 | /**

169 | * @}

170 | */

171 |

172 | /** @defgroup HASH_flags_definition

173 | * @{

174 | */

175 | #define HASH_FLAG_DINIS HASH_SR_DINIS /*!< 16 locations are free in the DIN : A new block can be entered into the input buffer */

176 | #define HASH_FLAG_DCIS HASH_SR_DCIS /*!< Digest calculation complete */

177 | #define HASH_FLAG_DMAS HASH_SR_DMAS /*!< DMA interface is enabled (DMAE=1) or a transfer is ongoing */

178 | #define HASH_FLAG_BUSY HASH_SR_BUSY /*!< The hash core is Busy : processing a block of data */

179 | #define HASH_FLAG_DINNE HASH_CR_DINNE /*!< DIN not empty : The input buffer contains at least one word of data */

180 |

181 | #define IS_HASH_GET_FLAG(FLAG) (((FLAG) == HASH_FLAG_DINIS) || \

182 | ((FLAG) == HASH_FLAG_DCIS) || \

183 | ((FLAG) == HASH_FLAG_DMAS) || \

184 | ((FLAG) == HASH_FLAG_BUSY) || \

185 | ((FLAG) == HASH_FLAG_DINNE))

186 |

187 | #define IS_HASH_CLEAR_FLAG(FLAG)(((FLAG) == HASH_FLAG_DINIS) || \

188 | ((FLAG) == HASH_FLAG_DCIS))

189 |

190 | /**

191 | * @}

192 | */

193 |

194 | /**

195 | * @}

196 | */

197 |

198 | /* Exported macro ------------------------------------------------------------*/

199 | /* Exported functions --------------------------------------------------------*/

200 |

201 | /* Function used to set the HASH configuration to the default reset state ****/

202 | void HASH_DeInit(void);

203 |

204 | /* HASH Configuration function ************************************************/

205 | void HASH_Init(HASH_InitTypeDef* HASH_InitStruct);

206 | void HASH_StructInit(HASH_InitTypeDef* HASH_InitStruct);

207 | void HASH_Reset(void);

208 |

209 | /* HASH Message Digest generation functions ***********************************/

210 | void HASH_DataIn(uint32_t Data);

211 | uint8_t HASH_GetInFIFOWordsNbr(void);

212 | void HASH_SetLastWordValidBitsNbr(uint16_t ValidNumber);

213 | void HASH_StartDigest(void);

214 | void HASH_AutoStartDigest(FunctionalState NewState);

215 | void HASH_GetDigest(HASH_MsgDigest* HASH_MessageDigest);

216 |

217 | /* HASH Context swapping functions ********************************************/

218 | void HASH_SaveContext(HASH_Context* HASH_ContextSave);

219 | void HASH_RestoreContext(HASH_Context* HASH_ContextRestore);

220 |

221 | /* HASH DMA interface function ************************************************/

222 | void HASH_DMACmd(FunctionalState NewState);

223 |

224 | /* HASH Interrupts and flags management functions *****************************/

225 | void HASH_ITConfig(uint32_t HASH_IT, FunctionalState NewState);

226 | FlagStatus HASH_GetFlagStatus(uint32_t HASH_FLAG);

227 | void HASH_ClearFlag(uint32_t HASH_FLAG);

228 | ITStatus HASH_GetITStatus(uint32_t HASH_IT);

229 | void HASH_ClearITPendingBit(uint32_t HASH_IT);

230 |

231 | /* High Level SHA1 functions **************************************************/

232 | ErrorStatus HASH_SHA1(uint8_t *Input, uint32_t Ilen, uint8_t Output[20]);

233 | ErrorStatus HMAC_SHA1(uint8_t *Key, uint32_t Keylen,

234 | uint8_t *Input, uint32_t Ilen,

235 | uint8_t Output[20]);

236 |

237 | /* High Level MD5 functions ***************************************************/

238 | ErrorStatus HASH_MD5(uint8_t *Input, uint32_t Ilen, uint8_t Output[16]);

239 | ErrorStatus HMAC_MD5(uint8_t *Key, uint32_t Keylen,

240 | uint8_t *Input, uint32_t Ilen,

241 | uint8_t Output[16]);

242 |

243 | #ifdef __cplusplus

244 | }

245 | #endif

246 |

247 | #endif /*__STM32F4xx_HASH_H */

248 |

249 | /**

250 | * @}

251 | */

252 |

253 | /**

254 | * @}

255 | */

256 |

257 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

258 |

--------------------------------------------------------------------------------

/lib/STM32F4xx/STM32F4xx_StdPeriph_Driver/inc/stm32f4xx_iwdg.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file stm32f4xx_iwdg.h

4 | * @author MCD Application Team

5 | * @version V1.6.1

6 | * @date 21-October-2015

7 | * @brief This file contains all the functions prototypes for the IWDG

8 | * firmware library.

9 | ******************************************************************************

10 | * @attention

11 | *

12 | * © COPYRIGHT 2015 STMicroelectronics

13 | *

14 | * Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

15 | * You may not use this file except in compliance with the License.

16 | * You may obtain a copy of the License at:

17 | *

18 | * http://www.st.com/software_license_agreement_liberty_v2

19 | *

20 | * Unless required by applicable law or agreed to in writing, software

21 | * distributed under the License is distributed on an "AS IS" BASIS,

22 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

23 | * See the License for the specific language governing permissions and

24 | * limitations under the License.

25 | *

26 | ******************************************************************************

27 | */

28 |

29 | /* Define to prevent recursive inclusion -------------------------------------*/

30 | #ifndef __STM32F4xx_IWDG_H

31 | #define __STM32F4xx_IWDG_H

32 |

33 | #ifdef __cplusplus

34 | extern "C" {

35 | #endif

36 |

37 | /* Includes ------------------------------------------------------------------*/

38 | #include "stm32f4xx.h"

39 |

40 | /** @addtogroup STM32F4xx_StdPeriph_Driver

41 | * @{

42 | */

43 |

44 | /** @addtogroup IWDG

45 | * @{

46 | */

47 |

48 | /* Exported types ------------------------------------------------------------*/

49 | /* Exported constants --------------------------------------------------------*/

50 |

51 | /** @defgroup IWDG_Exported_Constants

52 | * @{

53 | */

54 |

55 | /** @defgroup IWDG_WriteAccess

56 | * @{

57 | */

58 | #define IWDG_WriteAccess_Enable ((uint16_t)0x5555)

59 | #define IWDG_WriteAccess_Disable ((uint16_t)0x0000)

60 | #define IS_IWDG_WRITE_ACCESS(ACCESS) (((ACCESS) == IWDG_WriteAccess_Enable) || \

61 | ((ACCESS) == IWDG_WriteAccess_Disable))

62 | /**

63 | * @}

64 | */

65 |

66 | /** @defgroup IWDG_prescaler

67 | * @{

68 | */

69 | #define IWDG_Prescaler_4 ((uint8_t)0x00)

70 | #define IWDG_Prescaler_8 ((uint8_t)0x01)

71 | #define IWDG_Prescaler_16 ((uint8_t)0x02)

72 | #define IWDG_Prescaler_32 ((uint8_t)0x03)

73 | #define IWDG_Prescaler_64 ((uint8_t)0x04)

74 | #define IWDG_Prescaler_128 ((uint8_t)0x05)

75 | #define IWDG_Prescaler_256 ((uint8_t)0x06)

76 | #define IS_IWDG_PRESCALER(PRESCALER) (((PRESCALER) == IWDG_Prescaler_4) || \

77 | ((PRESCALER) == IWDG_Prescaler_8) || \

78 | ((PRESCALER) == IWDG_Prescaler_16) || \

79 | ((PRESCALER) == IWDG_Prescaler_32) || \

80 | ((PRESCALER) == IWDG_Prescaler_64) || \

81 | ((PRESCALER) == IWDG_Prescaler_128)|| \

82 | ((PRESCALER) == IWDG_Prescaler_256))

83 | /**

84 | * @}

85 | */

86 |

87 | /** @defgroup IWDG_Flag

88 | * @{

89 | */

90 | #define IWDG_FLAG_PVU ((uint16_t)0x0001)

91 | #define IWDG_FLAG_RVU ((uint16_t)0x0002)

92 | #define IS_IWDG_FLAG(FLAG) (((FLAG) == IWDG_FLAG_PVU) || ((FLAG) == IWDG_FLAG_RVU))

93 | #define IS_IWDG_RELOAD(RELOAD) ((RELOAD) <= 0xFFF)

94 | /**

95 | * @}

96 | */

97 |

98 | /**

99 | * @}

100 | */

101 |

102 | /* Exported macro ------------------------------------------------------------*/

103 | /* Exported functions --------------------------------------------------------*/

104 |

105 | /* Prescaler and Counter configuration functions ******************************/

106 | void IWDG_WriteAccessCmd(uint16_t IWDG_WriteAccess);

107 | void IWDG_SetPrescaler(uint8_t IWDG_Prescaler);

108 | void IWDG_SetReload(uint16_t Reload);

109 | void IWDG_ReloadCounter(void);

110 |

111 | /* IWDG activation function ***************************************************/

112 | void IWDG_Enable(void);

113 |

114 | /* Flag management function ***************************************************/

115 | FlagStatus IWDG_GetFlagStatus(uint16_t IWDG_FLAG);

116 |

117 | #ifdef __cplusplus

118 | }

119 | #endif

120 |

121 | #endif /* __STM32F4xx_IWDG_H */

122 |

123 | /**

124 | * @}

125 | */

126 |

127 | /**

128 | * @}

129 | */

130 |

131 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

132 |

--------------------------------------------------------------------------------

/lib/STM32F4xx/STM32F4xx_StdPeriph_Driver/inc/stm32f4xx_pwr.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file stm32f4xx_pwr.h

4 | * @author MCD Application Team

5 | * @version V1.6.1

6 | * @date 21-October-2015

7 | * @brief This file contains all the functions prototypes for the PWR firmware

8 | * library.

9 | ******************************************************************************

10 | * @attention

11 | *

12 | * © COPYRIGHT 2015 STMicroelectronics

13 | *

14 | * Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

15 | * You may not use this file except in compliance with the License.

16 | * You may obtain a copy of the License at:

17 | *

18 | * http://www.st.com/software_license_agreement_liberty_v2

19 | *

20 | * Unless required by applicable law or agreed to in writing, software

21 | * distributed under the License is distributed on an "AS IS" BASIS,

22 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

23 | * See the License for the specific language governing permissions and

24 | * limitations under the License.

25 | *

26 | ******************************************************************************

27 | */

28 |

29 | /* Define to prevent recursive inclusion -------------------------------------*/

30 | #ifndef __STM32F4xx_PWR_H

31 | #define __STM32F4xx_PWR_H

32 |

33 | #ifdef __cplusplus

34 | extern "C" {

35 | #endif

36 |

37 | /* Includes ------------------------------------------------------------------*/

38 | #include "stm32f4xx.h"

39 |

40 | /** @addtogroup STM32F4xx_StdPeriph_Driver

41 | * @{

42 | */

43 |

44 | /** @addtogroup PWR

45 | * @{

46 | */

47 |

48 | /* Exported types ------------------------------------------------------------*/

49 | /* Exported constants --------------------------------------------------------*/

50 |

51 | /** @defgroup PWR_Exported_Constants

52 | * @{

53 | */

54 |

55 | /** @defgroup PWR_PVD_detection_level

56 | * @{

57 | */

58 | #define PWR_PVDLevel_0 PWR_CR_PLS_LEV0

59 | #define PWR_PVDLevel_1 PWR_CR_PLS_LEV1

60 | #define PWR_PVDLevel_2 PWR_CR_PLS_LEV2

61 | #define PWR_PVDLevel_3 PWR_CR_PLS_LEV3

62 | #define PWR_PVDLevel_4 PWR_CR_PLS_LEV4

63 | #define PWR_PVDLevel_5 PWR_CR_PLS_LEV5

64 | #define PWR_PVDLevel_6 PWR_CR_PLS_LEV6

65 | #define PWR_PVDLevel_7 PWR_CR_PLS_LEV7

66 |

67 | #define IS_PWR_PVD_LEVEL(LEVEL) (((LEVEL) == PWR_PVDLevel_0) || ((LEVEL) == PWR_PVDLevel_1)|| \

68 | ((LEVEL) == PWR_PVDLevel_2) || ((LEVEL) == PWR_PVDLevel_3)|| \

69 | ((LEVEL) == PWR_PVDLevel_4) || ((LEVEL) == PWR_PVDLevel_5)|| \

70 | ((LEVEL) == PWR_PVDLevel_6) || ((LEVEL) == PWR_PVDLevel_7))

71 | /**

72 | * @}

73 | */

74 |

75 |

76 | /** @defgroup PWR_Regulator_state_in_STOP_mode

77 | * @{

78 | */

79 | #define PWR_MainRegulator_ON ((uint32_t)0x00000000)

80 | #define PWR_LowPowerRegulator_ON PWR_CR_LPDS

81 |

82 | /* --- PWR_Legacy ---*/

83 | #define PWR_Regulator_ON PWR_MainRegulator_ON

84 | #define PWR_Regulator_LowPower PWR_LowPowerRegulator_ON

85 |

86 | #define IS_PWR_REGULATOR(REGULATOR) (((REGULATOR) == PWR_MainRegulator_ON) || \

87 | ((REGULATOR) == PWR_LowPowerRegulator_ON))

88 |

89 | /**

90 | * @}

91 | */

92 |

93 | /** @defgroup PWR_Regulator_state_in_UnderDrive_mode

94 | * @{

95 | */

96 | #define PWR_MainRegulator_UnderDrive_ON PWR_CR_MRUDS

97 | #define PWR_LowPowerRegulator_UnderDrive_ON ((uint32_t)(PWR_CR_LPDS | PWR_CR_LPUDS))

98 |

99 | #define IS_PWR_REGULATOR_UNDERDRIVE(REGULATOR) (((REGULATOR) == PWR_MainRegulator_UnderDrive_ON) || \

100 | ((REGULATOR) == PWR_LowPowerRegulator_UnderDrive_ON))

101 |

102 | /**

103 | * @}

104 | */

105 | #if defined(STM32F410xx) || defined(STM32F446xx)

106 | /** @defgroup PWR_Wake_Up_Pin

107 | * @{

108 | */

109 | #define PWR_WakeUp_Pin1 ((uint32_t)0x00)

110 | #define PWR_WakeUp_Pin2 ((uint32_t)0x01)

111 | #if defined(STM32F410xx)

112 | #define PWR_WakeUp_Pin3 ((uint32_t)0x02)

113 | #endif /* STM32F410xx */

114 |

115 | #if defined(STM32F446xx)

116 | #define IS_PWR_WAKEUP_PIN(PIN) (((PIN) == PWR_WakeUp_Pin1) || \

117 | ((PIN) == PWR_WakeUp_Pin2))

118 | #else /* STM32F410xx */

119 | #define IS_PWR_WAKEUP_PIN(PIN) (((PIN) == PWR_WAKEUP_PIN1) || ((PIN) == PWR_WAKEUP_PIN2) || \

120 | ((PIN) == PWR_WAKEUP_PIN3))

121 | #endif /* STM32F446xx */

122 | /**