├── Completed

├── work

│ ├── _vmake

│ ├── _lib.qdb

│ ├── _lib1_34.qdb

│ ├── _lib1_34.qpg

│ ├── _lib1_34.qtl

│ ├── _lib1_47.qdb

│ ├── _lib1_47.qpg

│ ├── _lib1_47.qtl

│ └── _info

├── ram.v

├── cache.v

├── testbench.v

├── cache_and_ram.v

├── testbench2.v

└── Completed parts.mpf

├── LICENSE

└── README.md

/Completed/work/_vmake:

--------------------------------------------------------------------------------

1 | m255

2 | K4

3 | z0

4 | cModel Technology

5 |

--------------------------------------------------------------------------------

/Completed/work/_lib.qdb:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/psnjk/SimpleCache/HEAD/Completed/work/_lib.qdb

--------------------------------------------------------------------------------

/Completed/work/_lib1_34.qdb:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/psnjk/SimpleCache/HEAD/Completed/work/_lib1_34.qdb

--------------------------------------------------------------------------------

/Completed/work/_lib1_34.qpg:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/psnjk/SimpleCache/HEAD/Completed/work/_lib1_34.qpg

--------------------------------------------------------------------------------

/Completed/work/_lib1_34.qtl:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/psnjk/SimpleCache/HEAD/Completed/work/_lib1_34.qtl

--------------------------------------------------------------------------------

/Completed/work/_lib1_47.qdb:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/psnjk/SimpleCache/HEAD/Completed/work/_lib1_47.qdb

--------------------------------------------------------------------------------

/Completed/work/_lib1_47.qpg:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/psnjk/SimpleCache/HEAD/Completed/work/_lib1_47.qpg

--------------------------------------------------------------------------------

/Completed/work/_lib1_47.qtl:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/psnjk/SimpleCache/HEAD/Completed/work/_lib1_47.qtl

--------------------------------------------------------------------------------

/Completed/ram.v:

--------------------------------------------------------------------------------

1 | module ram();

2 |

3 | parameter size = 4096; //size of a ram in bits

4 |

5 | reg [31:0] ram [0:size-1]; //data matrix for ram

6 |

7 | endmodule

8 |

--------------------------------------------------------------------------------

/Completed/cache.v:

--------------------------------------------------------------------------------

1 | module cache();

2 |

3 | parameter size = 64; // cache size

4 | parameter index_size = 6; // index size

5 |

6 |

7 | reg [31:0] cache [0:size - 1]; //registers for the data in cache

8 | reg [11 - index_size:0] tag_array [0:size - 1]; // for all tags in cache

9 | reg valid_array [0:size - 1]; //0 - there is no data 1 - there is data

10 |

11 | initial

12 | begin: initialization

13 | integer i;

14 | for (i = 0; i < size; i = i + 1)

15 | begin

16 | valid_array[i] = 1'b0;

17 | tag_array[i] = 6'b000000;

18 | end

19 | end

20 |

21 | endmodule

22 |

--------------------------------------------------------------------------------

/LICENSE:

--------------------------------------------------------------------------------

1 | MIT License

2 |

3 | Copyright (c) 2018 Jameel Mukhutdinov

4 |

5 | Permission is hereby granted, free of charge, to any person obtaining a copy

6 | of this software and associated documentation files (the "Software"), to deal

7 | in the Software without restriction, including without limitation the rights

8 | to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

9 | copies of the Software, and to permit persons to whom the Software is

10 | furnished to do so, subject to the following conditions:

11 |

12 | The above copyright notice and this permission notice shall be included in all

13 | copies or substantial portions of the Software.

14 |

15 | THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

16 | IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

17 | FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

18 | AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

19 | LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

20 | OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE

21 | SOFTWARE.

22 |

--------------------------------------------------------------------------------

/Completed/testbench.v:

--------------------------------------------------------------------------------

1 | module testbench;

2 |

3 | reg [31:0] address, data;

4 | reg mode, clk;

5 | wire [31:0] out;

6 |

7 | cache_and_ram tb(

8 | .address(address),

9 | .data(data),

10 | .mode(mode),

11 | .clk(clk),

12 | .out(out)

13 | );

14 |

15 | initial

16 | begin

17 | clk = 1'b1;

18 |

19 | address = 32'b00000000000000000000000000000000; // 0

20 | data = 32'b00000000000000000011100011000000; // 14528

21 | mode = 1'b1;

22 |

23 | #200

24 | address = 32'b10100111111001011111101111011100; // 2816867292 % size = 3036

25 | data = 32'b00000000000010000000100001010101; // 526421

26 | mode = 1'b1;

27 |

28 | #200

29 | address = 32'b00000000000011110100011111010001; // 1001425 % size = 2001

30 | data = 32'b00000001100000110001101100010110; // 25369366

31 | mode = 1'b1;

32 |

33 | #200

34 | address = 32'b10100111111001011111101111011100; // 2816867292 % size = 3036

35 | data = 32'b00000000000000000011100011000000; // 14528

36 | mode = 1'b1;

37 |

38 | #200

39 | address = 32'b00000000000011110100011111010001; // 1001425 % size = 2001

40 | data = 32'b00000000000000000011100011000000; // 14528

41 | mode = 1'b1;

42 |

43 | #200

44 | address = 32'b00000000000011110100011111010001; // 1001425 % size = 2001

45 | data = 32'b00000000000000000000000000000000; // 0

46 | mode = 1'b0;

47 |

48 | #200

49 | address = 32'b10100111111001011111101111011100; // 2816867292 % size = 3036

50 | data = 32'b00000000000000000000000000000000; // 0

51 | mode = 1'b0;

52 |

53 | #200

54 | address = 32'b00000000000000000000000000000000; // 0

55 | data = 32'b00000000000000000011100011000000; // 14528

56 | mode = 1'b0;

57 | end

58 |

59 | initial

60 | $monitor("address = %d data = %d mode = %d out = %d", address % 4096, data, mode, out);

61 |

62 | always #25 clk = ~clk;

63 |

64 | endmodule

65 |

--------------------------------------------------------------------------------

/Completed/cache_and_ram.v:

--------------------------------------------------------------------------------

1 | module cache_and_ram(

2 | input [31:0] address,

3 | input [31:0] data,

4 | input clk,

5 | input mode, //mode equal to 1 when we write and equal to 0 when we read

6 | output [31:0] out

7 | );

8 |

9 | //previous values

10 | reg [31:0] prev_address, prev_data;

11 | reg prev_mode;

12 | reg [31:0] temp_out;

13 |

14 | reg [cache.index_size - 1:0] index; // for keeping index of current address

15 | reg [11 - cache.index_size:0] tag; // for keeping tag of ceurrent address

16 |

17 | ram ram();

18 | cache cache();

19 |

20 | initial

21 | begin

22 | index = 0;

23 | tag = 0;

24 | prev_address = 0;

25 | prev_data = 0;

26 | prev_mode = 0;

27 | end

28 |

29 | always @(posedge clk)

30 | begin

31 | //check if the new input is updated

32 | if (prev_address != address || prev_data != data || prev_mode != mode)

33 | begin

34 | prev_address = address % ram.size;

35 | prev_data = data;

36 | prev_mode = mode;

37 |

38 | tag = prev_address >> cache.index_size; // tag = first bits of address except index ones (In our particular case - 6)

39 | index = address % cache.size; // index value = last n (n = size of cache) bits of address

40 |

41 | if (mode == 1)

42 | begin

43 | ram.ram[prev_address] = data;

44 | //write new data to the relevant cache block if there is such one

45 | if (cache.valid_array[index] == 1 && cache.tag_array[index] == tag)

46 | cache.cache[index] = data;

47 | end

48 | else

49 | begin

50 | //write new data to the relevant cache's block, because the one we addressing to will be possibly addressed one more time soon

51 | if (cache.valid_array[index] != 1 || cache.tag_array[index] != tag)

52 | begin

53 | cache.valid_array[index] = 1;

54 | cache.tag_array[index] = tag;

55 | cache.cache[index] = ram.ram[prev_address];

56 | end

57 | temp_out = cache.cache[index];

58 | end

59 | end

60 | end

61 |

62 | assign out = temp_out;

63 |

64 | endmodule

65 |

--------------------------------------------------------------------------------

/Completed/testbench2.v:

--------------------------------------------------------------------------------

1 | module testbench2;

2 |

3 | reg [31:0] address, data;

4 | reg mode, clk;

5 | wire [31:0] out;

6 |

7 | cache_and_ram tb(

8 | .address(address),

9 | .data(data),

10 | .mode(mode),

11 | .clk(clk),

12 | .out(out)

13 | );

14 |

15 | initial

16 | begin

17 | clk = 1'b1;

18 |

19 | address = 32'b00000000000000000000000000000000; // 0

20 | data = 32'b00000000000000000011100011000000; // 14528

21 | mode = 1'b1;

22 |

23 | #200

24 | address = 32'b10100111111001011111101111011100; // 2816867292 % size = 3036

25 | data = 32'b00000000000010000000100001010101; // 526421

26 | mode = 1'b1;

27 |

28 | #200

29 | address = 32'b00000000000000000000000000000000; // 0

30 | data = 32'b00000000000000000011100011000000; // 14528

31 | mode = 1'b0;

32 |

33 | #200

34 | address = 32'b10100111111001011111101111011100; // 2816867292 % size = 3036

35 | data = 32'b00000000000010000000100001010101; // 526421

36 | mode = 1'b0;

37 |

38 | #200

39 | address = 32'b00000000000011110100011111010001; // 1001425 % size = 2001

40 | data = 32'b00000001100000110001101100010110; // 25369366

41 | mode = 1'b1;

42 |

43 | #200

44 | address = 32'b00000000000011110100011111010001; // 1001425 % size = 2001

45 | data = 32'b00000001100000110001101100010110; // 25369366

46 | mode = 1'b0;

47 |

48 | #200

49 | address = 32'b10100111111001011111101111011100; // 2816867292 % size = 3036

50 | data = 32'b00000000000000000011100011000000; // 14528

51 | mode = 1'b1;

52 |

53 | #200

54 | address = 32'b00000000000011110100011111010001; // 1001425 % size = 2001

55 | data = 32'b00000000000000000011100011000000; // 14528

56 | mode = 1'b1;

57 |

58 | #200

59 | address = 32'b00000000000011110100011111010001; // 1001425 % size = 2001

60 | data = 32'b00000000000000000000000000000000; // 0

61 | mode = 1'b0;

62 |

63 | #200

64 | address = 32'b10100111111001011111101111011100; // 2816867292 % size = 3036

65 | data = 32'b00000000000000000000000000000000; // 0

66 | mode = 1'b0;

67 | end

68 |

69 | initial

70 | $monitor("address = %d data = %d mode = %d out = %d", address % 4096, data, mode, out);

71 |

72 | always #25 clk = ~clk;

73 |

74 | endmodule

75 |

--------------------------------------------------------------------------------

/README.md:

--------------------------------------------------------------------------------

1 |

2 |

3 | # Simple direct-mapped cache simulation on FPGA

4 | ------

5 | The subject of this article is the topic of the project for first year bachelors, the purpose of which is to show an understanding of the topic, or to help to understand it using simulation.

6 | ___

7 |

8 | Principle of work but from the user side should look like:

9 | * To write any data in memory, you need to access the RAM with data and address in which we want to write.

10 | * To access the data, we have to adress to cache. If the cache cannot find the necessary data, then it accesses the RAM by copying data from there.

11 |

12 | When working with Verilog, it should be understood that each individual block of the program is represented as a module. As you know, the cache is not an independent part of fast memory, and for its proper operation it needs to take data from another memory block - RAM. Therefore, in order to simulate the work of the cache at the FPGA, we have to simulate whole RAM module which includes cache as well, but the main point is cache simulation.

13 |

14 | The implementation consists of such modules:

15 | * ram.v - RAM memory module

16 | * cache.v - Cache memory module

17 | * cache_and_ram.v - module that operates with data and memory.

18 |

19 |

20 |

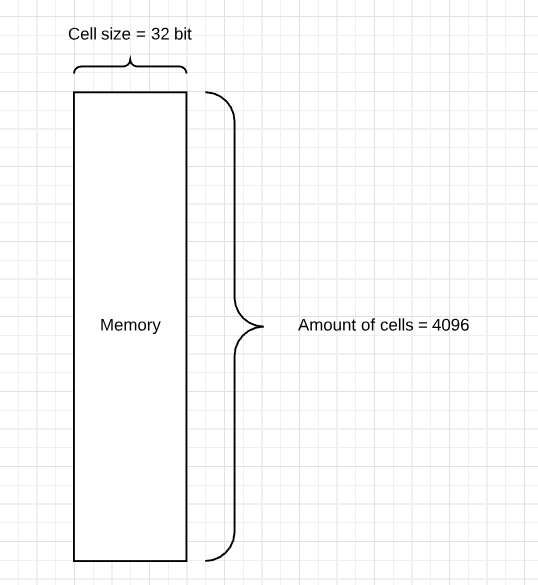

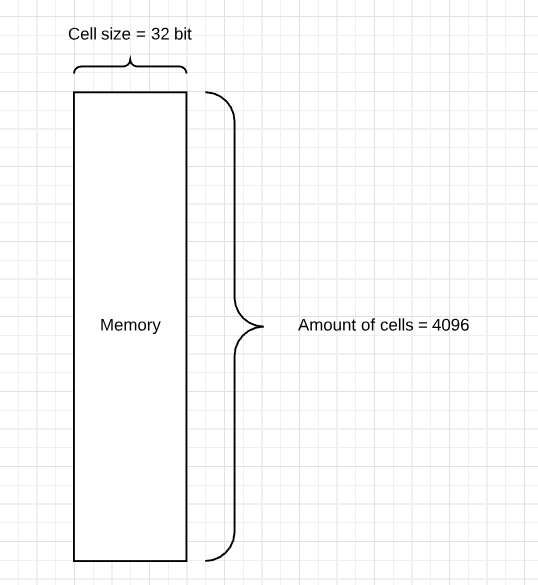

21 | ### RAM module:

22 |

23 | ```verilog

24 | module ram();

25 |

26 | parameter size = 4096; //size of a ram in bits

27 |

28 | reg [31:0] ram [0:size-1]; //data matrix for ram

29 |

30 | endmodule

31 | ```

32 |

33 |

34 |

35 | Module represents memory which is used as RAM. It has 4096 32-bit addressable cells to store some data.

36 |

37 |

38 |  39 | ---

40 |

41 | ###Cache module:

42 |

43 | ```verilog

44 | module cache();

45 |

46 | parameter size = 64; // cache size

47 | parameter index_size = 6; // index size

48 |

49 |

50 | reg [31:0] cache [0:size - 1]; //registers for the data in cache

51 | reg [11 - index_size:0] tag_array [0:size - 1]; // for all tags in cache

52 | reg valid_array [0:size - 1]; //0 - there is no data 1 - there is data

53 |

54 | initial

55 | begin: initialization

56 | integer i;

57 | for (i = 0; i < size; i = i + 1)

58 | begin

59 | valid_array[i] = 6'b000000;

60 | tag_array[i] = 6'b000000;

61 | end

62 | end

63 |

64 | endmodule

65 | ```

66 |

67 |

68 | So the cache contains more than just copies of the data in

69 | memory; it also has bits to help us find data within the cache and

70 | verify its validity.

71 |

72 |

39 | ---

40 |

41 | ###Cache module:

42 |

43 | ```verilog

44 | module cache();

45 |

46 | parameter size = 64; // cache size

47 | parameter index_size = 6; // index size

48 |

49 |

50 | reg [31:0] cache [0:size - 1]; //registers for the data in cache

51 | reg [11 - index_size:0] tag_array [0:size - 1]; // for all tags in cache

52 | reg valid_array [0:size - 1]; //0 - there is no data 1 - there is data

53 |

54 | initial

55 | begin: initialization

56 | integer i;

57 | for (i = 0; i < size; i = i + 1)

58 | begin

59 | valid_array[i] = 6'b000000;

60 | tag_array[i] = 6'b000000;

61 | end

62 | end

63 |

64 | endmodule

65 | ```

66 |

67 |

68 | So the cache contains more than just copies of the data in

69 | memory; it also has bits to help us find data within the cache and

70 | verify its validity.

71 |

72 |  73 | ---

74 |

75 | ###Cache and RAM module:

76 |

77 | ```verilog

78 | module cache_and_ram(

79 | input [31:0] address,

80 | input [31:0] data,

81 | input clk,

82 | input mode,

83 | output [31:0] out

84 | );

85 |

86 | //previous values

87 | reg [31:0] prev_address, prev_data;

88 | reg prev_mode;

89 | reg [31:0] temp_out;

90 |

91 | reg [cache.index_size - 1:0] index; // for keeping index of current address

92 | reg [11 - cache.index_size:0] tag; // for keeping tag of ceurrent address

93 |

94 | ram ram();

95 | cache cache();

96 |

97 | initial

98 | begin

99 | index = 0;

100 | tag = 0;

101 | prev_address = 0;

102 | prev_data = 0;

103 | prev_mode = 0;

104 | end

105 |

106 | always @(edge clk)

107 | begin

108 | //check if the new input is updated

109 | if (prev_address != address || prev_data != data || prev_mode != mode)

110 | begin

111 | prev_address = address % ram.size;

112 | prev_data = data;

113 | prev_mode = mode;

114 |

115 | tag = prev_address >> cache.index_size; // tag = first bits of address except index ones (In our particular case - 6)

116 | index = address % cache.size; // index value = last n (n = size of cache) bits of address

117 |

118 | if (mode == 1)

119 | begin

120 | ram.ram[prev_address] = data;

121 | //write new data to the relevant cache block if there is such one

122 | if (cache.valid_array[index] == 1 && cache.tag_array[index] == tag)

123 | cache.cache[index] = data;

124 | end

125 | else

126 | begin

127 | //write new data to the relevant cache's block, because the one we addressing to will be possibly addressed one more time soon

128 | if (cache.valid_array[index] != 1 || cache.tag_array[index] != tag)

129 | begin

130 | cache.valid_array[index] = 1;

131 | cache.tag_array[index] = tag;

132 | cache.cache[index] = ram.ram[prev_address];

133 | end

134 | temp_out = cache.cache[index];

135 | end

136 | end

137 | end

138 |

139 | assign out = temp_out;

140 |

141 | endmodule

142 | ```

143 |

144 |

145 |

--------------------------------------------------------------------------------

/Completed/work/_info:

--------------------------------------------------------------------------------

1 | m255

2 | K4

3 | z2

4 | 13

5 | !s112 1.1

6 | !i10d 8192

7 | !i10e 25

8 | !i10f 100

9 | cModel Technology

10 | dC:/intelFPGA_lite/18.0

11 | vcache

12 | Z0 !s110 1541601841

13 | !i10b 1

14 | !s100 AM?Kj>YPoQbPh@O5HzlJz1

15 | Ik:X?bcd9RU`eaPG2^lFQ>3

16 | Z1 VDg1SIo80bB@j0V0VzS_@n1

17 | Z2 dD:/Alphy/Doc/GitHub/SimpleCache/Completed

18 | w1541601388

19 | 8D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache.v

20 | FD:/Alphy/Doc/GitHub/SimpleCache/Completed/cache.v

21 | L0 1

22 | Z3 OV;L;10.5b;63

23 | r1

24 | !s85 0

25 | 31

26 | Z4 !s108 1541601841.000000

27 | !s107 D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache.v|

28 | !s90 -reportprogress|300|-work|work|-stats=none|D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache.v|

29 | !i113 1

30 | Z5 o-work work

31 | Z6 tCvgOpt 0

32 | vcache_and_ram

33 | R0

34 | !i10b 1

35 | !s100 Nc:T^JLco77jjQieUD7KI1

36 | Io@TdV>O?9b`44WfK7m3DNc]D_^0

58 | R1

59 | R2

60 | w1541343442

61 | 8D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_and_ram_clever_tb.v

62 | FD:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_and_ram_clever_tb.v

63 | L0 1

64 | R3

65 | r1

66 | !s85 0

67 | 31

68 | Z8 !s108 1541601665.000000

69 | !s107 D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_and_ram_clever_tb.v|

70 | !s90 -reportprogress|300|-work|work|-stats=none|D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_and_ram_clever_tb.v|

71 | !i113 1

72 | R5

73 | R6

74 | vcache_and_ram_tb

75 | Z9 !s110 1541600898

76 | !i10b 1

77 | !s100 11eVoEgSlk5GNZn<0j12THL^VB4E8OY2

121 | R1

122 | R2

123 | w1541600591

124 | 8D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode.v

125 | FD:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode.v

126 | L0 1

127 | R3

128 | r1

129 | !s85 0

130 | 31

131 | !s108 1541601310.000000

132 | !s107 D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode.v|

133 | !s90 -reportprogress|300|-work|work|-stats=none|D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode.v|

134 | !i113 1

135 | R5

136 | R6

137 | vcache_no_mode_clever

138 | !s110 1541601666

139 | !i10b 1

140 | !s100 D[^Q^C=lVDa47<3JZEQ`L0

141 | ICD03[[8oi9<3:z<]_]UY>0

142 | R1

143 | R2

144 | w1541344294

145 | 8D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode_clever.v

146 | FD:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode_clever.v

147 | L0 1

148 | R3

149 | r1

150 | !s85 0

151 | 31

152 | !s108 1541601666.000000

153 | !s107 D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode_clever.v|

154 | !s90 -reportprogress|300|-work|work|-stats=none|D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode_clever.v|

155 | !i113 1

156 | R5

157 | R6

158 | vram

159 | R0

160 | !i10b 1

161 | !s100 mY;G_1fYOo`4JBPMTLMB?3

162 | I1bg9H6fnDhR>EZ[h1>`BJ3

163 | R1

164 | R2

165 | w1541598700

166 | 8D:/Alphy/Doc/GitHub/SimpleCache/Completed/ram.v

167 | FD:/Alphy/Doc/GitHub/SimpleCache/Completed/ram.v

168 | L0 1

169 | R3

170 | r1

171 | !s85 0

172 | 31

173 | R4

174 | !s107 D:/Alphy/Doc/GitHub/SimpleCache/Completed/ram.v|

175 | !s90 -reportprogress|300|-work|work|-stats=none|D:/Alphy/Doc/GitHub/SimpleCache/Completed/ram.v|

176 | !i113 1

177 | R5

178 | R6

179 | vram_clever

180 | R7

181 | !i10b 1

182 | !s100 _d>z=zSmXV=cea0TP2^`32

183 | IM?jOUE^70hkj0Gh>EcbJa0

184 | R1

185 | R2

186 | w1541339652

187 | 8D:/Alphy/Doc/GitHub/SimpleCache/Completed/ram_clever.v

188 | FD:/Alphy/Doc/GitHub/SimpleCache/Completed/ram_clever.v

189 | L0 1

190 | R3

191 | r1

192 | !s85 0

193 | 31

194 | R8

195 | !s107 D:/Alphy/Doc/GitHub/SimpleCache/Completed/ram_clever.v|

196 | !s90 -reportprogress|300|-work|work|-stats=none|D:/Alphy/Doc/GitHub/SimpleCache/Completed/ram_clever.v|

197 | !i113 1

198 | R5

199 | R6

200 | vram_tb

201 | R11

202 | !i10b 1

203 | !s100 gTl]^[52Xfo2g50d9b1eX;ml_ioQ2n4z@D2

268 | R1

269 | R2

270 | w1541343988

271 | 8D:/Alphy/Doc/GitHub/SimpleCache/Completed/testbench_for_clevers.v

272 | FD:/Alphy/Doc/GitHub/SimpleCache/Completed/testbench_for_clevers.v

273 | L0 1

274 | R3

275 | r1

276 | !s85 0

277 | 31

278 | R10

279 | !s107 D:/Alphy/Doc/GitHub/SimpleCache/Completed/testbench_for_clevers.v|

280 | !s90 -reportprogress|300|-work|work|-stats=none|D:/Alphy/Doc/GitHub/SimpleCache/Completed/testbench_for_clevers.v|

281 | !i113 1

282 | R5

283 | R6

284 |

--------------------------------------------------------------------------------

/Completed/Completed parts.mpf:

--------------------------------------------------------------------------------

1 | ; Copyright 1991-2009 Mentor Graphics Corporation

2 | ;

3 | ; All Rights Reserved.

4 | ;

5 | ; THIS WORK CONTAINS TRADE SECRET AND PROPRIETARY INFORMATION WHICH IS THE PROPERTY OF

6 | ; MENTOR GRAPHICS CORPORATION OR ITS LICENSORS AND IS SUBJECT TO LICENSE TERMS.

7 | ;

8 |

9 | [Library]

10 | std = $MODEL_TECH/../std

11 | ieee = $MODEL_TECH/../ieee

12 | verilog = $MODEL_TECH/../verilog

13 | vital2000 = $MODEL_TECH/../vital2000

14 | std_developerskit = $MODEL_TECH/../std_developerskit

15 | synopsys = $MODEL_TECH/../synopsys

16 | modelsim_lib = $MODEL_TECH/../modelsim_lib

17 | sv_std = $MODEL_TECH/../sv_std

18 |

19 | ; Altera Primitive libraries

20 | ;

21 | ; VHDL Section

22 | ;

23 | altera_mf = $MODEL_TECH/../altera/vhdl/altera_mf

24 | altera = $MODEL_TECH/../altera/vhdl/altera

25 | altera_lnsim = $MODEL_TECH/../altera/vhdl/altera_lnsim

26 | lpm = $MODEL_TECH/../altera/vhdl/220model

27 | 220model = $MODEL_TECH/../altera/vhdl/220model

28 | maxii = $MODEL_TECH/../altera/vhdl/maxii

29 | maxv = $MODEL_TECH/../altera/vhdl/maxv

30 | fiftyfivenm = $MODEL_TECH/../altera/vhdl/fiftyfivenm

31 | sgate = $MODEL_TECH/../altera/vhdl/sgate

32 | arriaii = $MODEL_TECH/../altera/vhdl/arriaii

33 | arriaii_hssi = $MODEL_TECH/../altera/vhdl/arriaii_hssi

34 | arriaii_pcie_hip = $MODEL_TECH/../altera/vhdl/arriaii_pcie_hip

35 | arriaiigz = $MODEL_TECH/../altera/vhdl/arriaiigz

36 | arriaiigz_hssi = $MODEL_TECH/../altera/vhdl/arriaiigz_hssi

37 | arriaiigz_pcie_hip = $MODEL_TECH/../altera/vhdl/arriaiigz_pcie_hip

38 | stratixiv = $MODEL_TECH/../altera/vhdl/stratixiv

39 | stratixiv_hssi = $MODEL_TECH/../altera/vhdl/stratixiv_hssi

40 | stratixiv_pcie_hip = $MODEL_TECH/../altera/vhdl/stratixiv_pcie_hip

41 | cycloneiv = $MODEL_TECH/../altera/vhdl/cycloneiv

42 | cycloneiv_hssi = $MODEL_TECH/../altera/vhdl/cycloneiv_hssi

43 | cycloneiv_pcie_hip = $MODEL_TECH/../altera/vhdl/cycloneiv_pcie_hip

44 | cycloneive = $MODEL_TECH/../altera/vhdl/cycloneive

45 | stratixv = $MODEL_TECH/../altera/vhdl/stratixv

46 | stratixv_hssi = $MODEL_TECH/../altera/vhdl/stratixv_hssi

47 | stratixv_pcie_hip = $MODEL_TECH/../altera/vhdl/stratixv_pcie_hip

48 | arriavgz = $MODEL_TECH/../altera/vhdl/arriavgz

49 | arriavgz_hssi = $MODEL_TECH/../altera/vhdl/arriavgz_hssi

50 | arriavgz_pcie_hip = $MODEL_TECH/../altera/vhdl/arriavgz_pcie_hip

51 | arriav = $MODEL_TECH/../altera/vhdl/arriav

52 | cyclonev = $MODEL_TECH/../altera/vhdl/cyclonev

53 | twentynm = $MODEL_TECH/../altera/vhdl/twentynm

54 | twentynm_hssi = $MODEL_TECH/../altera/vhdl/twentynm_hssi

55 | twentynm_hip = $MODEL_TECH/../altera/vhdl/twentynm_hip

56 | cyclone10lp = $MODEL_TECH/../altera/vhdl/cyclone10lp

57 | ;

58 | ; Verilog Section

59 | ;

60 | altera_mf_ver = $MODEL_TECH/../altera/verilog/altera_mf

61 | altera_ver = $MODEL_TECH/../altera/verilog/altera

62 | altera_lnsim_ver = $MODEL_TECH/../altera/verilog/altera_lnsim

63 | lpm_ver = $MODEL_TECH/../altera/verilog/220model

64 | 220model_ver = $MODEL_TECH/../altera/verilog/220model

65 | maxii_ver = $MODEL_TECH/../altera/verilog/maxii

66 | maxv_ver = $MODEL_TECH/../altera/verilog/maxv

67 | fiftyfivenm_ver = $MODEL_TECH/../altera/verilog/fiftyfivenm

68 | sgate_ver = $MODEL_TECH/../altera/verilog/sgate

69 | arriaii_ver = $MODEL_TECH/../altera/verilog/arriaii

70 | arriaii_hssi_ver = $MODEL_TECH/../altera/verilog/arriaii_hssi

71 | arriaii_pcie_hip_ver = $MODEL_TECH/../altera/verilog/arriaii_pcie_hip

72 | arriaiigz_ver = $MODEL_TECH/../altera/verilog/arriaiigz

73 | arriaiigz_hssi_ver = $MODEL_TECH/../altera/verilog/arriaiigz_hssi

74 | arriaiigz_pcie_hip_ver = $MODEL_TECH/../altera/verilog/arriaiigz_pcie_hip

75 | stratixiv_ver = $MODEL_TECH/../altera/verilog/stratixiv

76 | stratixiv_hssi_ver = $MODEL_TECH/../altera/verilog/stratixiv_hssi

77 | stratixiv_pcie_hip_ver = $MODEL_TECH/../altera/verilog/stratixiv_pcie_hip

78 | stratixv_ver = $MODEL_TECH/../altera/verilog/stratixv

79 | stratixv_hssi_ver = $MODEL_TECH/../altera/verilog/stratixv_hssi

80 | stratixv_pcie_hip_ver = $MODEL_TECH/../altera/verilog/stratixv_pcie_hip

81 | arriavgz_ver = $MODEL_TECH/../altera/verilog/arriavgz

82 | arriavgz_hssi_ver = $MODEL_TECH/../altera/verilog/arriavgz_hssi

83 | arriavgz_pcie_hip_ver = $MODEL_TECH/../altera/verilog/arriavgz_pcie_hip

84 | arriav_ver = $MODEL_TECH/../altera/verilog/arriav

85 | arriav_hssi_ver = $MODEL_TECH/../altera/verilog/arriav_hssi

86 | arriav_pcie_hip_ver = $MODEL_TECH/../altera/verilog/arriav_pcie_hip

87 | cyclonev_ver = $MODEL_TECH/../altera/verilog/cyclonev

88 | cyclonev_hssi_ver = $MODEL_TECH/../altera/verilog/cyclonev_hssi

89 | cyclonev_pcie_hip_ver = $MODEL_TECH/../altera/verilog/cyclonev_pcie_hip

90 | cycloneiv_ver = $MODEL_TECH/../altera/verilog/cycloneiv

91 | cycloneiv_hssi_ver = $MODEL_TECH/../altera/verilog/cycloneiv_hssi

92 | cycloneiv_pcie_hip_ver = $MODEL_TECH/../altera/verilog/cycloneiv_pcie_hip

93 | cycloneive_ver = $MODEL_TECH/../altera/verilog/cycloneive

94 | twentynm_ver = $MODEL_TECH/../altera/verilog/twentynm

95 | twentynm_hssi_ver = $MODEL_TECH/../altera/verilog/twentynm_hssi

96 | twentynm_hip_ver = $MODEL_TECH/../altera/verilog/twentynm_hip

97 | cyclone10lp_ver = $MODEL_TECH/../altera/verilog/cyclone10lp

98 |

99 | work = work

100 | [vcom]

101 | ; VHDL93 variable selects language version as the default.

102 | ; Default is VHDL-2002.

103 | ; Value of 0 or 1987 for VHDL-1987.

104 | ; Value of 1 or 1993 for VHDL-1993.

105 | ; Default or value of 2 or 2002 for VHDL-2002.

106 | ; Default or value of 3 or 2008 for VHDL-2008.

107 | VHDL93 = 2002

108 |

109 | ; Show source line containing error. Default is off.

110 | ; Show_source = 1

111 |

112 | ; Turn off unbound-component warnings. Default is on.

113 | ; Show_Warning1 = 0

114 |

115 | ; Turn off process-without-a-wait-statement warnings. Default is on.

116 | ; Show_Warning2 = 0

117 |

118 | ; Turn off null-range warnings. Default is on.

119 | ; Show_Warning3 = 0

120 |

121 | ; Turn off no-space-in-time-literal warnings. Default is on.

122 | ; Show_Warning4 = 0

123 |

124 | ; Turn off multiple-drivers-on-unresolved-signal warnings. Default is on.

125 | ; Show_Warning5 = 0

126 |

127 | ; Turn off optimization for IEEE std_logic_1164 package. Default is on.

128 | ; Optimize_1164 = 0

129 |

130 | ; Turn on resolving of ambiguous function overloading in favor of the

131 | ; "explicit" function declaration (not the one automatically created by

132 | ; the compiler for each type declaration). Default is off.

133 | ; The .ini file has Explicit enabled so that std_logic_signed/unsigned

134 | ; will match the behavior of synthesis tools.

135 | Explicit = 1

136 |

137 | ; Turn off acceleration of the VITAL packages. Default is to accelerate.

138 | ; NoVital = 1

139 |

140 | ; Turn off VITAL compliance checking. Default is checking on.

141 | ; NoVitalCheck = 1

142 |

143 | ; Ignore VITAL compliance checking errors. Default is to not ignore.

144 | ; IgnoreVitalErrors = 1

145 |

146 | ; Turn off VITAL compliance checking warnings. Default is to show warnings.

147 | ; Show_VitalChecksWarnings = 0

148 |

149 | ; Keep silent about case statement static warnings.

150 | ; Default is to give a warning.

151 | ; NoCaseStaticError = 1

152 |

153 | ; Keep silent about warnings caused by aggregates that are not locally static.

154 | ; Default is to give a warning.

155 | ; NoOthersStaticError = 1

156 |

157 | ; Turn off inclusion of debugging info within design units.

158 | ; Default is to include debugging info.

159 | ; NoDebug = 1

160 |

161 | ; Turn off "Loading..." messages. Default is messages on.

162 | ; Quiet = 1

163 |

164 | ; Turn on some limited synthesis rule compliance checking. Checks only:

165 | ; -- signals used (read) by a process must be in the sensitivity list

166 | ; CheckSynthesis = 1

167 |

168 | ; Activate optimizations on expressions that do not involve signals,

169 | ; waits, or function/procedure/task invocations. Default is off.

170 | ; ScalarOpts = 1

171 |

172 | ; Require the user to specify a configuration for all bindings,

173 | ; and do not generate a compile time default binding for the

174 | ; component. This will result in an elaboration error of

175 | ; 'component not bound' if the user fails to do so. Avoids the rare

176 | ; issue of a false dependency upon the unused default binding.

177 | ; RequireConfigForAllDefaultBinding = 1

178 |

179 | ; Inhibit range checking on subscripts of arrays. Range checking on

180 | ; scalars defined with subtypes is inhibited by default.

181 | ; NoIndexCheck = 1

182 |

183 | ; Inhibit range checks on all (implicit and explicit) assignments to

184 | ; scalar objects defined with subtypes.

185 | ; NoRangeCheck = 1

186 |

187 | [vlog]

188 |

189 | ; Turn off inclusion of debugging info within design units.

190 | ; Default is to include debugging info.

191 | ; NoDebug = 1

192 |

193 | ; Turn off "loading..." messages. Default is messages on.

194 | ; Quiet = 1

195 |

196 | ; Turn on Verilog hazard checking (order-dependent accessing of global vars).

197 | ; Default is off.

198 | ; Hazard = 1

199 |

200 | ; Turn on converting regular Verilog identifiers to uppercase. Allows case

201 | ; insensitivity for module names. Default is no conversion.

202 | ; UpCase = 1

203 |

204 | ; Turn on incremental compilation of modules. Default is off.

205 | ; Incremental = 1

206 |

207 | ; Turns on lint-style checking.

208 | ; Show_Lint = 1

209 |

210 | [vsim]

211 | ; Simulator resolution

212 | ; Set to fs, ps, ns, us, ms, or sec with optional prefix of 1, 10, or 100.

213 | Resolution = ps

214 |

215 | ; User time unit for run commands

216 | ; Set to default, fs, ps, ns, us, ms, or sec. The default is to use the

217 | ; unit specified for Resolution. For example, if Resolution is 100ps,

218 | ; then UserTimeUnit defaults to ps.

219 | ; Should generally be set to default.

220 | UserTimeUnit = default

221 |

222 | ; Default run length

223 | RunLength = 27012000011 ns

224 |

225 | ; Maximum iterations that can be run without advancing simulation time

226 | IterationLimit = 10000000

227 |

228 | ; Directive to license manager:

229 | ; vhdl Immediately reserve a VHDL license

230 | ; vlog Immediately reserve a Verilog license

231 | ; plus Immediately reserve a VHDL and Verilog license

232 | ; nomgc Do not look for Mentor Graphics Licenses

233 | ; nomti Do not look for Model Technology Licenses

234 | ; noqueue Do not wait in the license queue when a license isn't available

235 | ; viewsim Try for viewer license but accept simulator license(s) instead

236 | ; of queuing for viewer license

237 | ; License = plus

238 |

239 | ; Stop the simulator after a VHDL/Verilog assertion message

240 | ; 0 = Note 1 = Warning 2 = Error 3 = Failure 4 = Fatal

241 | BreakOnAssertion = 3

242 |

243 | ; Assertion Message Format

244 | ; %S - Severity Level

245 | ; %R - Report Message

246 | ; %T - Time of assertion

247 | ; %D - Delta

248 | ; %I - Instance or Region pathname (if available)

249 | ; %% - print '%' character

250 | ; AssertionFormat = "** %S: %R\n Time: %T Iteration: %D%I\n"

251 |

252 | ; Assertion File - alternate file for storing VHDL/Verilog assertion messages

253 | ; AssertFile = assert.log

254 |

255 | ; Default radix for all windows and commands...

256 | ; Set to symbolic, ascii, binary, octal, decimal, hex, unsigned

257 | DefaultRadix = symbolic

258 |

259 | ; VSIM Startup command

260 | ; Startup = do startup.do

261 |

262 | ; File for saving command transcript

263 | TranscriptFile = transcript

264 |

265 | ; File for saving command history

266 | ; CommandHistory = cmdhist.log

267 |

268 | ; Specify whether paths in simulator commands should be described

269 | ; in VHDL or Verilog format.

270 | ; For VHDL, PathSeparator = /

271 | ; For Verilog, PathSeparator = .

272 | ; Must not be the same character as DatasetSeparator.

273 | PathSeparator = /

274 |

275 | ; Specify the dataset separator for fully rooted contexts.

276 | ; The default is ':'. For example, sim:/top

277 | ; Must not be the same character as PathSeparator.

278 | DatasetSeparator = :

279 |

280 | ; Disable VHDL assertion messages

281 | ; IgnoreNote = 1

282 | ; IgnoreWarning = 1

283 | ; IgnoreError = 1

284 | ; IgnoreFailure = 1

285 |

286 | ; Default force kind. May be freeze, drive, deposit, or default

287 | ; or in other terms, fixed, wired, or charged.

288 | ; A value of "default" will use the signal kind to determine the

289 | ; force kind, drive for resolved signals, freeze for unresolved signals

290 | ; DefaultForceKind = freeze

291 |

292 | ; If zero, open files when elaborated; otherwise, open files on

293 | ; first read or write. Default is 0.

294 | ; DelayFileOpen = 1

295 |

296 | ; Control VHDL files opened for write.

297 | ; 0 = Buffered, 1 = Unbuffered

298 | UnbufferedOutput = 0

299 |

300 | ; Control the number of VHDL files open concurrently.

301 | ; This number should always be less than the current ulimit

302 | ; setting for max file descriptors.

303 | ; 0 = unlimited

304 | ConcurrentFileLimit = 40

305 |

306 | ; Control the number of hierarchical regions displayed as

307 | ; part of a signal name shown in the Wave window.

308 | ; A value of zero tells VSIM to display the full name.

309 | ; The default is 0.

310 | ; WaveSignalNameWidth = 0

311 |

312 | ; Turn off warnings from the std_logic_arith, std_logic_unsigned

313 | ; and std_logic_signed packages.

314 | ; StdArithNoWarnings = 1

315 |

316 | ; Turn off warnings from the IEEE numeric_std and numeric_bit packages.

317 | ; NumericStdNoWarnings = 1

318 |

319 | ; Control the format of the (VHDL) FOR generate statement label

320 | ; for each iteration. Do not quote it.

321 | ; The format string here must contain the conversion codes %s and %d,

322 | ; in that order, and no other conversion codes. The %s represents

323 | ; the generate_label; the %d represents the generate parameter value

324 | ; at a particular generate iteration (this is the position number if

325 | ; the generate parameter is of an enumeration type). Embedded whitespace

326 | ; is allowed (but discouraged); leading and trailing whitespace is ignored.

327 | ; Application of the format must result in a unique scope name over all

328 | ; such names in the design so that name lookup can function properly.

329 | ; GenerateFormat = %s__%d

330 |

331 | ; Specify whether checkpoint files should be compressed.

332 | ; The default is 1 (compressed).

333 | ; CheckpointCompressMode = 0

334 |

335 | ; List of dynamically loaded objects for Verilog PLI applications

336 | ; Veriuser = veriuser.sl

337 |

338 | ; Specify default options for the restart command. Options can be one

339 | ; or more of: -force -nobreakpoint -nolist -nolog -nowave

340 | ; DefaultRestartOptions = -force

341 |

342 | ; HP-UX 10.20 ONLY - Enable memory locking to speed up large designs

343 | ; (> 500 megabyte memory footprint). Default is disabled.

344 | ; Specify number of megabytes to lock.

345 | ; LockedMemory = 1000

346 |

347 | ; Turn on (1) or off (0) WLF file compression.

348 | ; The default is 1 (compress WLF file).

349 | ; WLFCompress = 0

350 |

351 | ; Specify whether to save all design hierarchy (1) in the WLF file

352 | ; or only regions containing logged signals (0).

353 | ; The default is 0 (save only regions with logged signals).

354 | ; WLFSaveAllRegions = 1

355 |

356 | ; WLF file time limit. Limit WLF file by time, as closely as possible,

357 | ; to the specified amount of simulation time. When the limit is exceeded

358 | ; the earliest times get truncated from the file.

359 | ; If both time and size limits are specified the most restrictive is used.

360 | ; UserTimeUnits are used if time units are not specified.

361 | ; The default is 0 (no limit). Example: WLFTimeLimit = {100 ms}

362 | ; WLFTimeLimit = 0

363 |

364 | ; WLF file size limit. Limit WLF file size, as closely as possible,

365 | ; to the specified number of megabytes. If both time and size limits

366 | ; are specified then the most restrictive is used.

367 | ; The default is 0 (no limit).

368 | ; WLFSizeLimit = 1000

369 |

370 | ; Specify whether or not a WLF file should be deleted when the

371 | ; simulation ends. A value of 1 will cause the WLF file to be deleted.

372 | ; The default is 0 (do not delete WLF file when simulation ends).

373 | ; WLFDeleteOnQuit = 1

374 |

375 | ; Automatic SDF compilation

376 | ; Disables automatic compilation of SDF files in flows that support it.

377 | ; Default is on, uncomment to turn off.

378 | ; NoAutoSDFCompile = 1

379 |

380 | [lmc]

381 |

382 | [msg_system]

383 | ; Change a message severity or suppress a message.

384 | ; The format is: = [,...]

385 | ; Examples:

386 | ; note = 3009

387 | ; warning = 3033

388 | ; error = 3010,3016

389 | ; fatal = 3016,3033

390 | ; suppress = 3009,3016,3043

391 | ; The command verror can be used to get the complete

392 | ; description of a message.

393 |

394 | ; Control transcripting of elaboration/runtime messages.

395 | ; The default is to have messages appear in the transcript and

396 | ; recorded in the wlf file (messages that are recorded in the

397 | ; wlf file can be viewed in the MsgViewer). The other settings

398 | ; are to send messages only to the transcript or only to the

399 | ; wlf file. The valid values are

400 | ; both {default}

401 | ; tran {transcript only}

402 | ; wlf {wlf file only}

403 | ; msgmode = both

404 | [Project]

405 | ; Warning -- Do not edit the project properties directly.

406 | ; Property names are dynamic in nature and property

407 | ; values have special syntax. Changing property data directly

408 | ; can result in a corrupt MPF file. All project properties

409 | ; can be modified through project window dialogs.

410 | Project_Version = 6

411 | Project_DefaultLib = work

412 | Project_SortMethod = unused

413 | Project_Files_Count = 5

414 | Project_File_0 = D:/Alphy/Doc/GitHub/SimpleCache/Completed/testbench2.v

415 | Project_File_P_0 = cover_toggle 0 vlog_protect 0 file_type verilog group_id 0 cover_exttoggle 0 cover_nofec 0 cover_cond 0 vlog_1995compat 0 vlog_nodebug 0 vlog_noload 0 cover_branch 0 folder {Top Level} last_compile 1541601521 cover_fsm 0 cover_excludedefault 0 vlog_enable0In 0 vlog_disableopt 0 cover_covercells 0 voptflow 1 cover_optlevel 3 vlog_showsource 0 vlog_hazard 0 toggle - vlog_0InOptions {} ood 0 cover_noshort 0 vlog_upper 0 compile_to work vlog_options {} compile_order 2 cover_expr 0 dont_compile 0 cover_stmt 0

416 | Project_File_1 = D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache.v

417 | Project_File_P_1 = cover_toggle 0 vlog_protect 0 file_type verilog group_id 0 cover_exttoggle 0 cover_nofec 0 cover_cond 0 vlog_1995compat 0 vlog_nodebug 0 cover_fsm 0 cover_branch 0 vlog_noload 0 last_compile 1541601388 folder {Top Level} cover_excludedefault 0 vlog_enable0In 0 vlog_disableopt 0 cover_covercells 0 voptflow 1 cover_optlevel 3 vlog_showsource 0 vlog_hazard 0 toggle - vlog_0InOptions {} ood 0 cover_noshort 0 vlog_upper 0 compile_to work vlog_options {} compile_order 4 cover_expr 0 dont_compile 0 cover_stmt 0

418 | Project_File_2 = D:/Alphy/Doc/GitHub/SimpleCache/Completed/ram.v

419 | Project_File_P_2 = cover_toggle 0 vlog_protect 0 file_type verilog group_id 0 cover_exttoggle 0 cover_nofec 0 cover_cond 0 vlog_1995compat 0 vlog_nodebug 0 vlog_noload 0 last_compile 1541598700 folder {Top Level} cover_branch 0 cover_fsm 0 vlog_enable0In 0 cover_excludedefault 0 vlog_disableopt 0 cover_covercells 0 vlog_hazard 0 vlog_showsource 0 cover_optlevel 3 voptflow 1 ood 0 vlog_0InOptions {} toggle - vlog_options {} compile_to work vlog_upper 0 cover_noshort 0 compile_order 0 dont_compile 0 cover_expr 0 cover_stmt 0

420 | Project_File_3 = D:/Alphy/Doc/GitHub/SimpleCache/Completed/testbench.v

421 | Project_File_P_3 = cover_toggle 0 vlog_protect 0 file_type verilog group_id 0 cover_exttoggle 0 cover_nofec 0 cover_cond 0 vlog_1995compat 0 vlog_nodebug 0 vlog_noload 0 last_compile 1541600884 folder {Top Level} cover_branch 0 cover_fsm 0 vlog_enable0In 0 cover_excludedefault 0 vlog_disableopt 0 cover_covercells 0 vlog_hazard 0 vlog_showsource 0 cover_optlevel 3 voptflow 1 ood 0 vlog_0InOptions {} toggle - vlog_options {} compile_to work vlog_upper 0 cover_noshort 0 compile_order 1 dont_compile 0 cover_expr 0 cover_stmt 0

422 | Project_File_4 = D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_and_ram.v

423 | Project_File_P_4 = cover_toggle 0 vlog_protect 0 file_type verilog group_id 0 cover_exttoggle 0 cover_nofec 0 cover_cond 0 vlog_1995compat 0 vlog_nodebug 0 folder {Top Level} last_compile 1541601377 cover_fsm 0 cover_branch 0 vlog_noload 0 vlog_enable0In 0 cover_excludedefault 0 vlog_disableopt 0 cover_covercells 0 vlog_hazard 0 vlog_showsource 0 cover_optlevel 3 voptflow 1 ood 0 vlog_0InOptions {} toggle - vlog_options {} compile_to work vlog_upper 0 cover_noshort 0 compile_order 3 dont_compile 0 cover_expr 0 cover_stmt 0

424 | Project_Sim_Count = 0

425 | Project_Folder_Count = 0

426 | Echo_Compile_Output = 0

427 | Save_Compile_Report = 1

428 | Project_Opt_Count = 0

429 | ForceSoftPaths = 0

430 | ProjectStatusDelay = 5000

431 | VERILOG_DoubleClick = Edit

432 | VERILOG_CustomDoubleClick =

433 | SYSTEMVERILOG_DoubleClick = Edit

434 | SYSTEMVERILOG_CustomDoubleClick =

435 | VHDL_DoubleClick = Edit

436 | VHDL_CustomDoubleClick =

437 | PSL_DoubleClick = Edit

438 | PSL_CustomDoubleClick =

439 | TEXT_DoubleClick = Edit

440 | TEXT_CustomDoubleClick =

441 | SYSTEMC_DoubleClick = Edit

442 | SYSTEMC_CustomDoubleClick =

443 | TCL_DoubleClick = Edit

444 | TCL_CustomDoubleClick =

445 | MACRO_DoubleClick = Edit

446 | MACRO_CustomDoubleClick =

447 | VCD_DoubleClick = Edit

448 | VCD_CustomDoubleClick =

449 | SDF_DoubleClick = Edit

450 | SDF_CustomDoubleClick =

451 | XML_DoubleClick = Edit

452 | XML_CustomDoubleClick =

453 | LOGFILE_DoubleClick = Edit

454 | LOGFILE_CustomDoubleClick =

455 | UCDB_DoubleClick = Edit

456 | UCDB_CustomDoubleClick =

457 | TDB_DoubleClick = Edit

458 | TDB_CustomDoubleClick =

459 | UPF_DoubleClick = Edit

460 | UPF_CustomDoubleClick =

461 | PCF_DoubleClick = Edit

462 | PCF_CustomDoubleClick =

463 | PROJECT_DoubleClick = Edit

464 | PROJECT_CustomDoubleClick =

465 | VRM_DoubleClick = Edit

466 | VRM_CustomDoubleClick =

467 | DEBUGDATABASE_DoubleClick = Edit

468 | DEBUGDATABASE_CustomDoubleClick =

469 | DEBUGARCHIVE_DoubleClick = Edit

470 | DEBUGARCHIVE_CustomDoubleClick =

471 | Project_Major_Version = 10

472 | Project_Minor_Version = 5

473 |

--------------------------------------------------------------------------------

73 | ---

74 |

75 | ###Cache and RAM module:

76 |

77 | ```verilog

78 | module cache_and_ram(

79 | input [31:0] address,

80 | input [31:0] data,

81 | input clk,

82 | input mode,

83 | output [31:0] out

84 | );

85 |

86 | //previous values

87 | reg [31:0] prev_address, prev_data;

88 | reg prev_mode;

89 | reg [31:0] temp_out;

90 |

91 | reg [cache.index_size - 1:0] index; // for keeping index of current address

92 | reg [11 - cache.index_size:0] tag; // for keeping tag of ceurrent address

93 |

94 | ram ram();

95 | cache cache();

96 |

97 | initial

98 | begin

99 | index = 0;

100 | tag = 0;

101 | prev_address = 0;

102 | prev_data = 0;

103 | prev_mode = 0;

104 | end

105 |

106 | always @(edge clk)

107 | begin

108 | //check if the new input is updated

109 | if (prev_address != address || prev_data != data || prev_mode != mode)

110 | begin

111 | prev_address = address % ram.size;

112 | prev_data = data;

113 | prev_mode = mode;

114 |

115 | tag = prev_address >> cache.index_size; // tag = first bits of address except index ones (In our particular case - 6)

116 | index = address % cache.size; // index value = last n (n = size of cache) bits of address

117 |

118 | if (mode == 1)

119 | begin

120 | ram.ram[prev_address] = data;

121 | //write new data to the relevant cache block if there is such one

122 | if (cache.valid_array[index] == 1 && cache.tag_array[index] == tag)

123 | cache.cache[index] = data;

124 | end

125 | else

126 | begin

127 | //write new data to the relevant cache's block, because the one we addressing to will be possibly addressed one more time soon

128 | if (cache.valid_array[index] != 1 || cache.tag_array[index] != tag)

129 | begin

130 | cache.valid_array[index] = 1;

131 | cache.tag_array[index] = tag;

132 | cache.cache[index] = ram.ram[prev_address];

133 | end

134 | temp_out = cache.cache[index];

135 | end

136 | end

137 | end

138 |

139 | assign out = temp_out;

140 |

141 | endmodule

142 | ```

143 |

144 |

145 |

--------------------------------------------------------------------------------

/Completed/work/_info:

--------------------------------------------------------------------------------

1 | m255

2 | K4

3 | z2

4 | 13

5 | !s112 1.1

6 | !i10d 8192

7 | !i10e 25

8 | !i10f 100

9 | cModel Technology

10 | dC:/intelFPGA_lite/18.0

11 | vcache

12 | Z0 !s110 1541601841

13 | !i10b 1

14 | !s100 AM?Kj>YPoQbPh@O5HzlJz1

15 | Ik:X?bcd9RU`eaPG2^lFQ>3

16 | Z1 VDg1SIo80bB@j0V0VzS_@n1

17 | Z2 dD:/Alphy/Doc/GitHub/SimpleCache/Completed

18 | w1541601388

19 | 8D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache.v

20 | FD:/Alphy/Doc/GitHub/SimpleCache/Completed/cache.v

21 | L0 1

22 | Z3 OV;L;10.5b;63

23 | r1

24 | !s85 0

25 | 31

26 | Z4 !s108 1541601841.000000

27 | !s107 D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache.v|

28 | !s90 -reportprogress|300|-work|work|-stats=none|D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache.v|

29 | !i113 1

30 | Z5 o-work work

31 | Z6 tCvgOpt 0

32 | vcache_and_ram

33 | R0

34 | !i10b 1

35 | !s100 Nc:T^JLco77jjQieUD7KI1

36 | Io@TdV>O?9b`44WfK7m3DNc]D_^0

58 | R1

59 | R2

60 | w1541343442

61 | 8D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_and_ram_clever_tb.v

62 | FD:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_and_ram_clever_tb.v

63 | L0 1

64 | R3

65 | r1

66 | !s85 0

67 | 31

68 | Z8 !s108 1541601665.000000

69 | !s107 D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_and_ram_clever_tb.v|

70 | !s90 -reportprogress|300|-work|work|-stats=none|D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_and_ram_clever_tb.v|

71 | !i113 1

72 | R5

73 | R6

74 | vcache_and_ram_tb

75 | Z9 !s110 1541600898

76 | !i10b 1

77 | !s100 11eVoEgSlk5GNZn<0j12THL^VB4E8OY2

121 | R1

122 | R2

123 | w1541600591

124 | 8D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode.v

125 | FD:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode.v

126 | L0 1

127 | R3

128 | r1

129 | !s85 0

130 | 31

131 | !s108 1541601310.000000

132 | !s107 D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode.v|

133 | !s90 -reportprogress|300|-work|work|-stats=none|D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode.v|

134 | !i113 1

135 | R5

136 | R6

137 | vcache_no_mode_clever

138 | !s110 1541601666

139 | !i10b 1

140 | !s100 D[^Q^C=lVDa47<3JZEQ`L0

141 | ICD03[[8oi9<3:z<]_]UY>0

142 | R1

143 | R2

144 | w1541344294

145 | 8D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode_clever.v

146 | FD:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode_clever.v

147 | L0 1

148 | R3

149 | r1

150 | !s85 0

151 | 31

152 | !s108 1541601666.000000

153 | !s107 D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode_clever.v|

154 | !s90 -reportprogress|300|-work|work|-stats=none|D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache_no_mode_clever.v|

155 | !i113 1

156 | R5

157 | R6

158 | vram

159 | R0

160 | !i10b 1

161 | !s100 mY;G_1fYOo`4JBPMTLMB?3

162 | I1bg9H6fnDhR>EZ[h1>`BJ3

163 | R1

164 | R2

165 | w1541598700

166 | 8D:/Alphy/Doc/GitHub/SimpleCache/Completed/ram.v

167 | FD:/Alphy/Doc/GitHub/SimpleCache/Completed/ram.v

168 | L0 1

169 | R3

170 | r1

171 | !s85 0

172 | 31

173 | R4

174 | !s107 D:/Alphy/Doc/GitHub/SimpleCache/Completed/ram.v|

175 | !s90 -reportprogress|300|-work|work|-stats=none|D:/Alphy/Doc/GitHub/SimpleCache/Completed/ram.v|

176 | !i113 1

177 | R5

178 | R6

179 | vram_clever

180 | R7

181 | !i10b 1

182 | !s100 _d>z=zSmXV=cea0TP2^`32

183 | IM?jOUE^70hkj0Gh>EcbJa0

184 | R1

185 | R2

186 | w1541339652

187 | 8D:/Alphy/Doc/GitHub/SimpleCache/Completed/ram_clever.v

188 | FD:/Alphy/Doc/GitHub/SimpleCache/Completed/ram_clever.v

189 | L0 1

190 | R3

191 | r1

192 | !s85 0

193 | 31

194 | R8

195 | !s107 D:/Alphy/Doc/GitHub/SimpleCache/Completed/ram_clever.v|

196 | !s90 -reportprogress|300|-work|work|-stats=none|D:/Alphy/Doc/GitHub/SimpleCache/Completed/ram_clever.v|

197 | !i113 1

198 | R5

199 | R6

200 | vram_tb

201 | R11

202 | !i10b 1

203 | !s100 gTl]^[52Xfo2g50d9b1eX;ml_ioQ2n4z@D2

268 | R1

269 | R2

270 | w1541343988

271 | 8D:/Alphy/Doc/GitHub/SimpleCache/Completed/testbench_for_clevers.v

272 | FD:/Alphy/Doc/GitHub/SimpleCache/Completed/testbench_for_clevers.v

273 | L0 1

274 | R3

275 | r1

276 | !s85 0

277 | 31

278 | R10

279 | !s107 D:/Alphy/Doc/GitHub/SimpleCache/Completed/testbench_for_clevers.v|

280 | !s90 -reportprogress|300|-work|work|-stats=none|D:/Alphy/Doc/GitHub/SimpleCache/Completed/testbench_for_clevers.v|

281 | !i113 1

282 | R5

283 | R6

284 |

--------------------------------------------------------------------------------

/Completed/Completed parts.mpf:

--------------------------------------------------------------------------------

1 | ; Copyright 1991-2009 Mentor Graphics Corporation

2 | ;

3 | ; All Rights Reserved.

4 | ;

5 | ; THIS WORK CONTAINS TRADE SECRET AND PROPRIETARY INFORMATION WHICH IS THE PROPERTY OF

6 | ; MENTOR GRAPHICS CORPORATION OR ITS LICENSORS AND IS SUBJECT TO LICENSE TERMS.

7 | ;

8 |

9 | [Library]

10 | std = $MODEL_TECH/../std

11 | ieee = $MODEL_TECH/../ieee

12 | verilog = $MODEL_TECH/../verilog

13 | vital2000 = $MODEL_TECH/../vital2000

14 | std_developerskit = $MODEL_TECH/../std_developerskit

15 | synopsys = $MODEL_TECH/../synopsys

16 | modelsim_lib = $MODEL_TECH/../modelsim_lib

17 | sv_std = $MODEL_TECH/../sv_std

18 |

19 | ; Altera Primitive libraries

20 | ;

21 | ; VHDL Section

22 | ;

23 | altera_mf = $MODEL_TECH/../altera/vhdl/altera_mf

24 | altera = $MODEL_TECH/../altera/vhdl/altera

25 | altera_lnsim = $MODEL_TECH/../altera/vhdl/altera_lnsim

26 | lpm = $MODEL_TECH/../altera/vhdl/220model

27 | 220model = $MODEL_TECH/../altera/vhdl/220model

28 | maxii = $MODEL_TECH/../altera/vhdl/maxii

29 | maxv = $MODEL_TECH/../altera/vhdl/maxv

30 | fiftyfivenm = $MODEL_TECH/../altera/vhdl/fiftyfivenm

31 | sgate = $MODEL_TECH/../altera/vhdl/sgate

32 | arriaii = $MODEL_TECH/../altera/vhdl/arriaii

33 | arriaii_hssi = $MODEL_TECH/../altera/vhdl/arriaii_hssi

34 | arriaii_pcie_hip = $MODEL_TECH/../altera/vhdl/arriaii_pcie_hip

35 | arriaiigz = $MODEL_TECH/../altera/vhdl/arriaiigz

36 | arriaiigz_hssi = $MODEL_TECH/../altera/vhdl/arriaiigz_hssi

37 | arriaiigz_pcie_hip = $MODEL_TECH/../altera/vhdl/arriaiigz_pcie_hip

38 | stratixiv = $MODEL_TECH/../altera/vhdl/stratixiv

39 | stratixiv_hssi = $MODEL_TECH/../altera/vhdl/stratixiv_hssi

40 | stratixiv_pcie_hip = $MODEL_TECH/../altera/vhdl/stratixiv_pcie_hip

41 | cycloneiv = $MODEL_TECH/../altera/vhdl/cycloneiv

42 | cycloneiv_hssi = $MODEL_TECH/../altera/vhdl/cycloneiv_hssi

43 | cycloneiv_pcie_hip = $MODEL_TECH/../altera/vhdl/cycloneiv_pcie_hip

44 | cycloneive = $MODEL_TECH/../altera/vhdl/cycloneive

45 | stratixv = $MODEL_TECH/../altera/vhdl/stratixv

46 | stratixv_hssi = $MODEL_TECH/../altera/vhdl/stratixv_hssi

47 | stratixv_pcie_hip = $MODEL_TECH/../altera/vhdl/stratixv_pcie_hip

48 | arriavgz = $MODEL_TECH/../altera/vhdl/arriavgz

49 | arriavgz_hssi = $MODEL_TECH/../altera/vhdl/arriavgz_hssi

50 | arriavgz_pcie_hip = $MODEL_TECH/../altera/vhdl/arriavgz_pcie_hip

51 | arriav = $MODEL_TECH/../altera/vhdl/arriav

52 | cyclonev = $MODEL_TECH/../altera/vhdl/cyclonev

53 | twentynm = $MODEL_TECH/../altera/vhdl/twentynm

54 | twentynm_hssi = $MODEL_TECH/../altera/vhdl/twentynm_hssi

55 | twentynm_hip = $MODEL_TECH/../altera/vhdl/twentynm_hip

56 | cyclone10lp = $MODEL_TECH/../altera/vhdl/cyclone10lp

57 | ;

58 | ; Verilog Section

59 | ;

60 | altera_mf_ver = $MODEL_TECH/../altera/verilog/altera_mf

61 | altera_ver = $MODEL_TECH/../altera/verilog/altera

62 | altera_lnsim_ver = $MODEL_TECH/../altera/verilog/altera_lnsim

63 | lpm_ver = $MODEL_TECH/../altera/verilog/220model

64 | 220model_ver = $MODEL_TECH/../altera/verilog/220model

65 | maxii_ver = $MODEL_TECH/../altera/verilog/maxii

66 | maxv_ver = $MODEL_TECH/../altera/verilog/maxv

67 | fiftyfivenm_ver = $MODEL_TECH/../altera/verilog/fiftyfivenm

68 | sgate_ver = $MODEL_TECH/../altera/verilog/sgate

69 | arriaii_ver = $MODEL_TECH/../altera/verilog/arriaii

70 | arriaii_hssi_ver = $MODEL_TECH/../altera/verilog/arriaii_hssi

71 | arriaii_pcie_hip_ver = $MODEL_TECH/../altera/verilog/arriaii_pcie_hip

72 | arriaiigz_ver = $MODEL_TECH/../altera/verilog/arriaiigz

73 | arriaiigz_hssi_ver = $MODEL_TECH/../altera/verilog/arriaiigz_hssi

74 | arriaiigz_pcie_hip_ver = $MODEL_TECH/../altera/verilog/arriaiigz_pcie_hip

75 | stratixiv_ver = $MODEL_TECH/../altera/verilog/stratixiv

76 | stratixiv_hssi_ver = $MODEL_TECH/../altera/verilog/stratixiv_hssi

77 | stratixiv_pcie_hip_ver = $MODEL_TECH/../altera/verilog/stratixiv_pcie_hip

78 | stratixv_ver = $MODEL_TECH/../altera/verilog/stratixv

79 | stratixv_hssi_ver = $MODEL_TECH/../altera/verilog/stratixv_hssi

80 | stratixv_pcie_hip_ver = $MODEL_TECH/../altera/verilog/stratixv_pcie_hip

81 | arriavgz_ver = $MODEL_TECH/../altera/verilog/arriavgz

82 | arriavgz_hssi_ver = $MODEL_TECH/../altera/verilog/arriavgz_hssi

83 | arriavgz_pcie_hip_ver = $MODEL_TECH/../altera/verilog/arriavgz_pcie_hip

84 | arriav_ver = $MODEL_TECH/../altera/verilog/arriav

85 | arriav_hssi_ver = $MODEL_TECH/../altera/verilog/arriav_hssi

86 | arriav_pcie_hip_ver = $MODEL_TECH/../altera/verilog/arriav_pcie_hip

87 | cyclonev_ver = $MODEL_TECH/../altera/verilog/cyclonev

88 | cyclonev_hssi_ver = $MODEL_TECH/../altera/verilog/cyclonev_hssi

89 | cyclonev_pcie_hip_ver = $MODEL_TECH/../altera/verilog/cyclonev_pcie_hip

90 | cycloneiv_ver = $MODEL_TECH/../altera/verilog/cycloneiv

91 | cycloneiv_hssi_ver = $MODEL_TECH/../altera/verilog/cycloneiv_hssi

92 | cycloneiv_pcie_hip_ver = $MODEL_TECH/../altera/verilog/cycloneiv_pcie_hip

93 | cycloneive_ver = $MODEL_TECH/../altera/verilog/cycloneive

94 | twentynm_ver = $MODEL_TECH/../altera/verilog/twentynm

95 | twentynm_hssi_ver = $MODEL_TECH/../altera/verilog/twentynm_hssi

96 | twentynm_hip_ver = $MODEL_TECH/../altera/verilog/twentynm_hip

97 | cyclone10lp_ver = $MODEL_TECH/../altera/verilog/cyclone10lp

98 |

99 | work = work

100 | [vcom]

101 | ; VHDL93 variable selects language version as the default.

102 | ; Default is VHDL-2002.

103 | ; Value of 0 or 1987 for VHDL-1987.

104 | ; Value of 1 or 1993 for VHDL-1993.

105 | ; Default or value of 2 or 2002 for VHDL-2002.

106 | ; Default or value of 3 or 2008 for VHDL-2008.

107 | VHDL93 = 2002

108 |

109 | ; Show source line containing error. Default is off.

110 | ; Show_source = 1

111 |

112 | ; Turn off unbound-component warnings. Default is on.

113 | ; Show_Warning1 = 0

114 |

115 | ; Turn off process-without-a-wait-statement warnings. Default is on.

116 | ; Show_Warning2 = 0

117 |

118 | ; Turn off null-range warnings. Default is on.

119 | ; Show_Warning3 = 0

120 |

121 | ; Turn off no-space-in-time-literal warnings. Default is on.

122 | ; Show_Warning4 = 0

123 |

124 | ; Turn off multiple-drivers-on-unresolved-signal warnings. Default is on.

125 | ; Show_Warning5 = 0

126 |

127 | ; Turn off optimization for IEEE std_logic_1164 package. Default is on.

128 | ; Optimize_1164 = 0

129 |

130 | ; Turn on resolving of ambiguous function overloading in favor of the

131 | ; "explicit" function declaration (not the one automatically created by

132 | ; the compiler for each type declaration). Default is off.

133 | ; The .ini file has Explicit enabled so that std_logic_signed/unsigned

134 | ; will match the behavior of synthesis tools.

135 | Explicit = 1

136 |

137 | ; Turn off acceleration of the VITAL packages. Default is to accelerate.

138 | ; NoVital = 1

139 |

140 | ; Turn off VITAL compliance checking. Default is checking on.

141 | ; NoVitalCheck = 1

142 |

143 | ; Ignore VITAL compliance checking errors. Default is to not ignore.

144 | ; IgnoreVitalErrors = 1

145 |

146 | ; Turn off VITAL compliance checking warnings. Default is to show warnings.

147 | ; Show_VitalChecksWarnings = 0

148 |

149 | ; Keep silent about case statement static warnings.

150 | ; Default is to give a warning.

151 | ; NoCaseStaticError = 1

152 |

153 | ; Keep silent about warnings caused by aggregates that are not locally static.

154 | ; Default is to give a warning.

155 | ; NoOthersStaticError = 1

156 |

157 | ; Turn off inclusion of debugging info within design units.

158 | ; Default is to include debugging info.

159 | ; NoDebug = 1

160 |

161 | ; Turn off "Loading..." messages. Default is messages on.

162 | ; Quiet = 1

163 |

164 | ; Turn on some limited synthesis rule compliance checking. Checks only:

165 | ; -- signals used (read) by a process must be in the sensitivity list

166 | ; CheckSynthesis = 1

167 |

168 | ; Activate optimizations on expressions that do not involve signals,

169 | ; waits, or function/procedure/task invocations. Default is off.

170 | ; ScalarOpts = 1

171 |

172 | ; Require the user to specify a configuration for all bindings,

173 | ; and do not generate a compile time default binding for the

174 | ; component. This will result in an elaboration error of

175 | ; 'component not bound' if the user fails to do so. Avoids the rare

176 | ; issue of a false dependency upon the unused default binding.

177 | ; RequireConfigForAllDefaultBinding = 1

178 |

179 | ; Inhibit range checking on subscripts of arrays. Range checking on

180 | ; scalars defined with subtypes is inhibited by default.

181 | ; NoIndexCheck = 1

182 |

183 | ; Inhibit range checks on all (implicit and explicit) assignments to

184 | ; scalar objects defined with subtypes.

185 | ; NoRangeCheck = 1

186 |

187 | [vlog]

188 |

189 | ; Turn off inclusion of debugging info within design units.

190 | ; Default is to include debugging info.

191 | ; NoDebug = 1

192 |

193 | ; Turn off "loading..." messages. Default is messages on.

194 | ; Quiet = 1

195 |

196 | ; Turn on Verilog hazard checking (order-dependent accessing of global vars).

197 | ; Default is off.

198 | ; Hazard = 1

199 |

200 | ; Turn on converting regular Verilog identifiers to uppercase. Allows case

201 | ; insensitivity for module names. Default is no conversion.

202 | ; UpCase = 1

203 |

204 | ; Turn on incremental compilation of modules. Default is off.

205 | ; Incremental = 1

206 |

207 | ; Turns on lint-style checking.

208 | ; Show_Lint = 1

209 |

210 | [vsim]

211 | ; Simulator resolution

212 | ; Set to fs, ps, ns, us, ms, or sec with optional prefix of 1, 10, or 100.

213 | Resolution = ps

214 |

215 | ; User time unit for run commands

216 | ; Set to default, fs, ps, ns, us, ms, or sec. The default is to use the

217 | ; unit specified for Resolution. For example, if Resolution is 100ps,

218 | ; then UserTimeUnit defaults to ps.

219 | ; Should generally be set to default.

220 | UserTimeUnit = default

221 |

222 | ; Default run length

223 | RunLength = 27012000011 ns

224 |

225 | ; Maximum iterations that can be run without advancing simulation time

226 | IterationLimit = 10000000

227 |

228 | ; Directive to license manager:

229 | ; vhdl Immediately reserve a VHDL license

230 | ; vlog Immediately reserve a Verilog license

231 | ; plus Immediately reserve a VHDL and Verilog license

232 | ; nomgc Do not look for Mentor Graphics Licenses

233 | ; nomti Do not look for Model Technology Licenses

234 | ; noqueue Do not wait in the license queue when a license isn't available

235 | ; viewsim Try for viewer license but accept simulator license(s) instead

236 | ; of queuing for viewer license

237 | ; License = plus

238 |

239 | ; Stop the simulator after a VHDL/Verilog assertion message

240 | ; 0 = Note 1 = Warning 2 = Error 3 = Failure 4 = Fatal

241 | BreakOnAssertion = 3

242 |

243 | ; Assertion Message Format

244 | ; %S - Severity Level

245 | ; %R - Report Message

246 | ; %T - Time of assertion

247 | ; %D - Delta

248 | ; %I - Instance or Region pathname (if available)

249 | ; %% - print '%' character

250 | ; AssertionFormat = "** %S: %R\n Time: %T Iteration: %D%I\n"

251 |

252 | ; Assertion File - alternate file for storing VHDL/Verilog assertion messages

253 | ; AssertFile = assert.log

254 |

255 | ; Default radix for all windows and commands...

256 | ; Set to symbolic, ascii, binary, octal, decimal, hex, unsigned

257 | DefaultRadix = symbolic

258 |

259 | ; VSIM Startup command

260 | ; Startup = do startup.do

261 |

262 | ; File for saving command transcript

263 | TranscriptFile = transcript

264 |

265 | ; File for saving command history

266 | ; CommandHistory = cmdhist.log

267 |

268 | ; Specify whether paths in simulator commands should be described

269 | ; in VHDL or Verilog format.

270 | ; For VHDL, PathSeparator = /

271 | ; For Verilog, PathSeparator = .

272 | ; Must not be the same character as DatasetSeparator.

273 | PathSeparator = /

274 |

275 | ; Specify the dataset separator for fully rooted contexts.

276 | ; The default is ':'. For example, sim:/top

277 | ; Must not be the same character as PathSeparator.

278 | DatasetSeparator = :

279 |

280 | ; Disable VHDL assertion messages

281 | ; IgnoreNote = 1

282 | ; IgnoreWarning = 1

283 | ; IgnoreError = 1

284 | ; IgnoreFailure = 1

285 |

286 | ; Default force kind. May be freeze, drive, deposit, or default

287 | ; or in other terms, fixed, wired, or charged.

288 | ; A value of "default" will use the signal kind to determine the

289 | ; force kind, drive for resolved signals, freeze for unresolved signals

290 | ; DefaultForceKind = freeze

291 |

292 | ; If zero, open files when elaborated; otherwise, open files on

293 | ; first read or write. Default is 0.

294 | ; DelayFileOpen = 1

295 |

296 | ; Control VHDL files opened for write.

297 | ; 0 = Buffered, 1 = Unbuffered

298 | UnbufferedOutput = 0

299 |

300 | ; Control the number of VHDL files open concurrently.

301 | ; This number should always be less than the current ulimit

302 | ; setting for max file descriptors.

303 | ; 0 = unlimited

304 | ConcurrentFileLimit = 40

305 |

306 | ; Control the number of hierarchical regions displayed as

307 | ; part of a signal name shown in the Wave window.

308 | ; A value of zero tells VSIM to display the full name.

309 | ; The default is 0.

310 | ; WaveSignalNameWidth = 0

311 |

312 | ; Turn off warnings from the std_logic_arith, std_logic_unsigned

313 | ; and std_logic_signed packages.

314 | ; StdArithNoWarnings = 1

315 |

316 | ; Turn off warnings from the IEEE numeric_std and numeric_bit packages.

317 | ; NumericStdNoWarnings = 1

318 |

319 | ; Control the format of the (VHDL) FOR generate statement label

320 | ; for each iteration. Do not quote it.

321 | ; The format string here must contain the conversion codes %s and %d,

322 | ; in that order, and no other conversion codes. The %s represents

323 | ; the generate_label; the %d represents the generate parameter value

324 | ; at a particular generate iteration (this is the position number if

325 | ; the generate parameter is of an enumeration type). Embedded whitespace

326 | ; is allowed (but discouraged); leading and trailing whitespace is ignored.

327 | ; Application of the format must result in a unique scope name over all

328 | ; such names in the design so that name lookup can function properly.

329 | ; GenerateFormat = %s__%d

330 |

331 | ; Specify whether checkpoint files should be compressed.

332 | ; The default is 1 (compressed).

333 | ; CheckpointCompressMode = 0

334 |

335 | ; List of dynamically loaded objects for Verilog PLI applications

336 | ; Veriuser = veriuser.sl

337 |

338 | ; Specify default options for the restart command. Options can be one

339 | ; or more of: -force -nobreakpoint -nolist -nolog -nowave

340 | ; DefaultRestartOptions = -force

341 |

342 | ; HP-UX 10.20 ONLY - Enable memory locking to speed up large designs

343 | ; (> 500 megabyte memory footprint). Default is disabled.

344 | ; Specify number of megabytes to lock.

345 | ; LockedMemory = 1000

346 |

347 | ; Turn on (1) or off (0) WLF file compression.

348 | ; The default is 1 (compress WLF file).

349 | ; WLFCompress = 0

350 |

351 | ; Specify whether to save all design hierarchy (1) in the WLF file

352 | ; or only regions containing logged signals (0).

353 | ; The default is 0 (save only regions with logged signals).

354 | ; WLFSaveAllRegions = 1

355 |

356 | ; WLF file time limit. Limit WLF file by time, as closely as possible,

357 | ; to the specified amount of simulation time. When the limit is exceeded

358 | ; the earliest times get truncated from the file.

359 | ; If both time and size limits are specified the most restrictive is used.

360 | ; UserTimeUnits are used if time units are not specified.

361 | ; The default is 0 (no limit). Example: WLFTimeLimit = {100 ms}

362 | ; WLFTimeLimit = 0

363 |

364 | ; WLF file size limit. Limit WLF file size, as closely as possible,

365 | ; to the specified number of megabytes. If both time and size limits

366 | ; are specified then the most restrictive is used.

367 | ; The default is 0 (no limit).

368 | ; WLFSizeLimit = 1000

369 |

370 | ; Specify whether or not a WLF file should be deleted when the

371 | ; simulation ends. A value of 1 will cause the WLF file to be deleted.

372 | ; The default is 0 (do not delete WLF file when simulation ends).

373 | ; WLFDeleteOnQuit = 1

374 |

375 | ; Automatic SDF compilation

376 | ; Disables automatic compilation of SDF files in flows that support it.

377 | ; Default is on, uncomment to turn off.

378 | ; NoAutoSDFCompile = 1

379 |

380 | [lmc]

381 |

382 | [msg_system]

383 | ; Change a message severity or suppress a message.

384 | ; The format is: = [,...]

385 | ; Examples:

386 | ; note = 3009

387 | ; warning = 3033

388 | ; error = 3010,3016

389 | ; fatal = 3016,3033

390 | ; suppress = 3009,3016,3043

391 | ; The command verror can be used to get the complete

392 | ; description of a message.

393 |

394 | ; Control transcripting of elaboration/runtime messages.

395 | ; The default is to have messages appear in the transcript and

396 | ; recorded in the wlf file (messages that are recorded in the

397 | ; wlf file can be viewed in the MsgViewer). The other settings

398 | ; are to send messages only to the transcript or only to the

399 | ; wlf file. The valid values are

400 | ; both {default}

401 | ; tran {transcript only}

402 | ; wlf {wlf file only}

403 | ; msgmode = both

404 | [Project]

405 | ; Warning -- Do not edit the project properties directly.

406 | ; Property names are dynamic in nature and property

407 | ; values have special syntax. Changing property data directly

408 | ; can result in a corrupt MPF file. All project properties

409 | ; can be modified through project window dialogs.

410 | Project_Version = 6

411 | Project_DefaultLib = work

412 | Project_SortMethod = unused

413 | Project_Files_Count = 5

414 | Project_File_0 = D:/Alphy/Doc/GitHub/SimpleCache/Completed/testbench2.v

415 | Project_File_P_0 = cover_toggle 0 vlog_protect 0 file_type verilog group_id 0 cover_exttoggle 0 cover_nofec 0 cover_cond 0 vlog_1995compat 0 vlog_nodebug 0 vlog_noload 0 cover_branch 0 folder {Top Level} last_compile 1541601521 cover_fsm 0 cover_excludedefault 0 vlog_enable0In 0 vlog_disableopt 0 cover_covercells 0 voptflow 1 cover_optlevel 3 vlog_showsource 0 vlog_hazard 0 toggle - vlog_0InOptions {} ood 0 cover_noshort 0 vlog_upper 0 compile_to work vlog_options {} compile_order 2 cover_expr 0 dont_compile 0 cover_stmt 0

416 | Project_File_1 = D:/Alphy/Doc/GitHub/SimpleCache/Completed/cache.v