9?3

109 | R1

110 | w1631101968

111 | 8D:/comber/ADPLL/source/variableresetrandomwalkfilter.v

112 | FD:/comber/ADPLL/source/variableresetrandomwalkfilter.v

113 | L0 5

114 | R2

115 | r1

116 | 31

117 | R3

118 | R4

119 | !i10b 1

120 | !s100 IVg_1l^[Lfj?nJ=G8kUZT1

121 | !s85 0

122 | !s108 1632394244.088000

123 | !s107 D:/comber/ADPLL/source/variableresetrandomwalkfilter.v|

124 | !s90 -reportprogress|300|-vlog01compat|-work|work|+incdir+D:/comber/ADPLL/source|D:/comber/ADPLL/source/variableresetrandomwalkfilter.v|

125 | !s101 -O0

126 |

--------------------------------------------------------------------------------

/source/phasecomparator.v:

--------------------------------------------------------------------------------

1 | `timescale 1ns / 1ps

2 |

3 | /* phase comparator */

4 |

5 | module phasecomparator(InputSignal, OutputSignal, MainClock, Lead, Lag, InputSignalEdge, OutputSignalEdge, Lock, SynchronousSignal, PeriodCount);

6 |

7 | input MainClock; // System Clock

8 | input InputSignal, OutputSignal; // PLL input(reference) and output(dejittered clock) signals

9 | output SynchronousSignal;

10 | output Lead, Lag; // Lead and Lag signals

11 | output InputSignalEdge, OutputSignalEdge, Lock;

12 | output [7:0] PeriodCount;

13 |

14 | /* D触发器,同步输入信号 */

15 | reg SynchronousSignal;

16 | always @(posedge MainClock)

17 | begin

18 | SynchronousSignal <= InputSignal;

19 | end

20 |

21 | reg [1:0] InputSignalEdgeDet; // detector of the rising edge

22 | always @(posedge MainClock)

23 | begin

24 | #0.001;

25 | InputSignalEdgeDet <= { InputSignalEdgeDet[0], SynchronousSignal };

26 | end

27 |

28 | reg [1:0] OutputSignalEdgeDet; // detector of the rising edge

29 | always @(posedge MainClock)

30 | begin

31 | #0.002;

32 | OutputSignalEdgeDet <= { OutputSignalEdgeDet[0], OutputSignal };

33 | end

34 |

35 | /* this signal checked at rising edge of MainClock. */

36 | /* It's simple detector of the Input signal rising edge - */

37 | /* When it detected then we check the level of the output.*/

38 | /* There is possible to place additional 2 registers for */

39 | /* output signal for eliminatig the cmp. constant phase error */

40 | wire InputSignalEdge = (InputSignalEdgeDet == 2'b01); // InputSignal上升沿

41 | wire InputSignalDownEdge = (InputSignalEdgeDet == 2'b10); // InputSignal下降沿

42 | wire OutputSignalEdge = (OutputSignalEdgeDet == 2'b01); // OutputSignal上升沿

43 |

44 | /* 计算输入信号的频率(时钟周期数) */

45 | reg flag;

46 | reg [7:0] cnt, PeriodCount;

47 | always @(posedge MainClock)

48 | begin

49 | #0.001;

50 | if(flag)

51 | begin

52 | if(SynchronousSignal)

53 | begin

54 | cnt <= cnt + 1;

55 | end

56 | end

57 | end

58 | always @(posedge InputSignalDownEdge)

59 | begin

60 | flag = 1'b0;

61 | PeriodCount <= cnt;

62 | end

63 |

64 | /* "Lead" signal will be generate in case of output==1 during input rising edge*/

65 | reg Lead, Lag; // outputs "Lead", "Lag" are registered

66 | always @(posedge MainClock)

67 | begin

68 | if(Lock)

69 | begin

70 | Lag <= 1'b0;

71 | Lead <= 1'b0;

72 | end

73 | else

74 | begin

75 | #0.001;

76 | Lag <= ((InputSignalEdge == 1'b1) && (OutputSignal == 1'b0));

77 | Lead <= ((InputSignalEdge == 1'b1) && (OutputSignal == 1'b1));

78 | end

79 | end

80 |

81 | reg Lock;

82 | always @(posedge InputSignalEdge)

83 | begin

84 | #0.002;

85 | if(OutputSignalEdge)

86 | Lock <= 1'b1;

87 | else

88 | Lock <= 1'b0;

89 | end

90 |

91 | initial begin

92 | flag <= 1'b1;

93 | Lock <= 1'b0;

94 | cnt <= 8'd0;

95 | PeriodCount <= 8'd0;

96 | OutputSignalEdgeDet <= 2'b00;

97 | InputSignalEdgeDet <= 2'b00;

98 | end

99 |

100 |

101 | endmodule

102 |

--------------------------------------------------------------------------------

/output_files/dpll.asm.rpt:

--------------------------------------------------------------------------------

1 | Assembler report for dpll

2 | Wed Sep 08 19:32:09 2021

3 | Quartus II 64-Bit Version 15.0.0 Build 145 04/22/2015 SJ Full Version

4 |

5 |

6 | ---------------------

7 | ; Table of Contents ;

8 | ---------------------

9 | 1. Legal Notice

10 | 2. Assembler Summary

11 | 3. Assembler Settings

12 | 4. Assembler Generated Files

13 | 5. Assembler Device Options: D:/comber/ADPLL/output_files/dpll.sof

14 | 6. Assembler Messages

15 |

16 |

17 |

18 | ----------------

19 | ; Legal Notice ;

20 | ----------------

21 | Copyright (C) 1991-2015 Altera Corporation. All rights reserved.

22 | Your use of Altera Corporation's design tools, logic functions

23 | and other software and tools, and its AMPP partner logic

24 | functions, and any output files from any of the foregoing

25 | (including device programming or simulation files), and any

26 | associated documentation or information are expressly subject

27 | to the terms and conditions of the Altera Program License

28 | Subscription Agreement, the Altera Quartus II License Agreement,

29 | the Altera MegaCore Function License Agreement, or other

30 | applicable license agreement, including, without limitation,

31 | that your use is for the sole purpose of programming logic

32 | devices manufactured by Altera and sold by Altera or its

33 | authorized distributors. Please refer to the applicable

34 | agreement for further details.

35 |

36 |

37 |

38 | +---------------------------------------------------------------+

39 | ; Assembler Summary ;

40 | +-----------------------+---------------------------------------+

41 | ; Assembler Status ; Successful - Wed Sep 08 19:32:09 2021 ;

42 | ; Revision Name ; dpll ;

43 | ; Top-level Entity Name ; dpll ;

44 | ; Family ; Cyclone IV E ;

45 | ; Device ; EP4CE15F17C8 ;

46 | +-----------------------+---------------------------------------+

47 |

48 |

49 | +----------------------------------+

50 | ; Assembler Settings ;

51 | +--------+---------+---------------+

52 | ; Option ; Setting ; Default Value ;

53 | +--------+---------+---------------+

54 |

55 |

56 | +---------------------------------------+

57 | ; Assembler Generated Files ;

58 | +---------------------------------------+

59 | ; File Name ;

60 | +---------------------------------------+

61 | ; D:/comber/ADPLL/output_files/dpll.sof ;

62 | +---------------------------------------+

63 |

64 |

65 | +-----------------------------------------------------------------+

66 | ; Assembler Device Options: D:/comber/ADPLL/output_files/dpll.sof ;

67 | +----------------+------------------------------------------------+

68 | ; Option ; Setting ;

69 | +----------------+------------------------------------------------+

70 | ; Device ; EP4CE15F17C8 ;

71 | ; JTAG usercode ; 0x000F8AED ;

72 | ; Checksum ; 0x000F8AED ;

73 | +----------------+------------------------------------------------+

74 |

75 |

76 | +--------------------+

77 | ; Assembler Messages ;

78 | +--------------------+

79 | Info: *******************************************************************

80 | Info: Running Quartus II 64-Bit Assembler

81 | Info: Version 15.0.0 Build 145 04/22/2015 SJ Full Version

82 | Info: Processing started: Wed Sep 08 19:32:08 2021

83 | Info: Command: quartus_asm --read_settings_files=off --write_settings_files=off dpll -c dpll

84 | Info (115031): Writing out detailed assembly data for power analysis

85 | Info (115030): Assembler is generating device programming files

86 | Info: Quartus II 64-Bit Assembler was successful. 0 errors, 0 warnings

87 | Info: Peak virtual memory: 4746 megabytes

88 | Info: Processing ended: Wed Sep 08 19:32:09 2021

89 | Info: Elapsed time: 00:00:01

90 | Info: Total CPU time (on all processors): 00:00:01

91 |

92 |

93 |

--------------------------------------------------------------------------------

/dpll.qsf:

--------------------------------------------------------------------------------

1 | # -------------------------------------------------------------------------- #

2 | #

3 | # Copyright (C) 1991-2013 Altera Corporation

4 | # Your use of Altera Corporation's design tools, logic functions

5 | # and other software and tools, and its AMPP partner logic

6 | # functions, and any output files from any of the foregoing

7 | # (including device programming or simulation files), and any

8 | # associated documentation or information are expressly subject

9 | # to the terms and conditions of the Altera Program License

10 | # Subscription Agreement, Altera MegaCore Function License

11 | # Agreement, or other applicable license agreement, including,

12 | # without limitation, that your use is for the sole purpose of

13 | # programming logic devices manufactured by Altera and sold by

14 | # Altera or its authorized distributors. Please refer to the

15 | # applicable agreement for further details.

16 | #

17 | # -------------------------------------------------------------------------- #

18 | #

19 | # Quartus II 64-Bit

20 | # Version 13.1.0 Build 162 10/23/2013 SJ Full Version

21 | # Date created = 22:10:53 August 26, 2021

22 | #

23 | # -------------------------------------------------------------------------- #

24 | #

25 | # Notes:

26 | #

27 | # 1) The default values for assignments are stored in the file:

28 | # dpll_assignment_defaults.qdf

29 | # If this file doesn't exist, see file:

30 | # assignment_defaults.qdf

31 | #

32 | # 2) Altera recommends that you do not modify this file. This

33 | # file is updated automatically by the Quartus II software

34 | # and any changes you make may be lost or overwritten.

35 | #

36 | # -------------------------------------------------------------------------- #

37 |

38 |

39 | set_global_assignment -name FAMILY "Cyclone IV E"

40 | set_global_assignment -name DEVICE EP4CE15F17C8

41 | set_global_assignment -name TOP_LEVEL_ENTITY dpll

42 | set_global_assignment -name ORIGINAL_QUARTUS_VERSION 13.1

43 | set_global_assignment -name PROJECT_CREATION_TIME_DATE "22:10:53 AUGUST 26, 2021"

44 | set_global_assignment -name LAST_QUARTUS_VERSION 15.0.0

45 | set_global_assignment -name PROJECT_OUTPUT_DIRECTORY output_files

46 | set_global_assignment -name MIN_CORE_JUNCTION_TEMP 0

47 | set_global_assignment -name MAX_CORE_JUNCTION_TEMP 85

48 | set_global_assignment -name DEVICE_FILTER_PACKAGE FBGA

49 | set_global_assignment -name DEVICE_FILTER_SPEED_GRADE 8

50 | set_global_assignment -name ERROR_CHECK_FREQUENCY_DIVISOR 1

51 | set_global_assignment -name NOMINAL_CORE_SUPPLY_VOLTAGE 1.2V

52 | set_global_assignment -name EDA_SIMULATION_TOOL "ModelSim-Altera (Verilog)"

53 | set_global_assignment -name EDA_OUTPUT_DATA_FORMAT "VERILOG HDL" -section_id eda_simulation

54 | set_global_assignment -name VERILOG_FILE source/dpll.v

55 | set_global_assignment -name VERILOG_FILE source/phasecomparator.v

56 | set_global_assignment -name VERILOG_FILE source/randomwalkfilter.v

57 | set_global_assignment -name VERILOG_FILE source/variableresetrandomwalkfilter.v

58 | set_global_assignment -name POWER_PRESET_COOLING_SOLUTION "23 MM HEAT SINK WITH 200 LFPM AIRFLOW"

59 | set_global_assignment -name POWER_BOARD_THERMAL_MODEL "NONE (CONSERVATIVE)"

60 | set_global_assignment -name PARTITION_NETLIST_TYPE SOURCE -section_id Top

61 | set_global_assignment -name PARTITION_FITTER_PRESERVATION_LEVEL PLACEMENT_AND_ROUTING -section_id Top

62 | set_global_assignment -name PARTITION_COLOR 16764057 -section_id Top

63 | set_global_assignment -name EDA_TIME_SCALE "1 ns" -section_id eda_simulation

64 | set_global_assignment -name EDA_TEST_BENCH_ENABLE_STATUS TEST_BENCH_MODE -section_id eda_simulation

65 | set_global_assignment -name EDA_NATIVELINK_SIMULATION_TEST_BENCH dpll -section_id eda_simulation

66 | set_global_assignment -name EDA_TEST_BENCH_NAME dpll -section_id eda_simulation

67 | set_global_assignment -name EDA_DESIGN_INSTANCE_NAME i1 -section_id dpll

68 | set_global_assignment -name EDA_TEST_BENCH_MODULE_NAME dpll_vlg_tst -section_id dpll

69 | set_global_assignment -name EDA_TEST_BENCH_FILE simulation/modelsim/dpll.vt -section_id dpll

70 | set_global_assignment -name VERILOG_FILE source/freqdivider.v

71 | set_instance_assignment -name PARTITION_HIERARCHY root_partition -to | -section_id Top

--------------------------------------------------------------------------------

/source/variableresetrandomwalkfilter.v.bak:

--------------------------------------------------------------------------------

1 |

2 | /* random-walk filter with variable reset */

3 |

4 | module variableresetrandomwalkfilter(

5 | MainClock,

6 | Lead, Lag,

7 | Positive, Negative,

8 | N_FilterCounter, ResetterValue, ResetterCounter);

9 |

10 | input MainClock, Lead, Lag; // System Clock and Phase Comparator signals

11 | output Positive, Negative; // "positive shift" and "negative shift" outputs

12 | output [7 : 0] N_FilterCounter,ResetterValue;

13 | output [3 : 0] ResetterCounter;

14 |

15 | parameter N_FilterLength = 8;

16 | parameter N_FilterResetValue = 8;

17 | parameter N_FilterMaxValue = N_FilterResetValue;

18 |

19 | /* 256=2_PWR_8(counter length). Use this value because unsigned arithmetic */

20 | parameter N_FilterMinValue = 256 - N_FilterResetValue;

21 |

22 | /* the counter length of reset scheme must be short */

23 | parameter ResetterCounterLength = 4;

24 | parameter ResetterCounterMaxValue = 3;

25 |

26 | /* 16=2_PWR_4 */

27 | parameter ResetterCounterMinValue = 16 - 3;

28 |

29 | /* counter "N - RandomWalkFilter" */

30 | reg [N_FilterLength-1 : 0] N_FilterCounter;

31 |

32 | /* connections of "M - RandomWalkFilter" */

33 | wire Up, Down;

34 | randomwalkfilter inst_M_F(.MainClock(MainClock), .Lead(Lead), .Lag(Lag),

35 | .Positive(Up), .Negative(Down));

36 |

37 | defparam inst_M_F.FilterResetValue = 32; // length "M-RWF" = 32

38 |

39 |

40 | /* Reset Scheme. This counter changes on "M-RWF" counter */

41 | reg [ResetterCounterLength-1 : 0] ResetterCounter;

42 | always @(posedge MainClock)

43 | begin

44 | if(Up)

45 | begin

46 | if((ResetterCounter < ResetterCounterMaxValue) || (ResetterCounter >= ResetterCounterMinValue))

47 | ResetterCounter <= ResetterCounter + 1;

48 | end

49 | else if(Down)

50 | begin

51 | if((ResetterCounter <= ResetterCounterMaxValue) || (ResetterCounter > ResetterCounterMinValue))

52 | ResetterCounter <= ResetterCounter - 1;

53 | end

54 | if((ResetterCounter > ResetterCounterMaxValue) && (ResetterCounter < ResetterCounterMinValue))

55 | ResetterCounter <= 0;

56 | end

57 |

58 | /* Look-Up Table between ResetterCounter value and reset state of "N-RWF" */

59 | reg [N_FilterLength-1 : 0] ResetterValue;

60 | always @(1)

61 | begin

62 | case(ResetterCounter)

63 | 16 - 3: ResetterValue = 256 - 7;

64 | 16 - 2: ResetterValue = 256 - 6;

65 | 16 - 1: ResetterValue = 256 - 4;

66 | 0: ResetterValue = 0;

67 | 1: ResetterValue = 4;

68 | 2: ResetterValue = 6;

69 | 3: ResetterValue = 7;

70 | default: ResetterValue = 0;

71 | endcase

72 | end

73 |

74 | /* "N-RWF" Filter has different reset states */

75 | /* in accordance ResetterCounter value */

76 | always @(posedge MainClock)

77 | begin

78 | if((N_FilterCounter == N_FilterMaxValue) || (N_FilterCounter == N_FilterMinValue))

79 | N_FilterCounter <= ResetterValue;

80 | else

81 | begin

82 | if(Lead) N_FilterCounter <= N_FilterCounter + 1;

83 | if(Lag) N_FilterCounter <= N_FilterCounter - 1;

84 | end

85 | end

86 |

87 | /* making "Lead" and "Lag" signals when */

88 | /* counter reached max or min levels */

89 | reg Positive, Negative;

90 | always @(posedge MainClock)

91 | begin

92 | Positive <= (N_FilterCounter == N_FilterMaxValue);

93 | Negative <= (N_FilterCounter == N_FilterMinValue);

94 | end

95 |

96 | initial begin

97 | N_FilterCounter <= 0;

98 | ResetterCounter <= 0;

99 | ResetterValue <= 0;

100 | end

101 |

102 |

103 | endmodule

104 |

--------------------------------------------------------------------------------

/source/variableresetrandomwalkfilter.v:

--------------------------------------------------------------------------------

1 | `timescale 1ns / 1ps

2 |

3 | /* random-walk filter with variable reset */

4 |

5 | module variableresetrandomwalkfilter(

6 | MainClock,

7 | Lead, Lag,

8 | Positive, Negative,

9 | N_FilterCounter, ResetterValue, ResetterCounter);

10 |

11 | input MainClock, Lead, Lag; // System Clock and Phase Comparator signals

12 | output Positive, Negative; // "positive shift" and "negative shift" outputs

13 | output [7 : 0] N_FilterCounter,ResetterValue;

14 | output [3 : 0] ResetterCounter;

15 |

16 | parameter N_FilterLength = 8;

17 | parameter N_FilterResetValue = 8;

18 | parameter N_FilterMaxValue = N_FilterResetValue;

19 |

20 | /* 256=2_PWR_8(counter length). Use this value because unsigned arithmetic */

21 | parameter N_FilterMinValue = 256 - N_FilterResetValue;

22 |

23 | /* the counter length of reset scheme must be short */

24 | parameter ResetterCounterLength = 4;

25 | parameter ResetterCounterMaxValue = 3;

26 |

27 | /* 16=2_PWR_4 */

28 | parameter ResetterCounterMinValue = 16 - 3;

29 |

30 | /* counter "N - RandomWalkFilter" */

31 | reg [N_FilterLength-1 : 0] N_FilterCounter;

32 |

33 | /* connections of "M - RandomWalkFilter" */

34 | wire Up, Down;

35 | randomwalkfilter inst_M_F(.MainClock(MainClock), .Lead(Lead), .Lag(Lag),

36 | .Positive(Up), .Negative(Down));

37 |

38 | defparam inst_M_F.FilterResetValue = 32; // length "M-RWF" = 32

39 |

40 |

41 | /* Reset Scheme. This counter changes on "M-RWF" counter */

42 | reg [ResetterCounterLength-1 : 0] ResetterCounter;

43 | always @(posedge MainClock)

44 | begin

45 | if(Up)

46 | begin

47 | if((ResetterCounter < ResetterCounterMaxValue) || (ResetterCounter >= ResetterCounterMinValue))

48 | ResetterCounter <= ResetterCounter + 1;

49 | end

50 | else if(Down)

51 | begin

52 | if((ResetterCounter <= ResetterCounterMaxValue) || (ResetterCounter > ResetterCounterMinValue))

53 | ResetterCounter <= ResetterCounter - 1;

54 | end

55 | if((ResetterCounter > ResetterCounterMaxValue) && (ResetterCounter < ResetterCounterMinValue))

56 | ResetterCounter <= 0;

57 | end

58 |

59 | /* Look-Up Table between ResetterCounter value and reset state of "N-RWF" */

60 | reg [N_FilterLength-1 : 0] ResetterValue;

61 | always @(1)

62 | begin

63 | case(ResetterCounter)

64 | 16 - 3: ResetterValue = 256 - 7;

65 | 16 - 2: ResetterValue = 256 - 6;

66 | 16 - 1: ResetterValue = 256 - 4;

67 | 0: ResetterValue = 0;

68 | 1: ResetterValue = 4;

69 | 2: ResetterValue = 6;

70 | 3: ResetterValue = 7;

71 | default: ResetterValue = 0;

72 | endcase

73 | end

74 |

75 | /* "N-RWF" Filter has different reset states */

76 | /* in accordance ResetterCounter value */

77 | always @(posedge MainClock)

78 | begin

79 | if((N_FilterCounter == N_FilterMaxValue) || (N_FilterCounter == N_FilterMinValue))

80 | N_FilterCounter <= ResetterValue;

81 | else

82 | begin

83 | if(Lead) N_FilterCounter <= N_FilterCounter + 1;

84 | if(Lag) N_FilterCounter <= N_FilterCounter - 1;

85 | end

86 | end

87 |

88 | /* making "Lead" and "Lag" signals when */

89 | /* counter reached max or min levels */

90 | reg Positive, Negative;

91 | always @(posedge MainClock)

92 | begin

93 | Positive <= (N_FilterCounter == N_FilterMaxValue);

94 | Negative <= (N_FilterCounter == N_FilterMinValue);

95 | end

96 |

97 | initial begin

98 | N_FilterCounter <= 0;

99 | ResetterCounter <= 0;

100 | ResetterValue <= 0;

101 | end

102 |

103 |

104 | endmodule

105 |

--------------------------------------------------------------------------------

/README.md:

--------------------------------------------------------------------------------

1 | # ADPLL_base_Verilog

2 | ## 基于Verilog的全数字锁相环

3 |

4 | ---

5 | 2021年9月23日 from [my blog:lijinbo.top](http://lijinbo.top/)

6 | ---

7 |

8 | # 概述

9 |

10 | 项目的主要目标就是用**Verilog**设计实现一款数字锁相环,基于低频率时钟源,倍频产生高频时钟,并且达到高频时钟输出相位锁定、占空比1:1的预期效果。设计全基于Verilog代码实现,第一阶段实现数字锁相环,达到输出锁定的效果,第二阶段进行倍频的实现。工程基于**QuartusII**平台实现,基于**Modelsim**平台进行行为仿真,验证功能的正确性,观测仿真波形图。

11 |

12 |

13 |

14 |

15 |

16 | # 层次结构

17 |

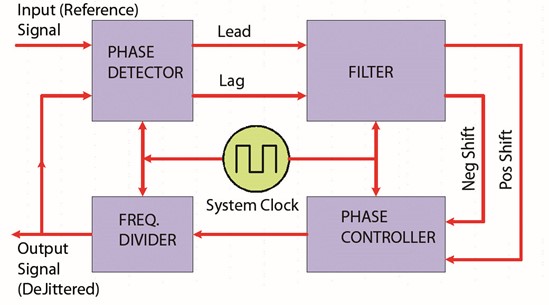

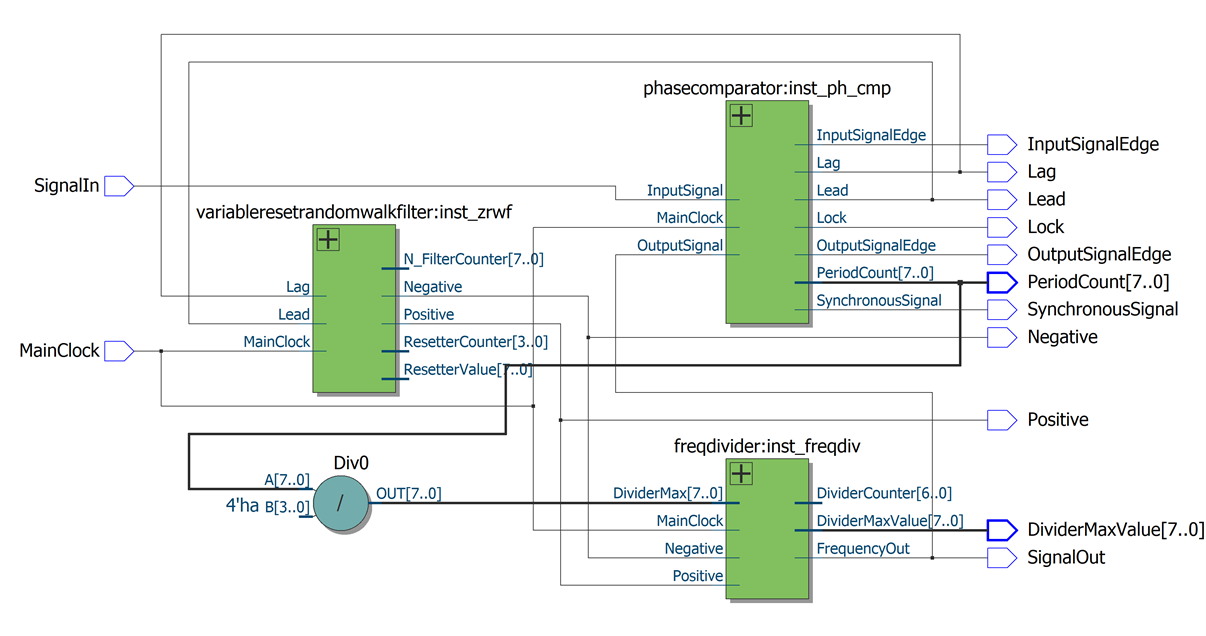

18 | 工程的结构分为顶层模块**dpll.v**和子模块**Phasecomparator**、**VariableResetRandomWalkFilter**和**Freqdivider**,分别对应PLL原理中的鉴相器**PD**、环路滤波器**LF**和受控振荡器**VCO**。系统在统一的系统时钟下同步工作,参考的架构图如下:

19 |

20 |

21 |

22 |

23 |

24 |

25 |

26 | # 模块说明

27 |

28 | ## DPLL.v

29 |

30 | ### 模块接口

31 |

32 | ```verilog

33 | module dpll(

34 | input SignalIn; // 输入信号

35 | input MainClock; // 系统时钟

36 | output SignalOut; // 输出信号

37 | output Positive, Negative; // 环路滤波器输出

38 | output Lead, Lag; // 鉴相器输出

39 | );

40 | ```

41 |

42 |

43 |

44 | ### 功能描述

45 |

46 | **DPLL**模块是工程的顶层文件,负责把各个子模块组合起来,负责声明整个系统的信号接口。

47 |

48 | ## Phasecomparator.v

49 |

50 | ### 模块接口

51 |

52 | ```verilog

53 | module phasecomparator(

54 | input MainClock, // System Clock

55 | input InputSignal, OutputSignal, // 输入输出信号

56 | output SynchronousSignal, // 同步信号

57 | output Lead, Lag, // 超前、滞后脉冲

58 | output InputSignalEdge, // 输入信号上升沿

59 | output OutputSignalEdge, // 输出信号上升沿

60 | output Lock, // 锁定标志位

61 | output [7:0] PeriodCount // 输入信号周期

62 | );

63 | ```

64 |

65 |

66 |

67 | ### 功能描述

68 |

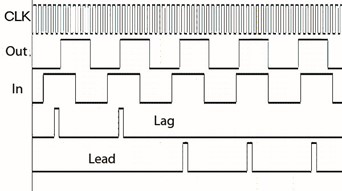

69 | **Phasecomparator**为鉴相器模块,首先通过D触发器,把输入信号同步到系统的时钟域;其二,统计输入信号的周期,用于振荡信号的生成;其三,对输入信号与反馈信号进行相位比较,反馈信号超前于输入信号则置Lead为高电平,反之,反馈信号滞后则置Lag为高电平,这两个信号有效的持续周期都为一个系统时钟周期。

70 |

71 |

72 |

73 |

74 |

75 |

76 |

77 | ## VariableResetRandomWalkFilter.v和RandomWalkFilter.v

78 |

79 | ### 模块接口

80 |

81 | ```verilog

82 | module variableresetrandomwalkfilter(

83 | input MainClock, Lead, Lag; // System Clock and Phase Comparator signals

84 | output Positive, Negative; // "positive shift" and "negative shift" outputs

85 | );

86 | ```

87 |

88 | ```verilog

89 | module randomwalkfilter(

90 | input MainClock, Lead, Lag; // System Clock and Phase Comparator signals

91 | output Positive, Negative; // "positive shift" and "negative shift" outputs

92 | );

93 | ```

94 |

95 | ### 功能描述

96 |

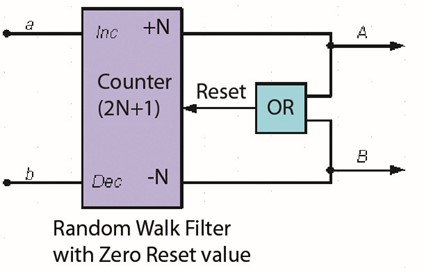

97 | **VariableResetRandomWalkFilter**模块是环路滤波器模块,**RandomWalkFilter**是它的子模块,该子模块实现的是**随机徘徊序列滤波器**,前者在后者基础上增加Reset值可调的功能。随机徘徊序列滤波器的主体是一个可逆计数器。当有超前脉冲输人到UP端时,计数器上行计数,当有滞后脉冲输入到DN端时,计数器下行计数。如果超前脉冲超过滞后的数目到达计数容量N时,就在+N端输出一个提前脉冲,同时使计数器复位。反之,则在-N端输出一个推后脉冲,同时计数器复位。环路锁定前,鉴相器连续输出超前或滞后脉冲,上行计数器或下行计数器到达满状态后输出提前脉冲或推后脉冲,在这两个脉冲作用下环路逐步进入锁定状态。当环路进入锁定状态后,由噪声引起的超前或滞后脉冲是随机的,而且出现概率基本相等,不会有连续很多个超前或滞后脉冲,因而它们的差值达到计数容量N的可能性极小,这样就可以减小噪声对环路的干扰作用。

98 |

99 |

100 |

101 |

102 |

103 |

104 |

105 |

106 |

107 | ## Freqdivider.v

108 |

109 | ### 模块接口

110 |

111 | ```verilog

112 | module freqdivider(

113 | input MainClock;

114 | input Positive, Negative; // 控制输出周期

115 | output FrequencyOut; // 倍频输出

116 | );

117 | ```

118 |

119 | ### 功能描述

120 |

121 | 主要功能是基于系统时钟进行分频。系统时钟取决于FPGA硬件型号,一般需要较高的系统时钟。基于由上述鉴相器模块计算得到的输入信号的时钟周期数,计算倍频信号的时钟周期数,产生同步振荡信号。由于存在系统延时,一开始产生的振荡信号与输入信号并不同步,由鉴相器处理使其逐渐达到同步锁定状态。

122 |

123 | # 功能仿真

124 |

125 | ## 电路逻辑

126 |

127 | 使用Quartus完成程序设计,对应的RTL电路逻辑如下图所示。

128 |

129 |

130 |

131 | ## 仿真参数

132 |

133 | 系统时钟设置为50MHz,输入信号频率为500KHz,输入信号具有不确定性,即仿真中添加一个随机时延,此处设置为3287ns。

134 |

135 | ## 仿真效果

136 |

137 | ### 同步性能

138 |

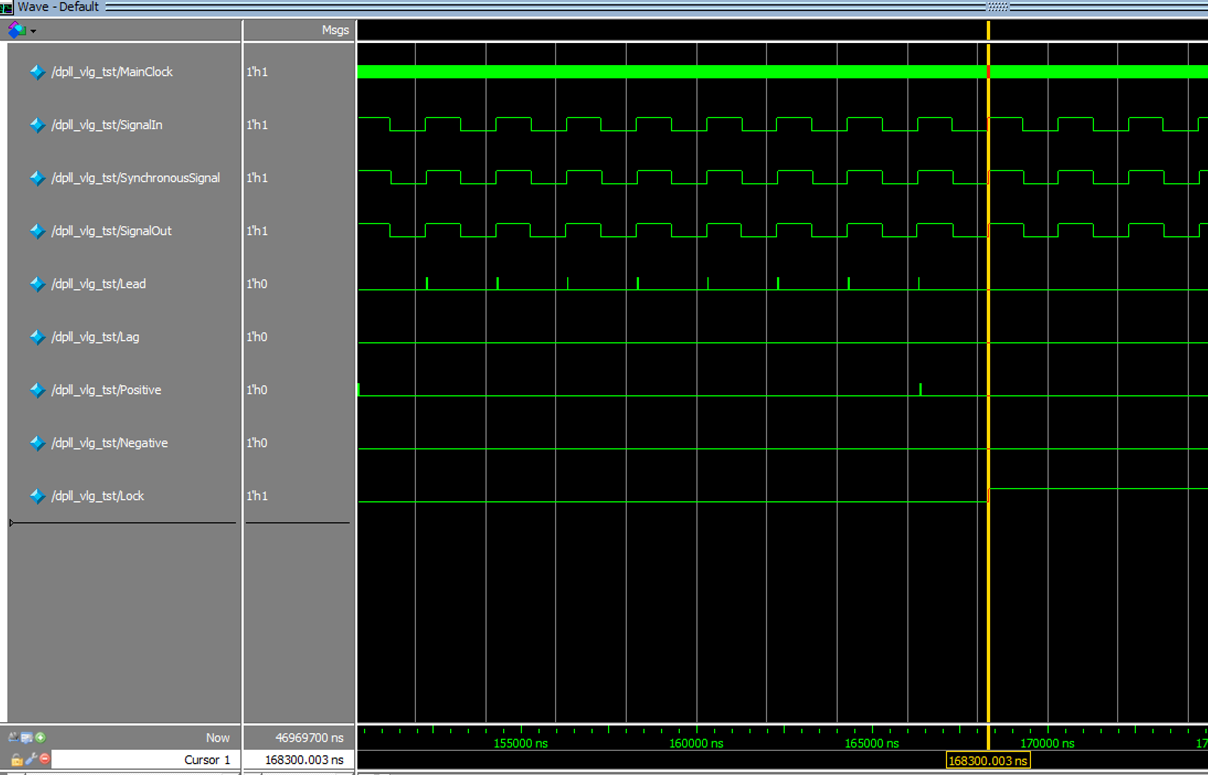

139 | 波形仿真图如图3-1所示,MainClock为系统时钟,SignalIn为输入信号,SignalOut为输出信号,Lead、Lag分别为鉴相器输出的相位领先和滞后信号,Positive、Negative则对应上述两个信号经过环路滤波器后的输出。Lock是输出锁定信号,置高电平时环路锁定。由仿真波形图可以看出,锁定时间为168300ns ,减去开头加入的输入时延3287ns,实际锁定时间为165013ns,即165μs,锁定后输出与输入信号同频同相。

140 |

141 |

142 |

143 | ### 倍频效果

144 |

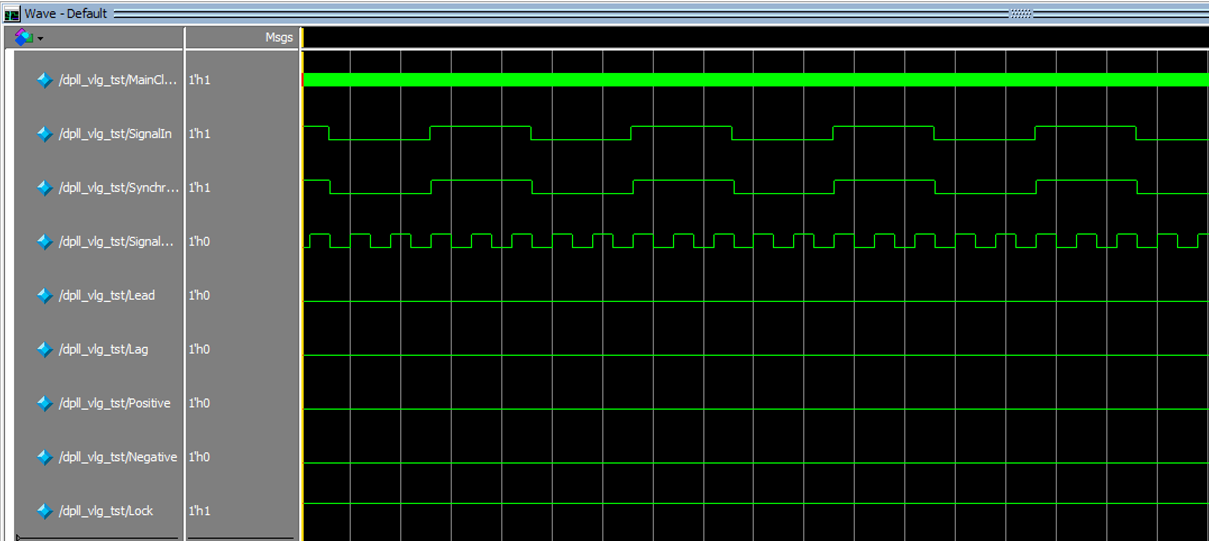

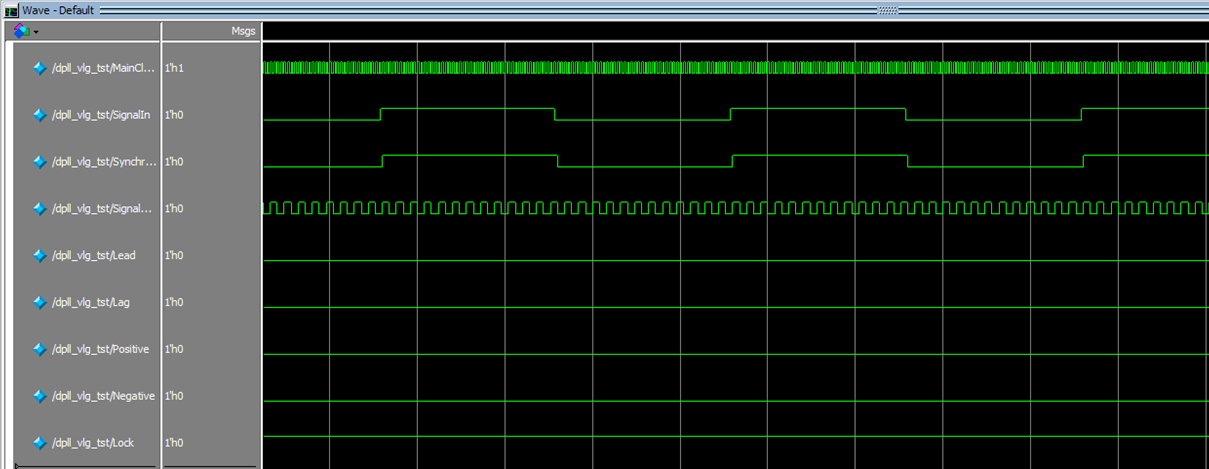

145 | 改变顶层文件(dpll.v)里的参数(parameter)DividerMultiple的值,便可以修改锁相环输出倍频的倍数,可以实现奇倍频和偶倍频。如图所示分别为基于500KHz输入信号产生2倍频、5倍频和20倍频的效果图。。

146 |

147 |

148 |

149 |

150 |

151 |

152 |

153 | # 总结

154 |

155 | 本设计实现了一款全数字锁相环路,能够基于低频率时钟源,倍频产生高频时钟,并且达到高频时钟输出相位锁定、占空比1:1的预期效果。通过本次设计的锁相环路,可以实现在FPGA平台上,锁定未知的较低频输入信号,产生同频同相的任意倍频(频率低于系统时钟频率)输出信号。本设计完全基于Verilog代码实现,程序简单,完全可以满足简单地实现同步倍频信号的场合要求。

156 |

157 |

158 |

159 |

160 |

161 | - end

162 |

--------------------------------------------------------------------------------

/simulation/modelsim/msim_transcript:

--------------------------------------------------------------------------------

1 | # Reading D:/Application/Altera/Quartus_13.1/modelsim_ase/tcl/vsim/pref.tcl

2 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/secureip". (Format: 4)

3 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/simprims_ver". (Format: 4)

4 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/unifast". (Format: 4)

5 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/unifast_ver". (Format: 4)

6 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/unimacro". (Format: 4)

7 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/unimacro_ver". (Format: 4)

8 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/unisim". (Format: 4)

9 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/unisims_ver". (Format: 4)

10 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/xilinx_vip". (Format: 4)

11 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/xpm". (Format: 4)

12 | # do dpll_run_msim_rtl_verilog.do

13 | # if {[file exists rtl_work]} {

14 | # vdel -lib rtl_work -all

15 | # }

16 | # vlib rtl_work

17 | # vmap work rtl_work

18 | # Modifying E:\Xilinx\Xlib\modelsim.ini

19 | #

20 | # vlog -vlog01compat -work work +incdir+D:/comber/ADPLL/source {D:/comber/ADPLL/source/dpll.v}

21 | # Model Technology ModelSim ALTERA vlog 10.1d Compiler 2012.11 Nov 2 2012

22 | # -- Compiling module dpll

23 | #

24 | # Top level modules:

25 | # dpll

26 | # vlog -vlog01compat -work work +incdir+D:/comber/ADPLL/source {D:/comber/ADPLL/source/freqdivider.v}

27 | # Model Technology ModelSim ALTERA vlog 10.1d Compiler 2012.11 Nov 2 2012

28 | # -- Compiling module freqdivider

29 | #

30 | # Top level modules:

31 | # freqdivider

32 | # vlog -vlog01compat -work work +incdir+D:/comber/ADPLL/source {D:/comber/ADPLL/source/phasecomparator.v}

33 | # Model Technology ModelSim ALTERA vlog 10.1d Compiler 2012.11 Nov 2 2012

34 | # -- Compiling module phasecomparator

35 | #

36 | # Top level modules:

37 | # phasecomparator

38 | # vlog -vlog01compat -work work +incdir+D:/comber/ADPLL/source {D:/comber/ADPLL/source/randomwalkfilter.v}

39 | # Model Technology ModelSim ALTERA vlog 10.1d Compiler 2012.11 Nov 2 2012

40 | # -- Compiling module randomwalkfilter

41 | #

42 | # Top level modules:

43 | # randomwalkfilter

44 | # vlog -vlog01compat -work work +incdir+D:/comber/ADPLL/source {D:/comber/ADPLL/source/variableresetrandomwalkfilter.v}

45 | # Model Technology ModelSim ALTERA vlog 10.1d Compiler 2012.11 Nov 2 2012

46 | # -- Compiling module variableresetrandomwalkfilter

47 | #

48 | # Top level modules:

49 | # variableresetrandomwalkfilter

50 | #

51 | # vlog -vlog01compat -work work +incdir+D:/comber/ADPLL/simulation/modelsim {D:/comber/ADPLL/simulation/modelsim/dpll.vt}

52 | # Model Technology ModelSim ALTERA vlog 10.1d Compiler 2012.11 Nov 2 2012

53 | # -- Compiling module dpll_vlg_tst

54 | #

55 | # Top level modules:

56 | # dpll_vlg_tst

57 | #

58 | # vsim -t 1ps -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L cycloneive_ver -L rtl_work -L work -voptargs="+acc" dpll_vlg_tst

59 | # vsim -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L cycloneive_ver -L rtl_work -L work -voptargs=\"+acc\" -t 1ps dpll_vlg_tst

60 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/secureip". (Format: 4)

61 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/simprims_ver". (Format: 4)

62 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/unifast". (Format: 4)

63 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/unifast_ver". (Format: 4)

64 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/unimacro". (Format: 4)

65 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/unimacro_ver". (Format: 4)

66 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/unisim". (Format: 4)

67 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/unisims_ver". (Format: 4)

68 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/xilinx_vip". (Format: 4)

69 | # ** Error: (vish-42) Unsupported ModelSim library format for "E:/Xilinx/Xlib/xpm". (Format: 4)

70 | # Loading work.dpll_vlg_tst

71 | # Loading work.dpll

72 | # Loading work.phasecomparator

73 | # Loading work.variableresetrandomwalkfilter

74 | # Loading work.randomwalkfilter

75 | # Loading work.freqdivider

76 | # ** Warning: (vsim-3017) D:/comber/ADPLL/source/dpll.v(43): [TFMPC] - Too few port connections. Expected 8, found 5.

77 | #

78 | # Region: /dpll_vlg_tst/i1/inst_zrwf

79 | # ** Warning: (vsim-3722) D:/comber/ADPLL/source/dpll.v(43): [TFMPC] - Missing connection for port 'N_FilterCounter'.

80 | #

81 | # ** Warning: (vsim-3722) D:/comber/ADPLL/source/dpll.v(43): [TFMPC] - Missing connection for port 'ResetterValue'.

82 | #

83 | # ** Warning: (vsim-3722) D:/comber/ADPLL/source/dpll.v(43): [TFMPC] - Missing connection for port 'ResetterCounter'.

84 | #

85 | # ** Warning: (vsim-3017) D:/comber/ADPLL/source/dpll.v(48): [TFMPC] - Too few port connections. Expected 7, found 6.

86 | #

87 | # Region: /dpll_vlg_tst/i1/inst_freqdiv

88 | # ** Warning: (vsim-3015) D:/comber/ADPLL/source/dpll.v(48): [PCDPC] - Port size (8 or 8) does not match connection size (32) for port 'DividerMax'. The port definition is at: D:/comber/ADPLL/source/freqdivider.v(5).

89 | #

90 | # Region: /dpll_vlg_tst/i1/inst_freqdiv

91 | # ** Warning: (vsim-3722) D:/comber/ADPLL/source/dpll.v(48): [TFMPC] - Missing connection for port 'DividerCounter'.

92 | #

93 | #

94 | # add wave *

95 | # view structure

96 | # .main_pane.structure.interior.cs.body.struct

97 | # view signals

98 | # .main_pane.objects.interior.cs.body.tree

99 | # run -all

100 | # Running testbench

101 | # Break key hit

102 | # Simulation stop requested.

103 |

--------------------------------------------------------------------------------

/db/dpll.eda.qmsg:

--------------------------------------------------------------------------------

1 | { "Info" "IQEXE_SEPARATOR" "" "*******************************************************************" { } { } 3 0 "*******************************************************************" 0 0 "Quartus II" 0 -1 1631100736279 ""}

2 | { "Info" "IQEXE_START_BANNER_PRODUCT" "EDA Netlist Writer Quartus II 64-Bit " "Running Quartus II 64-Bit EDA Netlist Writer" { { "Info" "IQEXE_START_BANNER_VERSION" "Version 15.0.0 Build 145 04/22/2015 SJ Full Version " "Version 15.0.0 Build 145 04/22/2015 SJ Full Version" { } { } 0 0 "%1!s!" 0 0 "Quartus II" 0 -1 1631100736279 ""} { "Info" "IQEXE_START_BANNER_TIME" "Wed Sep 08 19:32:16 2021 " "Processing started: Wed Sep 08 19:32:16 2021" { } { } 0 0 "Processing started: %1!s!" 0 0 "Quartus II" 0 -1 1631100736279 ""} } { } 4 0 "Running %2!s! %1!s!" 0 0 "Quartus II" 0 -1 1631100736279 ""}

3 | { "Info" "IQEXE_START_BANNER_COMMANDLINE" "quartus_eda --read_settings_files=off --write_settings_files=off dpll -c dpll " "Command: quartus_eda --read_settings_files=off --write_settings_files=off dpll -c dpll" { } { } 0 0 "Command: %1!s!" 0 0 "Quartus II" 0 -1 1631100736279 ""}

4 | { "Warning" "WVLGO_INVALID_TIMESCALE_SELECTED_FOR_PLL_DESIGN" "" "An incorrect timescale is selected for the Verilog Output (.VO) file of this PLL design. It's required that the timescale should be 1 ps when simulating a PLL design in a third party EDA tool." { } { } 0 202000 "An incorrect timescale is selected for the Verilog Output (.VO) file of this PLL design. It's required that the timescale should be 1 ps when simulating a PLL design in a third party EDA tool." 0 0 "Quartus II" 0 -1 1631100736813 ""}

5 | { "Info" "IWSC_DONE_HDL_GENERATION" "dpll_8_1200mv_85c_slow.vo D:/comber/ADPLL/simulation/modelsim/ simulation " "Generated file dpll_8_1200mv_85c_slow.vo in folder \"D:/comber/ADPLL/simulation/modelsim/\" for EDA simulation tool" { } { } 0 204019 "Generated file %1!s! in folder \"%2!s!\" for EDA %3!s! tool" 0 0 "Quartus II" 0 -1 1631100736844 ""}

6 | { "Warning" "WVLGO_INVALID_TIMESCALE_SELECTED_FOR_PLL_DESIGN" "" "An incorrect timescale is selected for the Verilog Output (.VO) file of this PLL design. It's required that the timescale should be 1 ps when simulating a PLL design in a third party EDA tool." { } { } 0 202000 "An incorrect timescale is selected for the Verilog Output (.VO) file of this PLL design. It's required that the timescale should be 1 ps when simulating a PLL design in a third party EDA tool." 0 0 "Quartus II" 0 -1 1631100736875 ""}

7 | { "Info" "IWSC_DONE_HDL_GENERATION" "dpll_8_1200mv_0c_slow.vo D:/comber/ADPLL/simulation/modelsim/ simulation " "Generated file dpll_8_1200mv_0c_slow.vo in folder \"D:/comber/ADPLL/simulation/modelsim/\" for EDA simulation tool" { } { } 0 204019 "Generated file %1!s! in folder \"%2!s!\" for EDA %3!s! tool" 0 0 "Quartus II" 0 -1 1631100736907 ""}

8 | { "Warning" "WVLGO_INVALID_TIMESCALE_SELECTED_FOR_PLL_DESIGN" "" "An incorrect timescale is selected for the Verilog Output (.VO) file of this PLL design. It's required that the timescale should be 1 ps when simulating a PLL design in a third party EDA tool." { } { } 0 202000 "An incorrect timescale is selected for the Verilog Output (.VO) file of this PLL design. It's required that the timescale should be 1 ps when simulating a PLL design in a third party EDA tool." 0 0 "Quartus II" 0 -1 1631100736922 ""}

9 | { "Info" "IWSC_DONE_HDL_GENERATION" "dpll_min_1200mv_0c_fast.vo D:/comber/ADPLL/simulation/modelsim/ simulation " "Generated file dpll_min_1200mv_0c_fast.vo in folder \"D:/comber/ADPLL/simulation/modelsim/\" for EDA simulation tool" { } { } 0 204019 "Generated file %1!s! in folder \"%2!s!\" for EDA %3!s! tool" 0 0 "Quartus II" 0 -1 1631100736954 ""}

10 | { "Warning" "WVLGO_INVALID_TIMESCALE_SELECTED_FOR_PLL_DESIGN" "" "An incorrect timescale is selected for the Verilog Output (.VO) file of this PLL design. It's required that the timescale should be 1 ps when simulating a PLL design in a third party EDA tool." { } { } 0 202000 "An incorrect timescale is selected for the Verilog Output (.VO) file of this PLL design. It's required that the timescale should be 1 ps when simulating a PLL design in a third party EDA tool." 0 0 "Quartus II" 0 -1 1631100736985 ""}

11 | { "Info" "IWSC_DONE_HDL_GENERATION" "dpll.vo D:/comber/ADPLL/simulation/modelsim/ simulation " "Generated file dpll.vo in folder \"D:/comber/ADPLL/simulation/modelsim/\" for EDA simulation tool" { } { } 0 204019 "Generated file %1!s! in folder \"%2!s!\" for EDA %3!s! tool" 0 0 "Quartus II" 0 -1 1631100737000 ""}

12 | { "Info" "IWSC_DONE_HDL_GENERATION" "dpll_8_1200mv_85c_v_slow.sdo D:/comber/ADPLL/simulation/modelsim/ simulation " "Generated file dpll_8_1200mv_85c_v_slow.sdo in folder \"D:/comber/ADPLL/simulation/modelsim/\" for EDA simulation tool" { } { } 0 204019 "Generated file %1!s! in folder \"%2!s!\" for EDA %3!s! tool" 0 0 "Quartus II" 0 -1 1631100737032 ""}

13 | { "Info" "IWSC_DONE_HDL_GENERATION" "dpll_8_1200mv_0c_v_slow.sdo D:/comber/ADPLL/simulation/modelsim/ simulation " "Generated file dpll_8_1200mv_0c_v_slow.sdo in folder \"D:/comber/ADPLL/simulation/modelsim/\" for EDA simulation tool" { } { } 0 204019 "Generated file %1!s! in folder \"%2!s!\" for EDA %3!s! tool" 0 0 "Quartus II" 0 -1 1631100737079 ""}

14 | { "Info" "IWSC_DONE_HDL_GENERATION" "dpll_min_1200mv_0c_v_fast.sdo D:/comber/ADPLL/simulation/modelsim/ simulation " "Generated file dpll_min_1200mv_0c_v_fast.sdo in folder \"D:/comber/ADPLL/simulation/modelsim/\" for EDA simulation tool" { } { } 0 204019 "Generated file %1!s! in folder \"%2!s!\" for EDA %3!s! tool" 0 0 "Quartus II" 0 -1 1631100737110 ""}

15 | { "Info" "IWSC_DONE_HDL_GENERATION" "dpll_v.sdo D:/comber/ADPLL/simulation/modelsim/ simulation " "Generated file dpll_v.sdo in folder \"D:/comber/ADPLL/simulation/modelsim/\" for EDA simulation tool" { } { } 0 204019 "Generated file %1!s! in folder \"%2!s!\" for EDA %3!s! tool" 0 0 "Quartus II" 0 -1 1631100737141 ""}

16 | { "Info" "IQEXE_ERROR_COUNT" "EDA Netlist Writer 0 s 4 s Quartus II 64-Bit " "Quartus II 64-Bit EDA Netlist Writer was successful. 0 errors, 4 warnings" { { "Info" "IQEXE_END_PEAK_VSIZE_MEMORY" "4722 " "Peak virtual memory: 4722 megabytes" { } { } 0 0 "Peak virtual memory: %1!s! megabytes" 0 0 "Quartus II" 0 -1 1631100737188 ""} { "Info" "IQEXE_END_BANNER_TIME" "Wed Sep 08 19:32:17 2021 " "Processing ended: Wed Sep 08 19:32:17 2021" { } { } 0 0 "Processing ended: %1!s!" 0 0 "Quartus II" 0 -1 1631100737188 ""} { "Info" "IQEXE_ELAPSED_TIME" "00:00:01 " "Elapsed time: 00:00:01" { } { } 0 0 "Elapsed time: %1!s!" 0 0 "Quartus II" 0 -1 1631100737188 ""} { "Info" "IQEXE_ELAPSED_CPU_TIME" "00:00:01 " "Total CPU time (on all processors): 00:00:01" { } { } 0 0 "Total CPU time (on all processors): %1!s!" 0 0 "Quartus II" 0 -1 1631100737188 ""} } { } 0 0 "%6!s! %1!s! was successful. %2!d! error%3!s!, %4!d! warning%5!s!" 0 0 "Quartus II" 0 -1 1631100737188 ""}

17 |

--------------------------------------------------------------------------------

/output_files/dpll.eda.rpt:

--------------------------------------------------------------------------------

1 | EDA Netlist Writer report for dpll

2 | Wed Sep 08 19:32:17 2021

3 | Quartus II 64-Bit Version 15.0.0 Build 145 04/22/2015 SJ Full Version

4 |

5 |

6 | ---------------------

7 | ; Table of Contents ;

8 | ---------------------

9 | 1. Legal Notice

10 | 2. EDA Netlist Writer Summary

11 | 3. Simulation Settings

12 | 4. Simulation Generated Files

13 | 5. EDA Netlist Writer Messages

14 |

15 |

16 |

17 | ----------------

18 | ; Legal Notice ;

19 | ----------------

20 | Copyright (C) 1991-2015 Altera Corporation. All rights reserved.

21 | Your use of Altera Corporation's design tools, logic functions

22 | and other software and tools, and its AMPP partner logic

23 | functions, and any output files from any of the foregoing

24 | (including device programming or simulation files), and any

25 | associated documentation or information are expressly subject

26 | to the terms and conditions of the Altera Program License

27 | Subscription Agreement, the Altera Quartus II License Agreement,

28 | the Altera MegaCore Function License Agreement, or other

29 | applicable license agreement, including, without limitation,

30 | that your use is for the sole purpose of programming logic

31 | devices manufactured by Altera and sold by Altera or its

32 | authorized distributors. Please refer to the applicable

33 | agreement for further details.

34 |

35 |

36 |

37 | +-------------------------------------------------------------------+

38 | ; EDA Netlist Writer Summary ;

39 | +---------------------------+---------------------------------------+

40 | ; EDA Netlist Writer Status ; Successful - Wed Sep 08 19:32:17 2021 ;

41 | ; Revision Name ; dpll ;

42 | ; Top-level Entity Name ; dpll ;

43 | ; Family ; Cyclone IV E ;

44 | ; Simulation Files Creation ; Successful ;

45 | +---------------------------+---------------------------------------+

46 |

47 |

48 | +-------------------------------------------------------------------------------------------------------------------------------+

49 | ; Simulation Settings ;

50 | +---------------------------------------------------------------------------------------------------+---------------------------+

51 | ; Option ; Setting ;

52 | +---------------------------------------------------------------------------------------------------+---------------------------+

53 | ; Tool Name ; ModelSim-Altera (Verilog) ;

54 | ; Generate netlist for functional simulation only ; Off ;

55 | ; Time scale ; 1 ns ;

56 | ; Truncate long hierarchy paths ; Off ;

57 | ; Map illegal HDL characters ; Off ;

58 | ; Flatten buses into individual nodes ; Off ;

59 | ; Maintain hierarchy ; Off ;

60 | ; Bring out device-wide set/reset signals as ports ; Off ;

61 | ; Enable glitch filtering ; Off ;

62 | ; Do not write top level VHDL entity ; Off ;

63 | ; Disable detection of setup and hold time violations in the input registers of bi-directional pins ; Off ;

64 | ; Architecture name in VHDL output netlist ; structure ;

65 | ; Generate third-party EDA tool command script for RTL functional simulation ; Off ;

66 | ; Generate third-party EDA tool command script for gate-level simulation ; Off ;

67 | +---------------------------------------------------------------------------------------------------+---------------------------+

68 |

69 |

70 | +-------------------------------------------------------------------+

71 | ; Simulation Generated Files ;

72 | +-------------------------------------------------------------------+

73 | ; Generated Files ;

74 | +-------------------------------------------------------------------+

75 | ; D:/comber/ADPLL/simulation/modelsim/dpll_8_1200mv_85c_slow.vo ;

76 | ; D:/comber/ADPLL/simulation/modelsim/dpll_8_1200mv_0c_slow.vo ;

77 | ; D:/comber/ADPLL/simulation/modelsim/dpll_min_1200mv_0c_fast.vo ;

78 | ; D:/comber/ADPLL/simulation/modelsim/dpll.vo ;

79 | ; D:/comber/ADPLL/simulation/modelsim/dpll_8_1200mv_85c_v_slow.sdo ;

80 | ; D:/comber/ADPLL/simulation/modelsim/dpll_8_1200mv_0c_v_slow.sdo ;

81 | ; D:/comber/ADPLL/simulation/modelsim/dpll_min_1200mv_0c_v_fast.sdo ;

82 | ; D:/comber/ADPLL/simulation/modelsim/dpll_v.sdo ;

83 | +-------------------------------------------------------------------+

84 |

85 |

86 | +-----------------------------+

87 | ; EDA Netlist Writer Messages ;

88 | +-----------------------------+

89 | Info: *******************************************************************

90 | Info: Running Quartus II 64-Bit EDA Netlist Writer

91 | Info: Version 15.0.0 Build 145 04/22/2015 SJ Full Version

92 | Info: Processing started: Wed Sep 08 19:32:16 2021

93 | Info: Command: quartus_eda --read_settings_files=off --write_settings_files=off dpll -c dpll

94 | Warning (202000): An incorrect timescale is selected for the Verilog Output (.VO) file of this PLL design. It's required that the timescale should be 1 ps when simulating a PLL design in a third party EDA tool.

95 | Info (204019): Generated file dpll_8_1200mv_85c_slow.vo in folder "D:/comber/ADPLL/simulation/modelsim/" for EDA simulation tool

96 | Warning (202000): An incorrect timescale is selected for the Verilog Output (.VO) file of this PLL design. It's required that the timescale should be 1 ps when simulating a PLL design in a third party EDA tool.

97 | Info (204019): Generated file dpll_8_1200mv_0c_slow.vo in folder "D:/comber/ADPLL/simulation/modelsim/" for EDA simulation tool

98 | Warning (202000): An incorrect timescale is selected for the Verilog Output (.VO) file of this PLL design. It's required that the timescale should be 1 ps when simulating a PLL design in a third party EDA tool.

99 | Info (204019): Generated file dpll_min_1200mv_0c_fast.vo in folder "D:/comber/ADPLL/simulation/modelsim/" for EDA simulation tool

100 | Warning (202000): An incorrect timescale is selected for the Verilog Output (.VO) file of this PLL design. It's required that the timescale should be 1 ps when simulating a PLL design in a third party EDA tool.

101 | Info (204019): Generated file dpll.vo in folder "D:/comber/ADPLL/simulation/modelsim/" for EDA simulation tool

102 | Info (204019): Generated file dpll_8_1200mv_85c_v_slow.sdo in folder "D:/comber/ADPLL/simulation/modelsim/" for EDA simulation tool

103 | Info (204019): Generated file dpll_8_1200mv_0c_v_slow.sdo in folder "D:/comber/ADPLL/simulation/modelsim/" for EDA simulation tool

104 | Info (204019): Generated file dpll_min_1200mv_0c_v_fast.sdo in folder "D:/comber/ADPLL/simulation/modelsim/" for EDA simulation tool

105 | Info (204019): Generated file dpll_v.sdo in folder "D:/comber/ADPLL/simulation/modelsim/" for EDA simulation tool

106 | Info: Quartus II 64-Bit EDA Netlist Writer was successful. 0 errors, 4 warnings

107 | Info: Peak virtual memory: 4722 megabytes

108 | Info: Processing ended: Wed Sep 08 19:32:17 2021

109 | Info: Elapsed time: 00:00:01

110 | Info: Total CPU time (on all processors): 00:00:01

111 |

112 |

113 |

--------------------------------------------------------------------------------

/db/dpll.hier_info:

--------------------------------------------------------------------------------

1 | |dpll

2 | MainClock => MainClock.IN3

3 | SignalIn => SignalIn.IN1

4 | SignalOut <= SignalOut.DB_MAX_OUTPUT_PORT_TYPE

5 | SynchronousSignal <= phasecomparator:inst_ph_cmp.SynchronousSignal

6 | Positive <= Positive.DB_MAX_OUTPUT_PORT_TYPE

7 | Negative <= Negative.DB_MAX_OUTPUT_PORT_TYPE

8 | Lead <= Lead.DB_MAX_OUTPUT_PORT_TYPE

9 | Lag <= Lag.DB_MAX_OUTPUT_PORT_TYPE

10 | InputSignalEdge <= phasecomparator:inst_ph_cmp.InputSignalEdge

11 | OutputSignalEdge <= phasecomparator:inst_ph_cmp.OutputSignalEdge

12 | Lock <= phasecomparator:inst_ph_cmp.Lock

13 | PeriodCount[0] <= phasecomparator:inst_ph_cmp.PeriodCount

14 | PeriodCount[1] <= phasecomparator:inst_ph_cmp.PeriodCount

15 | PeriodCount[2] <= phasecomparator:inst_ph_cmp.PeriodCount

16 | PeriodCount[3] <= phasecomparator:inst_ph_cmp.PeriodCount

17 | PeriodCount[4] <= phasecomparator:inst_ph_cmp.PeriodCount

18 | PeriodCount[5] <= phasecomparator:inst_ph_cmp.PeriodCount

19 | PeriodCount[6] <= phasecomparator:inst_ph_cmp.PeriodCount

20 | PeriodCount[7] <= phasecomparator:inst_ph_cmp.PeriodCount

21 | DividerMaxValue[0] <= freqdivider:inst_freqdiv.DividerMaxValue

22 | DividerMaxValue[1] <= freqdivider:inst_freqdiv.DividerMaxValue

23 | DividerMaxValue[2] <= freqdivider:inst_freqdiv.DividerMaxValue

24 | DividerMaxValue[3] <= freqdivider:inst_freqdiv.DividerMaxValue

25 | DividerMaxValue[4] <= freqdivider:inst_freqdiv.DividerMaxValue

26 | DividerMaxValue[5] <= freqdivider:inst_freqdiv.DividerMaxValue

27 | DividerMaxValue[6] <= freqdivider:inst_freqdiv.DividerMaxValue

28 | DividerMaxValue[7] <= freqdivider:inst_freqdiv.DividerMaxValue

29 |

30 |

31 | |dpll|phasecomparator:inst_ph_cmp

32 | InputSignal => SynchronousSignal~reg0.DATAIN

33 | OutputSignal => Lead.IN1

34 | OutputSignal => OutputSignalEdgeDet[0].DATAIN

35 | OutputSignal => Lag.IN1

36 | MainClock => Lead~reg0.CLK

37 | MainClock => Lag~reg0.CLK

38 | MainClock => cnt[0].CLK

39 | MainClock => cnt[1].CLK

40 | MainClock => cnt[2].CLK

41 | MainClock => cnt[3].CLK

42 | MainClock => cnt[4].CLK

43 | MainClock => cnt[5].CLK

44 | MainClock => cnt[6].CLK

45 | MainClock => cnt[7].CLK

46 | MainClock => OutputSignalEdgeDet[0].CLK

47 | MainClock => OutputSignalEdgeDet[1].CLK

48 | MainClock => InputSignalEdgeDet[0].CLK

49 | MainClock => InputSignalEdgeDet[1].CLK

50 | MainClock => SynchronousSignal~reg0.CLK

51 | Lead <= Lead~reg0.DB_MAX_OUTPUT_PORT_TYPE

52 | Lag <= Lag~reg0.DB_MAX_OUTPUT_PORT_TYPE

53 | InputSignalEdge <= Equal0.DB_MAX_OUTPUT_PORT_TYPE

54 | OutputSignalEdge <= Equal1.DB_MAX_OUTPUT_PORT_TYPE

55 | Lock <= Lock~reg0.DB_MAX_OUTPUT_PORT_TYPE

56 | SynchronousSignal <= SynchronousSignal~reg0.DB_MAX_OUTPUT_PORT_TYPE

57 | PeriodCount[0] <= PeriodCount[0]~reg0.DB_MAX_OUTPUT_PORT_TYPE

58 | PeriodCount[1] <= PeriodCount[1]~reg0.DB_MAX_OUTPUT_PORT_TYPE

59 | PeriodCount[2] <= PeriodCount[2]~reg0.DB_MAX_OUTPUT_PORT_TYPE

60 | PeriodCount[3] <= PeriodCount[3]~reg0.DB_MAX_OUTPUT_PORT_TYPE

61 | PeriodCount[4] <= PeriodCount[4]~reg0.DB_MAX_OUTPUT_PORT_TYPE

62 | PeriodCount[5] <= PeriodCount[5]~reg0.DB_MAX_OUTPUT_PORT_TYPE

63 | PeriodCount[6] <= PeriodCount[6]~reg0.DB_MAX_OUTPUT_PORT_TYPE

64 | PeriodCount[7] <= PeriodCount[7]~reg0.DB_MAX_OUTPUT_PORT_TYPE

65 |

66 |

67 | |dpll|variableresetrandomwalkfilter:inst_zrwf

68 | MainClock => MainClock.IN1

69 | Lead => Lead.IN1

70 | Lag => Lag.IN1

71 | Positive <= Positive~reg0.DB_MAX_OUTPUT_PORT_TYPE

72 | Negative <= Negative~reg0.DB_MAX_OUTPUT_PORT_TYPE

73 | N_FilterCounter[0] <= N_FilterCounter[0]~reg0.DB_MAX_OUTPUT_PORT_TYPE

74 | N_FilterCounter[1] <= N_FilterCounter[1]~reg0.DB_MAX_OUTPUT_PORT_TYPE

75 | N_FilterCounter[2] <= N_FilterCounter[2]~reg0.DB_MAX_OUTPUT_PORT_TYPE

76 | N_FilterCounter[3] <= N_FilterCounter[3]~reg0.DB_MAX_OUTPUT_PORT_TYPE

77 | N_FilterCounter[4] <= N_FilterCounter[4]~reg0.DB_MAX_OUTPUT_PORT_TYPE

78 | N_FilterCounter[5] <= N_FilterCounter[5]~reg0.DB_MAX_OUTPUT_PORT_TYPE

79 | N_FilterCounter[6] <= N_FilterCounter[6]~reg0.DB_MAX_OUTPUT_PORT_TYPE

80 | N_FilterCounter[7] <= N_FilterCounter[7]~reg0.DB_MAX_OUTPUT_PORT_TYPE

81 | ResetterValue[0] <= ResetterValue.DB_MAX_OUTPUT_PORT_TYPE

82 | ResetterValue[1] <= WideOr2.DB_MAX_OUTPUT_PORT_TYPE

83 | ResetterValue[2] <= WideOr1.DB_MAX_OUTPUT_PORT_TYPE

84 | ResetterValue[3] <= WideOr0.DB_MAX_OUTPUT_PORT_TYPE

85 | ResetterValue[4] <= WideOr0.DB_MAX_OUTPUT_PORT_TYPE

86 | ResetterValue[5] <= WideOr0.DB_MAX_OUTPUT_PORT_TYPE

87 | ResetterValue[6] <= WideOr0.DB_MAX_OUTPUT_PORT_TYPE

88 | ResetterValue[7] <= WideOr0.DB_MAX_OUTPUT_PORT_TYPE

89 | ResetterCounter[0] <= ResetterCounter[0]~reg0.DB_MAX_OUTPUT_PORT_TYPE

90 | ResetterCounter[1] <= ResetterCounter[1]~reg0.DB_MAX_OUTPUT_PORT_TYPE

91 | ResetterCounter[2] <= ResetterCounter[2]~reg0.DB_MAX_OUTPUT_PORT_TYPE

92 | ResetterCounter[3] <= ResetterCounter[3]~reg0.DB_MAX_OUTPUT_PORT_TYPE

93 |

94 |

95 | |dpll|variableresetrandomwalkfilter:inst_zrwf|randomwalkfilter:inst_M_F

96 | MainClock => Negative~reg0.CLK

97 | MainClock => Positive~reg0.CLK

98 | MainClock => FilterCounter[0].CLK

99 | MainClock => FilterCounter[1].CLK

100 | MainClock => FilterCounter[2].CLK

101 | MainClock => FilterCounter[3].CLK

102 | MainClock => FilterCounter[4].CLK

103 | MainClock => FilterCounter[5].CLK

104 | MainClock => FilterCounter[6].CLK

105 | MainClock => FilterCounter[7].CLK

106 | Lead => FilterCounter.OUTPUTSELECT

107 | Lead => FilterCounter.OUTPUTSELECT

108 | Lead => FilterCounter.OUTPUTSELECT

109 | Lead => FilterCounter.OUTPUTSELECT

110 | Lead => FilterCounter.OUTPUTSELECT

111 | Lead => FilterCounter.OUTPUTSELECT

112 | Lead => FilterCounter.OUTPUTSELECT

113 | Lead => FilterCounter.OUTPUTSELECT

114 | Lag => FilterCounter.OUTPUTSELECT

115 | Lag => FilterCounter.OUTPUTSELECT

116 | Lag => FilterCounter.OUTPUTSELECT

117 | Lag => FilterCounter.OUTPUTSELECT

118 | Lag => FilterCounter.OUTPUTSELECT

119 | Lag => FilterCounter.OUTPUTSELECT

120 | Lag => FilterCounter.OUTPUTSELECT

121 | Lag => FilterCounter.OUTPUTSELECT

122 | Positive <= Positive~reg0.DB_MAX_OUTPUT_PORT_TYPE

123 | Negative <= Negative~reg0.DB_MAX_OUTPUT_PORT_TYPE

124 |

125 |

126 | |dpll|freqdivider:inst_freqdiv

127 | MainClock => overflow.CLK

128 | MainClock => DividerCounter[0]~reg0.CLK

129 | MainClock => DividerCounter[1]~reg0.CLK

130 | MainClock => DividerCounter[2]~reg0.CLK

131 | MainClock => DividerCounter[3]~reg0.CLK

132 | MainClock => DividerCounter[4]~reg0.CLK

133 | MainClock => DividerCounter[5]~reg0.CLK

134 | MainClock => DividerCounter[6]~reg0.CLK

135 | MainClock => DividerMaxValue[0]~reg0.CLK

136 | MainClock => DividerMaxValue[1]~reg0.CLK

137 | MainClock => DividerMaxValue[2]~reg0.CLK

138 | MainClock => DividerMaxValue[3]~reg0.CLK

139 | MainClock => DividerMaxValue[4]~reg0.CLK

140 | MainClock => DividerMaxValue[5]~reg0.CLK

141 | MainClock => DividerMaxValue[6]~reg0.CLK

142 | MainClock => DividerMaxValue[7]~reg0.CLK

143 | DividerMax[0] => DividerMaxValue[0]~reg0.DATAIN

144 | DividerMax[1] => DividerMaxValue[1]~reg0.DATAIN

145 | DividerMax[2] => DividerMaxValue[2]~reg0.DATAIN

146 | DividerMax[3] => DividerMaxValue[3]~reg0.DATAIN

147 | DividerMax[4] => DividerMaxValue[4]~reg0.DATAIN

148 | DividerMax[5] => DividerMaxValue[5]~reg0.DATAIN

149 | DividerMax[6] => DividerMaxValue[6]~reg0.DATAIN

150 | DividerMax[7] => DividerMaxValue[7]~reg0.DATAIN

151 | Positive => DividerCounter.OUTPUTSELECT

152 | Positive => DividerCounter.OUTPUTSELECT

153 | Positive => DividerCounter.OUTPUTSELECT

154 | Positive => DividerCounter.OUTPUTSELECT

155 | Positive => DividerCounter.OUTPUTSELECT

156 | Positive => DividerCounter.OUTPUTSELECT

157 | Positive => DividerCounter.OUTPUTSELECT

158 | Positive => always1.IN0

159 | Negative => DividerCounter.OUTPUTSELECT

160 | Negative => DividerCounter.OUTPUTSELECT

161 | Negative => DividerCounter.OUTPUTSELECT

162 | Negative => DividerCounter.OUTPUTSELECT

163 | Negative => DividerCounter.OUTPUTSELECT

164 | Negative => DividerCounter.OUTPUTSELECT

165 | Negative => DividerCounter.OUTPUTSELECT

166 | Negative => overflow.OUTPUTSELECT

167 | Negative => always1.IN1

168 | FrequencyOut <= FrequencyOut~reg0.DB_MAX_OUTPUT_PORT_TYPE

169 | DividerCounter[0] <= DividerCounter[0]~reg0.DB_MAX_OUTPUT_PORT_TYPE

170 | DividerCounter[1] <= DividerCounter[1]~reg0.DB_MAX_OUTPUT_PORT_TYPE

171 | DividerCounter[2] <= DividerCounter[2]~reg0.DB_MAX_OUTPUT_PORT_TYPE

172 | DividerCounter[3] <= DividerCounter[3]~reg0.DB_MAX_OUTPUT_PORT_TYPE

173 | DividerCounter[4] <= DividerCounter[4]~reg0.DB_MAX_OUTPUT_PORT_TYPE

174 | DividerCounter[5] <= DividerCounter[5]~reg0.DB_MAX_OUTPUT_PORT_TYPE

175 | DividerCounter[6] <= DividerCounter[6]~reg0.DB_MAX_OUTPUT_PORT_TYPE

176 | DividerMaxValue[0] <= DividerMaxValue[0]~reg0.DB_MAX_OUTPUT_PORT_TYPE

177 | DividerMaxValue[1] <= DividerMaxValue[1]~reg0.DB_MAX_OUTPUT_PORT_TYPE

178 | DividerMaxValue[2] <= DividerMaxValue[2]~reg0.DB_MAX_OUTPUT_PORT_TYPE

179 | DividerMaxValue[3] <= DividerMaxValue[3]~reg0.DB_MAX_OUTPUT_PORT_TYPE

180 | DividerMaxValue[4] <= DividerMaxValue[4]~reg0.DB_MAX_OUTPUT_PORT_TYPE

181 | DividerMaxValue[5] <= DividerMaxValue[5]~reg0.DB_MAX_OUTPUT_PORT_TYPE

182 | DividerMaxValue[6] <= DividerMaxValue[6]~reg0.DB_MAX_OUTPUT_PORT_TYPE

183 | DividerMaxValue[7] <= DividerMaxValue[7]~reg0.DB_MAX_OUTPUT_PORT_TYPE

184 |

185 |

186 |

--------------------------------------------------------------------------------

/output_files/dpll.flow.rpt:

--------------------------------------------------------------------------------

1 | Flow report for dpll

2 | Wed Sep 08 19:32:17 2021

3 | Quartus II 64-Bit Version 15.0.0 Build 145 04/22/2015 SJ Full Version

4 |

5 |

6 | ---------------------

7 | ; Table of Contents ;

8 | ---------------------

9 | 1. Legal Notice

10 | 2. Flow Summary

11 | 3. Flow Settings

12 | 4. Flow Non-Default Global Settings

13 | 5. Flow Elapsed Time

14 | 6. Flow OS Summary

15 | 7. Flow Log

16 | 8. Flow Messages

17 | 9. Flow Suppressed Messages

18 |

19 |

20 |

21 | ----------------

22 | ; Legal Notice ;

23 | ----------------

24 | Copyright (C) 1991-2015 Altera Corporation. All rights reserved.

25 | Your use of Altera Corporation's design tools, logic functions

26 | and other software and tools, and its AMPP partner logic

27 | functions, and any output files from any of the foregoing

28 | (including device programming or simulation files), and any

29 | associated documentation or information are expressly subject

30 | to the terms and conditions of the Altera Program License

31 | Subscription Agreement, the Altera Quartus II License Agreement,

32 | the Altera MegaCore Function License Agreement, or other

33 | applicable license agreement, including, without limitation,

34 | that your use is for the sole purpose of programming logic

35 | devices manufactured by Altera and sold by Altera or its

36 | authorized distributors. Please refer to the applicable

37 | agreement for further details.

38 |

39 |

40 |

41 | +----------------------------------------------------------------------------------+

42 | ; Flow Summary ;

43 | +------------------------------------+---------------------------------------------+

44 | ; Flow Status ; Successful - Wed Sep 08 19:32:17 2021 ;

45 | ; Quartus II 64-Bit Version ; 15.0.0 Build 145 04/22/2015 SJ Full Version ;

46 | ; Revision Name ; dpll ;

47 | ; Top-level Entity Name ; dpll ;

48 | ; Family ; Cyclone IV E ;

49 | ; Device ; EP4CE15F17C8 ;

50 | ; Timing Models ; Final ;

51 | ; Total logic elements ; 212 / 15,408 ( 1 % ) ;

52 | ; Total combinational functions ; 197 / 15,408 ( 1 % ) ;

53 | ; Dedicated logic registers ; 63 / 15,408 ( < 1 % ) ;

54 | ; Total registers ; 63 ;

55 | ; Total pins ; 27 / 166 ( 16 % ) ;

56 | ; Total virtual pins ; 0 ;

57 | ; Total memory bits ; 0 / 516,096 ( 0 % ) ;

58 | ; Embedded Multiplier 9-bit elements ; 0 / 112 ( 0 % ) ;

59 | ; Total PLLs ; 0 / 4 ( 0 % ) ;

60 | +------------------------------------+---------------------------------------------+

61 |

62 |

63 | +-----------------------------------------+

64 | ; Flow Settings ;

65 | +-------------------+---------------------+

66 | ; Option ; Setting ;

67 | +-------------------+---------------------+

68 | ; Start date & time ; 09/08/2021 19:31:46 ;

69 | ; Main task ; Compilation ;

70 | ; Revision Name ; dpll ;

71 | +-------------------+---------------------+

72 |

73 |

74 | +-----------------------------------------------------------------------------------------------------------------------------+

75 | ; Flow Non-Default Global Settings ;

76 | +--------------------------------------+---------------------------------------+---------------+-------------+----------------+

77 | ; Assignment Name ; Value ; Default Value ; Entity Name ; Section Id ;

78 | +--------------------------------------+---------------------------------------+---------------+-------------+----------------+

79 | ; COMPILER_SIGNATURE_ID ; 255543656947206.163110070635764 ; -- ; -- ; -- ;

80 | ; EDA_DESIGN_INSTANCE_NAME ; i1 ; -- ; -- ; -- ;

81 | ; EDA_NATIVELINK_SIMULATION_TEST_BENCH ; dpll ; -- ; -- ; eda_simulation ;

82 | ; EDA_OUTPUT_DATA_FORMAT ; Verilog Hdl ; -- ; -- ; eda_simulation ;

83 | ; EDA_SIMULATION_TOOL ; ModelSim-Altera (Verilog) ; ; -- ; -- ;

84 | ; EDA_TEST_BENCH_ENABLE_STATUS ; TEST_BENCH_MODE ; -- ; -- ; eda_simulation ;

85 | ; EDA_TEST_BENCH_FILE ; simulation/modelsim/dpll.vt ; -- ; -- ; -- ;

86 | ; EDA_TEST_BENCH_MODULE_NAME ; dpll_vlg_tst ; -- ; -- ; -- ;

87 | ; EDA_TEST_BENCH_NAME ; dpll ; -- ; -- ; eda_simulation ;

88 | ; EDA_TIME_SCALE ; 1 ns ; -- ; -- ; eda_simulation ;

89 | ; MAX_CORE_JUNCTION_TEMP ; 85 ; -- ; -- ; -- ;

90 | ; MIN_CORE_JUNCTION_TEMP ; 0 ; -- ; -- ; -- ;

91 | ; NOMINAL_CORE_SUPPLY_VOLTAGE ; 1.2V ; -- ; -- ; -- ;

92 | ; PARTITION_COLOR ; 16764057 ; -- ; -- ; Top ;

93 | ; PARTITION_FITTER_PRESERVATION_LEVEL ; PLACEMENT_AND_ROUTING ; -- ; -- ; Top ;

94 | ; PARTITION_NETLIST_TYPE ; SOURCE ; -- ; -- ; Top ;

95 | ; POWER_BOARD_THERMAL_MODEL ; None (CONSERVATIVE) ; -- ; -- ; -- ;

96 | ; POWER_PRESET_COOLING_SOLUTION ; 23 MM HEAT SINK WITH 200 LFPM AIRFLOW ; -- ; -- ; -- ;

97 | ; PROJECT_OUTPUT_DIRECTORY ; output_files ; -- ; -- ; -- ;

98 | +--------------------------------------+---------------------------------------+---------------+-------------+----------------+

99 |

100 |

101 | +-------------------------------------------------------------------------------------------------------------------------------+

102 | ; Flow Elapsed Time ;

103 | +---------------------------+--------------+-------------------------+---------------------+------------------------------------+

104 | ; Module Name ; Elapsed Time ; Average Processors Used ; Peak Virtual Memory ; Total CPU Time (on all processors) ;

105 | +---------------------------+--------------+-------------------------+---------------------+------------------------------------+

106 | ; Analysis & Synthesis ; 00:00:10 ; 1.0 ; 4859 MB ; 00:00:25 ;

107 | ; Fitter ; 00:00:07 ; 2.3 ; 5777 MB ; 00:00:09 ;

108 | ; Assembler ; 00:00:01 ; 1.0 ; 4746 MB ; 00:00:01 ;

109 | ; TimeQuest Timing Analyzer ; 00:00:02 ; 1.0 ; 4885 MB ; 00:00:02 ;

110 | ; EDA Netlist Writer ; 00:00:01 ; 1.0 ; 4714 MB ; 00:00:01 ;

111 | ; Total ; 00:00:21 ; -- ; -- ; 00:00:38 ;

112 | +---------------------------+--------------+-------------------------+---------------------+------------------------------------+

113 |

114 |

115 | +----------------------------------------------------------------------------------------+

116 | ; Flow OS Summary ;

117 | +---------------------------+------------------+-----------+------------+----------------+

118 | ; Module Name ; Machine Hostname ; OS Name ; OS Version ; Processor type ;

119 | +---------------------------+------------------+-----------+------------+----------------+

120 | ; Analysis & Synthesis ; THE-LEGION ; Windows 7 ; 6.2 ; x86_64 ;

121 | ; Fitter ; THE-LEGION ; Windows 7 ; 6.2 ; x86_64 ;

122 | ; Assembler ; THE-LEGION ; Windows 7 ; 6.2 ; x86_64 ;

123 | ; TimeQuest Timing Analyzer ; THE-LEGION ; Windows 7 ; 6.2 ; x86_64 ;

124 | ; EDA Netlist Writer ; THE-LEGION ; Windows 7 ; 6.2 ; x86_64 ;

125 | +---------------------------+------------------+-----------+------------+----------------+

126 |

127 |

128 | ------------

129 | ; Flow Log ;

130 | ------------

131 | quartus_map --read_settings_files=on --write_settings_files=off dpll -c dpll

132 | quartus_fit --read_settings_files=off --write_settings_files=off dpll -c dpll

133 | quartus_asm --read_settings_files=off --write_settings_files=off dpll -c dpll

134 | quartus_sta dpll -c dpll

135 | quartus_eda --read_settings_files=off --write_settings_files=off dpll -c dpll

136 |

137 |

138 |

139 |

--------------------------------------------------------------------------------

/db/alt_u_div_a4f.tdf:

--------------------------------------------------------------------------------

1 | --alt_u_div DEVICE_FAMILY="Cyclone IV E" LPM_PIPELINE=0 MAXIMIZE_SPEED=5 SKIP_BITS=0 WIDTH_D=4 WIDTH_N=8 WIDTH_Q=8 WIDTH_R=4 denominator numerator quotient remainder

2 | --VERSION_BEGIN 15.0 cbx_cycloneii 2015:04:22:18:04:07:SJ cbx_lpm_abs 2015:04:22:18:04:07:SJ cbx_lpm_add_sub 2015:04:22:18:04:07:SJ cbx_lpm_divide 2015:04:22:18:04:08:SJ cbx_mgl 2015:04:22:18:06:50:SJ cbx_stratix 2015:04:22:18:04:08:SJ cbx_stratixii 2015:04:22:18:04:08:SJ cbx_util_mgl 2015:04:22:18:04:08:SJ VERSION_END

3 |

4 |

5 | -- Copyright (C) 1991-2015 Altera Corporation. All rights reserved.

6 | -- Your use of Altera Corporation's design tools, logic functions

7 | -- and other software and tools, and its AMPP partner logic

8 | -- functions, and any output files from any of the foregoing

9 | -- (including device programming or simulation files), and any

10 | -- associated documentation or information are expressly subject

11 | -- to the terms and conditions of the Altera Program License

12 | -- Subscription Agreement, the Altera Quartus II License Agreement,

13 | -- the Altera MegaCore Function License Agreement, or other

14 | -- applicable license agreement, including, without limitation,

15 | -- that your use is for the sole purpose of programming logic

16 | -- devices manufactured by Altera and sold by Altera or its

17 | -- authorized distributors. Please refer to the applicable

18 | -- agreement for further details.

19 |

20 |

21 | FUNCTION add_sub_7pc (dataa[0..0], datab[0..0])

22 | RETURNS ( cout, result[0..0]);

23 | FUNCTION add_sub_8pc (dataa[1..0], datab[1..0])

24 | RETURNS ( cout, result[1..0]);

25 |

26 | --synthesis_resources = lut 33

27 | SUBDESIGN alt_u_div_a4f

28 | (

29 | denominator[3..0] : input;

30 | numerator[7..0] : input;

31 | quotient[7..0] : output;

32 | remainder[3..0] : output;

33 | )

34 | VARIABLE

35 | add_sub_0 : add_sub_7pc;

36 | add_sub_1 : add_sub_8pc;

37 | add_sub_2_result_int[3..0] : WIRE;

38 | add_sub_2_cout : WIRE;

39 | add_sub_2_dataa[2..0] : WIRE;

40 | add_sub_2_datab[2..0] : WIRE;

41 | add_sub_2_result[2..0] : WIRE;

42 | add_sub_3_result_int[4..0] : WIRE;

43 | add_sub_3_cout : WIRE;

44 | add_sub_3_dataa[3..0] : WIRE;

45 | add_sub_3_datab[3..0] : WIRE;

46 | add_sub_3_result[3..0] : WIRE;

47 | add_sub_4_result_int[5..0] : WIRE;

48 | add_sub_4_cout : WIRE;

49 | add_sub_4_dataa[4..0] : WIRE;

50 | add_sub_4_datab[4..0] : WIRE;

51 | add_sub_4_result[4..0] : WIRE;

52 | add_sub_5_result_int[5..0] : WIRE;

53 | add_sub_5_cout : WIRE;

54 | add_sub_5_dataa[4..0] : WIRE;

55 | add_sub_5_datab[4..0] : WIRE;

56 | add_sub_5_result[4..0] : WIRE;

57 | add_sub_6_result_int[5..0] : WIRE;

58 | add_sub_6_cout : WIRE;

59 | add_sub_6_dataa[4..0] : WIRE;

60 | add_sub_6_datab[4..0] : WIRE;

61 | add_sub_6_result[4..0] : WIRE;

62 | add_sub_7_result_int[5..0] : WIRE;

63 | add_sub_7_cout : WIRE;

64 | add_sub_7_dataa[4..0] : WIRE;

65 | add_sub_7_datab[4..0] : WIRE;

66 | add_sub_7_result[4..0] : WIRE;

67 | DenominatorIn[44..0] : WIRE;

68 | DenominatorIn_tmp[44..0] : WIRE;

69 | gnd_wire : WIRE;

70 | nose[71..0] : WIRE;

71 | NumeratorIn[71..0] : WIRE;

72 | NumeratorIn_tmp[71..0] : WIRE;

73 | prestg[39..0] : WIRE;

74 | quotient_tmp[7..0] : WIRE;

75 | sel[35..0] : WIRE;

76 | selnose[71..0] : WIRE;

77 | StageIn[44..0] : WIRE;

78 | StageIn_tmp[44..0] : WIRE;

79 | StageOut[39..0] : WIRE;

80 |

81 | BEGIN

82 | add_sub_0.dataa[0..0] = NumeratorIn[7..7];

83 | add_sub_0.datab[0..0] = DenominatorIn[0..0];

84 | add_sub_1.dataa[] = ( StageIn[5..5], NumeratorIn[14..14]);

85 | add_sub_1.datab[1..0] = DenominatorIn[6..5];

86 | add_sub_2_result_int[] = (0, add_sub_2_dataa[]) - (0, add_sub_2_datab[]);

87 | add_sub_2_result[] = add_sub_2_result_int[2..0];

88 | add_sub_2_cout = !add_sub_2_result_int[3];

89 | add_sub_2_dataa[] = ( StageIn[11..10], NumeratorIn[21..21]);

90 | add_sub_2_datab[] = DenominatorIn[12..10];

91 | add_sub_3_result_int[] = (0, add_sub_3_dataa[]) - (0, add_sub_3_datab[]);

92 | add_sub_3_result[] = add_sub_3_result_int[3..0];

93 | add_sub_3_cout = !add_sub_3_result_int[4];

94 | add_sub_3_dataa[] = ( StageIn[17..15], NumeratorIn[28..28]);

95 | add_sub_3_datab[] = DenominatorIn[18..15];

96 | add_sub_4_result_int[] = (0, add_sub_4_dataa[]) - (0, add_sub_4_datab[]);

97 | add_sub_4_result[] = add_sub_4_result_int[4..0];

98 | add_sub_4_cout = !add_sub_4_result_int[5];

99 | add_sub_4_dataa[] = ( StageIn[23..20], NumeratorIn[35..35]);

100 | add_sub_4_datab[] = DenominatorIn[24..20];

101 | add_sub_5_result_int[] = (0, add_sub_5_dataa[]) - (0, add_sub_5_datab[]);

102 | add_sub_5_result[] = add_sub_5_result_int[4..0];

103 | add_sub_5_cout = !add_sub_5_result_int[5];

104 | add_sub_5_dataa[] = ( StageIn[28..25], NumeratorIn[42..42]);

105 | add_sub_5_datab[] = DenominatorIn[29..25];

106 | add_sub_6_result_int[] = (0, add_sub_6_dataa[]) - (0, add_sub_6_datab[]);

107 | add_sub_6_result[] = add_sub_6_result_int[4..0];

108 | add_sub_6_cout = !add_sub_6_result_int[5];

109 | add_sub_6_dataa[] = ( StageIn[33..30], NumeratorIn[49..49]);

110 | add_sub_6_datab[] = DenominatorIn[34..30];

111 | add_sub_7_result_int[] = (0, add_sub_7_dataa[]) - (0, add_sub_7_datab[]);

112 | add_sub_7_result[] = add_sub_7_result_int[4..0];

113 | add_sub_7_cout = !add_sub_7_result_int[5];

114 | add_sub_7_dataa[] = ( StageIn[38..35], NumeratorIn[56..56]);

115 | add_sub_7_datab[] = DenominatorIn[39..35];

116 | DenominatorIn[] = DenominatorIn_tmp[];

117 | DenominatorIn_tmp[] = ( DenominatorIn[39..0], ( gnd_wire, denominator[]));

118 | gnd_wire = B"0";

119 | nose[] = ( B"00000000", add_sub_7_cout, B"00000000", add_sub_6_cout, B"00000000", add_sub_5_cout, B"00000000", add_sub_4_cout, B"00000000", add_sub_3_cout, B"00000000", add_sub_2_cout, B"00000000", add_sub_1.cout, B"00000000", add_sub_0.cout);

120 | NumeratorIn[] = NumeratorIn_tmp[];

121 | NumeratorIn_tmp[] = ( NumeratorIn[63..0], numerator[]);

122 | prestg[] = ( add_sub_7_result[], add_sub_6_result[], add_sub_5_result[], add_sub_4_result[], GND, add_sub_3_result[], B"00", add_sub_2_result[], B"000", add_sub_1.result[], B"0000", add_sub_0.result[]);

123 | quotient[] = quotient_tmp[];

124 | quotient_tmp[] = ( (! selnose[0..0]), (! selnose[9..9]), (! selnose[18..18]), (! selnose[27..27]), (! selnose[36..36]), (! selnose[45..45]), (! selnose[54..54]), (! selnose[63..63]));

125 | remainder[3..0] = StageIn[43..40];

126 | sel[] = ( gnd_wire, (sel[35..35] # DenominatorIn[43..43]), (sel[34..34] # DenominatorIn[42..42]), (sel[33..33] # DenominatorIn[41..41]), gnd_wire, (sel[31..31] # DenominatorIn[38..38]), (sel[30..30] # DenominatorIn[37..37]), (sel[29..29] # DenominatorIn[36..36]), gnd_wire, (sel[27..27] # DenominatorIn[33..33]), (sel[26..26] # DenominatorIn[32..32]), (sel[25..25] # DenominatorIn[31..31]), gnd_wire, (sel[23..23] # DenominatorIn[28..28]), (sel[22..22] # DenominatorIn[27..27]), (sel[21..21] # DenominatorIn[26..26]), gnd_wire, (sel[19..19] # DenominatorIn[23..23]), (sel[18..18] # DenominatorIn[22..22]), (sel[17..17] # DenominatorIn[21..21]), gnd_wire, (sel[15..15] # DenominatorIn[18..18]), (sel[14..14] # DenominatorIn[17..17]), (sel[13..13] # DenominatorIn[16..16]), gnd_wire, (sel[11..11] # DenominatorIn[13..13]), (sel[10..10] # DenominatorIn[12..12]), (sel[9..9] # DenominatorIn[11..11]), gnd_wire, (sel[7..7] # DenominatorIn[8..8]), (sel[6..6] # DenominatorIn[7..7]), (sel[5..5] # DenominatorIn[6..6]), gnd_wire, (sel[3..3] # DenominatorIn[3..3]), (sel[2..2] # DenominatorIn[2..2]), (sel[1..1] # DenominatorIn[1..1]));

127 | selnose[] = ( (! nose[71..71]), (! nose[70..70]), (! nose[69..69]), (! nose[68..68]), ((! nose[67..67]) # sel[35..35]), ((! nose[66..66]) # sel[34..34]), ((! nose[65..65]) # sel[33..33]), ((! nose[64..64]) # sel[32..32]), (! nose[63..63]), (! nose[62..62]), (! nose[61..61]), (! nose[60..60]), ((! nose[59..59]) # sel[31..31]), ((! nose[58..58]) # sel[30..30]), ((! nose[57..57]) # sel[29..29]), ((! nose[56..56]) # sel[28..28]), (! nose[55..55]), (! nose[54..54]), (! nose[53..53]), (! nose[52..52]), ((! nose[51..51]) # sel[27..27]), ((! nose[50..50]) # sel[26..26]), ((! nose[49..49]) # sel[25..25]), ((! nose[48..48]) # sel[24..24]), (! nose[47..47]), (! nose[46..46]), (! nose[45..45]), (! nose[44..44]), ((! nose[43..43]) # sel[23..23]), ((! nose[42..42]) # sel[22..22]), ((! nose[41..41]) # sel[21..21]), ((! nose[40..40]) # sel[20..20]), (! nose[39..39]), (! nose[38..38]), (! nose[37..37]), (! nose[36..36]), ((! nose[35..35]) # sel[19..19]), ((! nose[34..34]) # sel[18..18]), ((! nose[33..33]) # sel[17..17]), ((! nose[32..32]) # sel[16..16]), (! nose[31..31]), (! nose[30..30]), (! nose[29..29]), (! nose[28..28]), ((! nose[27..27]) # sel[15..15]), ((! nose[26..26]) # sel[14..14]), ((! nose[25..25]) # sel[13..13]), ((! nose[24..24]) # sel[12..12]), (! nose[23..23]), (! nose[22..22]), (! nose[21..21]), (! nose[20..20]), ((! nose[19..19]) # sel[11..11]), ((! nose[18..18]) # sel[10..10]), ((! nose[17..17]) # sel[9..9]), ((! nose[16..16]) # sel[8..8]), (! nose[15..15]), (! nose[14..14]), (! nose[13..13]), (! nose[12..12]), ((! nose[11..11]) # sel[7..7]), ((! nose[10..10]) # sel[6..6]), ((! nose[9..9]) # sel[5..5]), ((! nose[8..8]) # sel[4..4]), (! nose[7..7]), (! nose[6..6]), (! nose[5..5]), (! nose[4..4]), ((! nose[3..3]) # sel[3..3]), ((! nose[2..2]) # sel[2..2]), ((! nose[1..1]) # sel[1..1]), ((! nose[0..0]) # sel[0..0]));

128 | StageIn[] = StageIn_tmp[];

129 | StageIn_tmp[] = ( StageOut[39..0], B"00000");

130 | StageOut[] = ( ((( StageIn[38..35], NumeratorIn[56..56]) & selnose[63..63]) # (prestg[39..35] & (! selnose[63..63]))), ((( StageIn[33..30], NumeratorIn[49..49]) & selnose[54..54]) # (prestg[34..30] & (! selnose[54..54]))), ((( StageIn[28..25], NumeratorIn[42..42]) & selnose[45..45]) # (prestg[29..25] & (! selnose[45..45]))), ((( StageIn[23..20], NumeratorIn[35..35]) & selnose[36..36]) # (prestg[24..20] & (! selnose[36..36]))), ((( StageIn[18..15], NumeratorIn[28..28]) & selnose[27..27]) # (prestg[19..15] & (! selnose[27..27]))), ((( StageIn[13..10], NumeratorIn[21..21]) & selnose[18..18]) # (prestg[14..10] & (! selnose[18..18]))), ((( StageIn[8..5], NumeratorIn[14..14]) & selnose[9..9]) # (prestg[9..5] & (! selnose[9..9]))), ((( StageIn[3..0], NumeratorIn[7..7]) & selnose[0..0]) # (prestg[4..0] & (! selnose[0..0]))));

131 | END;

132 | --VALID FILE

133 |

--------------------------------------------------------------------------------

/db/dpll.cmp.logdb:

--------------------------------------------------------------------------------

1 | v1

2 | IO_RULES,NUM_PINS_NOT_EXCEED_LOC_AVAILABLE,INAPPLICABLE,IO_000001,Capacity Checks,Number of pins in an I/O bank should not exceed the number of locations available.,Critical,No Location assignments found.,,I/O,,

3 | IO_RULES,NUM_CLKS_NOT_EXCEED_CLKS_AVAILABLE,INAPPLICABLE,IO_000002,Capacity Checks,Number of clocks in an I/O bank should not exceed the number of clocks available.,Critical,No Global Signal assignments found.,,I/O,,