├── .cproject

├── .gitignore

├── .project

├── .settings

└── language.settings.xml

├── CMSIS

├── core

│ ├── arm_common_tables.h

│ ├── arm_const_structs.h

│ ├── arm_math.h

│ ├── core_cm0.h

│ ├── core_cm0plus.h

│ ├── core_cm3.h

│ ├── core_cm4.h

│ ├── core_cm4_simd.h

│ ├── core_cmFunc.h

│ ├── core_cmInstr.h

│ ├── core_sc000.h

│ └── core_sc300.h

└── device

│ ├── stm32f0xx.h

│ └── system_stm32f0xx.h

├── LinkerScript.ld

├── README.md

├── StdPeriph_Driver

├── Release_Notes.html

├── inc

│ ├── stm32f0xx_adc.h

│ ├── stm32f0xx_can.h

│ ├── stm32f0xx_cec.h

│ ├── stm32f0xx_comp.h

│ ├── stm32f0xx_conf.h

│ ├── stm32f0xx_crc.h

│ ├── stm32f0xx_crs.h

│ ├── stm32f0xx_dac.h

│ ├── stm32f0xx_dbgmcu.h

│ ├── stm32f0xx_dma.h

│ ├── stm32f0xx_exti.h

│ ├── stm32f0xx_flash.h

│ ├── stm32f0xx_gpio.h

│ ├── stm32f0xx_i2c.h

│ ├── stm32f0xx_iwdg.h

│ ├── stm32f0xx_misc.h

│ ├── stm32f0xx_pwr.h

│ ├── stm32f0xx_rcc.h

│ ├── stm32f0xx_rtc.h

│ ├── stm32f0xx_spi.h

│ ├── stm32f0xx_syscfg.h

│ ├── stm32f0xx_tim.h

│ ├── stm32f0xx_usart.h

│ └── stm32f0xx_wwdg.h

└── src

│ ├── stm32f0xx_adc.c

│ ├── stm32f0xx_can.c

│ ├── stm32f0xx_cec.c

│ ├── stm32f0xx_comp.c

│ ├── stm32f0xx_crc.c

│ ├── stm32f0xx_crs.c

│ ├── stm32f0xx_dac.c

│ ├── stm32f0xx_dbgmcu.c

│ ├── stm32f0xx_dma.c

│ ├── stm32f0xx_exti.c

│ ├── stm32f0xx_flash.c

│ ├── stm32f0xx_gpio.c

│ ├── stm32f0xx_i2c.c

│ ├── stm32f0xx_iwdg.c

│ ├── stm32f0xx_misc.c

│ ├── stm32f0xx_pwr.c

│ ├── stm32f0xx_rcc.c

│ ├── stm32f0xx_rtc.c

│ ├── stm32f0xx_spi.c

│ ├── stm32f0xx_syscfg.c

│ ├── stm32f0xx_tim.c

│ ├── stm32f0xx_usart.c

│ └── stm32f0xx_wwdg.c

├── dist

└── sensorsRaw.bin

├── hardware

├── neoimage_sensors small.brd

├── neoimage_sensors small.pdf

└── neoimage_sensors small.sch

├── inc

├── main.h

└── stm32f0xx_it.h

├── sensorsRaw Run.cfg

├── src

├── fix_fft.c

├── libfixmath_sqrt.c

├── main.c

├── output.c

├── syscalls.c

└── system_stm32f0xx.c

└── startup

└── startup_stm32.s

/.gitignore:

--------------------------------------------------------------------------------

1 | .DS_Store

2 | /Debug/

3 | /Release/

4 |

5 | #eclipse stuff

6 |

7 |

8 | .metadata

9 | bin/

10 | tmp/

11 | *.tmp

12 | *.bak

13 | *.swp

14 | *~.nib

15 | local.properties

16 | .loadpath

17 | .recommenders

18 |

19 | # External tool builders

20 | .externalToolBuilders/

21 |

22 | # Locally stored "Eclipse launch configurations"

23 | *.launch

24 |

25 | # PyDev specific (Python IDE for Eclipse)

26 | *.pydevproject

27 |

28 |

29 | # CDT- autotools

30 | .autotools

31 |

32 | # Java annotation processor (APT)

33 | .factorypath

34 |

35 | # PDT-specific (PHP Development Tools)

36 | .buildpath

37 |

38 | # sbteclipse plugin

39 | .target

40 |

41 | # Tern plugin

42 | .tern-project

43 |

44 | # TeXlipse plugin

45 | .texlipse

46 |

47 | # STS (Spring Tool Suite)

48 | .springBeans

49 |

50 | # Code Recommenders

51 | .recommenders/

52 |

53 | # Scala IDE specific (Scala & Java development for Eclipse)

54 | .cache-main

55 | .scala_dependencies

56 | .worksheet

57 |

58 |

59 |

--------------------------------------------------------------------------------

/.project:

--------------------------------------------------------------------------------

1 |

2 |

3 | sensorsRaw

4 |

5 |

6 |

7 |

8 |

9 | org.eclipse.cdt.managedbuilder.core.genmakebuilder

10 | clean,full,incremental,

11 |

12 |

13 |

14 |

15 | org.eclipse.cdt.managedbuilder.core.ScannerConfigBuilder

16 | full,incremental,

17 |

18 |

19 |

20 |

21 |

22 | org.eclipse.cdt.core.cnature

23 | com.st.stm32cube.ide.mcu.MCUSingleCpuProjectNature

24 | org.eclipse.cdt.managedbuilder.core.ScannerConfigNature

25 | com.st.stm32cube.ide.mcu.MCUSW4STM32ConvertedProjectNature

26 | org.eclipse.cdt.managedbuilder.core.managedBuildNature

27 |

28 |

29 |

--------------------------------------------------------------------------------

/.settings/language.settings.xml:

--------------------------------------------------------------------------------

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

25 |

26 |

27 |

--------------------------------------------------------------------------------

/CMSIS/core/arm_common_tables.h:

--------------------------------------------------------------------------------

1 | /* ----------------------------------------------------------------------

2 | * Copyright (C) 2010-2013 ARM Limited. All rights reserved.

3 | *

4 | * $Date: 17. January 2013

5 | * $Revision: V1.4.1

6 | *

7 | * Project: CMSIS DSP Library

8 | * Title: arm_common_tables.h

9 | *

10 | * Description: This file has extern declaration for common tables like Bitreverse, reciprocal etc which are used across different functions

11 | *

12 | * Target Processor: Cortex-M4/Cortex-M3

13 | *

14 | * Redistribution and use in source and binary forms, with or without

15 | * modification, are permitted provided that the following conditions

16 | * are met:

17 | * - Redistributions of source code must retain the above copyright

18 | * notice, this list of conditions and the following disclaimer.

19 | * - Redistributions in binary form must reproduce the above copyright

20 | * notice, this list of conditions and the following disclaimer in

21 | * the documentation and/or other materials provided with the

22 | * distribution.

23 | * - Neither the name of ARM LIMITED nor the names of its contributors

24 | * may be used to endorse or promote products derived from this

25 | * software without specific prior written permission.

26 | *

27 | * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

28 | * "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

29 | * LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS

30 | * FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE

31 | * COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT,

32 | * INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING,

33 | * BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES;

34 | * LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER

35 | * CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT

36 | * LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN

37 | * ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE

38 | * POSSIBILITY OF SUCH DAMAGE.

39 | * -------------------------------------------------------------------- */

40 |

41 | #ifndef _ARM_COMMON_TABLES_H

42 | #define _ARM_COMMON_TABLES_H

43 |

44 | #include "arm_math.h"

45 |

46 | extern const uint16_t armBitRevTable[1024];

47 | extern const q15_t armRecipTableQ15[64];

48 | extern const q31_t armRecipTableQ31[64];

49 | extern const q31_t realCoefAQ31[1024];

50 | extern const q31_t realCoefBQ31[1024];

51 | extern const float32_t twiddleCoef_16[32];

52 | extern const float32_t twiddleCoef_32[64];

53 | extern const float32_t twiddleCoef_64[128];

54 | extern const float32_t twiddleCoef_128[256];

55 | extern const float32_t twiddleCoef_256[512];

56 | extern const float32_t twiddleCoef_512[1024];

57 | extern const float32_t twiddleCoef_1024[2048];

58 | extern const float32_t twiddleCoef_2048[4096];

59 | extern const float32_t twiddleCoef_4096[8192];

60 | #define twiddleCoef twiddleCoef_4096

61 | extern const q31_t twiddleCoefQ31[6144];

62 | extern const q15_t twiddleCoefQ15[6144];

63 | extern const float32_t twiddleCoef_rfft_32[32];

64 | extern const float32_t twiddleCoef_rfft_64[64];

65 | extern const float32_t twiddleCoef_rfft_128[128];

66 | extern const float32_t twiddleCoef_rfft_256[256];

67 | extern const float32_t twiddleCoef_rfft_512[512];

68 | extern const float32_t twiddleCoef_rfft_1024[1024];

69 | extern const float32_t twiddleCoef_rfft_2048[2048];

70 | extern const float32_t twiddleCoef_rfft_4096[4096];

71 |

72 |

73 | #define ARMBITREVINDEXTABLE__16_TABLE_LENGTH ((uint16_t)20 )

74 | #define ARMBITREVINDEXTABLE__32_TABLE_LENGTH ((uint16_t)48 )

75 | #define ARMBITREVINDEXTABLE__64_TABLE_LENGTH ((uint16_t)56 )

76 | #define ARMBITREVINDEXTABLE_128_TABLE_LENGTH ((uint16_t)208 )

77 | #define ARMBITREVINDEXTABLE_256_TABLE_LENGTH ((uint16_t)440 )

78 | #define ARMBITREVINDEXTABLE_512_TABLE_LENGTH ((uint16_t)448 )

79 | #define ARMBITREVINDEXTABLE1024_TABLE_LENGTH ((uint16_t)1800)

80 | #define ARMBITREVINDEXTABLE2048_TABLE_LENGTH ((uint16_t)3808)

81 | #define ARMBITREVINDEXTABLE4096_TABLE_LENGTH ((uint16_t)4032)

82 |

83 | extern const uint16_t armBitRevIndexTable16[ARMBITREVINDEXTABLE__16_TABLE_LENGTH];

84 | extern const uint16_t armBitRevIndexTable32[ARMBITREVINDEXTABLE__32_TABLE_LENGTH];

85 | extern const uint16_t armBitRevIndexTable64[ARMBITREVINDEXTABLE__64_TABLE_LENGTH];

86 | extern const uint16_t armBitRevIndexTable128[ARMBITREVINDEXTABLE_128_TABLE_LENGTH];

87 | extern const uint16_t armBitRevIndexTable256[ARMBITREVINDEXTABLE_256_TABLE_LENGTH];

88 | extern const uint16_t armBitRevIndexTable512[ARMBITREVINDEXTABLE_512_TABLE_LENGTH];

89 | extern const uint16_t armBitRevIndexTable1024[ARMBITREVINDEXTABLE1024_TABLE_LENGTH];

90 | extern const uint16_t armBitRevIndexTable2048[ARMBITREVINDEXTABLE2048_TABLE_LENGTH];

91 | extern const uint16_t armBitRevIndexTable4096[ARMBITREVINDEXTABLE4096_TABLE_LENGTH];

92 |

93 | #endif /* ARM_COMMON_TABLES_H */

94 |

--------------------------------------------------------------------------------

/CMSIS/core/arm_const_structs.h:

--------------------------------------------------------------------------------

1 | /* ----------------------------------------------------------------------

2 | * Copyright (C) 2010-2013 ARM Limited. All rights reserved.

3 | *

4 | * $Date: 17. January 2013

5 | * $Revision: V1.4.1

6 | *

7 | * Project: CMSIS DSP Library

8 | * Title: arm_const_structs.h

9 | *

10 | * Description: This file has constant structs that are initialized for

11 | * user convenience. For example, some can be given as

12 | * arguments to the arm_cfft_f32() function.

13 | *

14 | * Target Processor: Cortex-M4/Cortex-M3

15 | *

16 | * Redistribution and use in source and binary forms, with or without

17 | * modification, are permitted provided that the following conditions

18 | * are met:

19 | * - Redistributions of source code must retain the above copyright

20 | * notice, this list of conditions and the following disclaimer.

21 | * - Redistributions in binary form must reproduce the above copyright

22 | * notice, this list of conditions and the following disclaimer in

23 | * the documentation and/or other materials provided with the

24 | * distribution.

25 | * - Neither the name of ARM LIMITED nor the names of its contributors

26 | * may be used to endorse or promote products derived from this

27 | * software without specific prior written permission.

28 | *

29 | * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

30 | * "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

31 | * LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS

32 | * FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE

33 | * COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT,

34 | * INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING,

35 | * BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES;

36 | * LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER

37 | * CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT

38 | * LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN

39 | * ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE

40 | * POSSIBILITY OF SUCH DAMAGE.

41 | * -------------------------------------------------------------------- */

42 |

43 | #ifndef _ARM_CONST_STRUCTS_H

44 | #define _ARM_CONST_STRUCTS_H

45 |

46 | #include "arm_math.h"

47 | #include "arm_common_tables.h"

48 |

49 | const arm_cfft_instance_f32 arm_cfft_sR_f32_len16 = {

50 | 16, twiddleCoef_16, armBitRevIndexTable16, ARMBITREVINDEXTABLE__16_TABLE_LENGTH

51 | };

52 |

53 | const arm_cfft_instance_f32 arm_cfft_sR_f32_len32 = {

54 | 32, twiddleCoef_32, armBitRevIndexTable32, ARMBITREVINDEXTABLE__32_TABLE_LENGTH

55 | };

56 |

57 | const arm_cfft_instance_f32 arm_cfft_sR_f32_len64 = {

58 | 64, twiddleCoef_64, armBitRevIndexTable64, ARMBITREVINDEXTABLE__64_TABLE_LENGTH

59 | };

60 |

61 | const arm_cfft_instance_f32 arm_cfft_sR_f32_len128 = {

62 | 128, twiddleCoef_128, armBitRevIndexTable128, ARMBITREVINDEXTABLE_128_TABLE_LENGTH

63 | };

64 |

65 | const arm_cfft_instance_f32 arm_cfft_sR_f32_len256 = {

66 | 256, twiddleCoef_256, armBitRevIndexTable256, ARMBITREVINDEXTABLE_256_TABLE_LENGTH

67 | };

68 |

69 | const arm_cfft_instance_f32 arm_cfft_sR_f32_len512 = {

70 | 512, twiddleCoef_512, armBitRevIndexTable512, ARMBITREVINDEXTABLE_512_TABLE_LENGTH

71 | };

72 |

73 | const arm_cfft_instance_f32 arm_cfft_sR_f32_len1024 = {

74 | 1024, twiddleCoef_1024, armBitRevIndexTable1024, ARMBITREVINDEXTABLE1024_TABLE_LENGTH

75 | };

76 |

77 | const arm_cfft_instance_f32 arm_cfft_sR_f32_len2048 = {

78 | 2048, twiddleCoef_2048, armBitRevIndexTable2048, ARMBITREVINDEXTABLE2048_TABLE_LENGTH

79 | };

80 |

81 | const arm_cfft_instance_f32 arm_cfft_sR_f32_len4096 = {

82 | 4096, twiddleCoef_4096, armBitRevIndexTable4096, ARMBITREVINDEXTABLE4096_TABLE_LENGTH

83 | };

84 |

85 | #endif

86 |

--------------------------------------------------------------------------------

/CMSIS/device/system_stm32f0xx.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file system_stm32f0xx.h

4 | * @author MCD Application Team

5 | * @version V1.5.0

6 | * @date 05-December-2014

7 | * @brief CMSIS Cortex-M0 Device Peripheral Access Layer System Header File.

8 | ******************************************************************************

9 | * @attention

10 | *

11 | * © COPYRIGHT 2014 STMicroelectronics

12 | *

13 | * Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

14 | * You may not use this file except in compliance with the License.

15 | * You may obtain a copy of the License at:

16 | *

17 | * http://www.st.com/software_license_agreement_liberty_v2

18 | *

19 | * Unless required by applicable law or agreed to in writing, software

20 | * distributed under the License is distributed on an "AS IS" BASIS,

21 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

22 | * See the License for the specific language governing permissions and

23 | * limitations under the License.

24 | *

25 | ******************************************************************************

26 | */

27 |

28 | /** @addtogroup CMSIS

29 | * @{

30 | */

31 |

32 | /** @addtogroup stm32f0xx_system

33 | * @{

34 | */

35 |

36 | /**

37 | * @brief Define to prevent recursive inclusion

38 | */

39 | #ifndef __SYSTEM_STM32F0XX_H

40 | #define __SYSTEM_STM32F0XX_H

41 |

42 | #ifdef __cplusplus

43 | extern "C" {

44 | #endif

45 |

46 | /** @addtogroup STM32F0xx_System_Includes

47 | * @{

48 | */

49 |

50 | /**

51 | * @}

52 | */

53 |

54 |

55 | /** @addtogroup STM32F0xx_System_Exported_types

56 | * @{

57 | */

58 |

59 | extern uint32_t SystemCoreClock; /*!< System Clock Frequency (Core Clock) */

60 |

61 | /**

62 | * @}

63 | */

64 |

65 | /** @addtogroup STM32F0xx_System_Exported_Constants

66 | * @{

67 | */

68 |

69 | /**

70 | * @}

71 | */

72 |

73 | /** @addtogroup STM32F0xx_System_Exported_Macros

74 | * @{

75 | */

76 |

77 | /**

78 | * @}

79 | */

80 |

81 | /** @addtogroup STM32F0xx_System_Exported_Functions

82 | * @{

83 | */

84 |

85 | extern void SystemInit(void);

86 | extern void SystemCoreClockUpdate(void);

87 | /**

88 | * @}

89 | */

90 |

91 | #ifdef __cplusplus

92 | }

93 | #endif

94 |

95 | #endif /*__SYSTEM_STM32F0XX_H */

96 |

97 | /**

98 | * @}

99 | */

100 |

101 | /**

102 | * @}

103 | */

104 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

105 |

--------------------------------------------------------------------------------

/LinkerScript.ld:

--------------------------------------------------------------------------------

1 | /*

2 | ******************************************************************************

3 | **

4 | ** File : LinkerScript.ld

5 | **

6 | ** Author : Auto-generated by Ac6 System Workbench

7 | **

8 | ** Abstract : Linker script for STM32F030F4Px Device from STM32F0 series

9 | ** 4Kbytes RAM

10 | ** 16Kbytes ROM

11 | **

12 | ** Set heap size, stack size and stack location according

13 | ** to application requirements.

14 | **

15 | ** Set memory bank area and size if external memory is used.

16 | **

17 | ** Target : STMicroelectronics STM32

18 | **

19 | ** Distribution: The file is distributed �as is,� without any warranty

20 | ** of any kind.

21 | **

22 | *****************************************************************************

23 | ** @attention

24 | **

25 | ** © COPYRIGHT(c) 2018 Ac6

26 | **

27 | ** Redistribution and use in source and binary forms, with or without modification,

28 | ** are permitted provided that the following conditions are met:

29 | ** 1. Redistributions of source code must retain the above copyright notice,

30 | ** this list of conditions and the following disclaimer.

31 | ** 2. Redistributions in binary form must reproduce the above copyright notice,

32 | ** this list of conditions and the following disclaimer in the documentation

33 | ** and/or other materials provided with the distribution.

34 | ** 3. Neither the name of Ac6 nor the names of its contributors

35 | ** may be used to endorse or promote products derived from this software

36 | ** without specific prior written permission.

37 | **

38 | ** THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

39 | ** AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE

40 | ** IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE

41 | ** DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE

42 | ** FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL

43 | ** DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR

44 | ** SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER

45 | ** CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY,

46 | ** OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

47 | ** OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

48 | **

49 | *****************************************************************************

50 | */

51 |

52 | /* Entry Point */

53 | ENTRY(Reset_Handler)

54 |

55 | /* Highest address of the user mode stack */

56 | _estack = 0x20001000; /* end of RAM */

57 |

58 | _Min_Heap_Size = 0; /* required amount of heap */

59 | _Min_Stack_Size = 0x400; /* required amount of stack */

60 |

61 | /* Memories definition */

62 | MEMORY

63 | {

64 | RAM (xrw) : ORIGIN = 0x20000000, LENGTH = 4K

65 | ROM (rx) : ORIGIN = 0x8000000, LENGTH = 16K

66 | }

67 |

68 | /* Sections */

69 | SECTIONS

70 | {

71 | /* The startup code into ROM memory */

72 | .isr_vector :

73 | {

74 | . = ALIGN(4);

75 | KEEP(*(.isr_vector)) /* Startup code */

76 | . = ALIGN(4);

77 | } >ROM

78 |

79 | /* The program code and other data into ROM memory */

80 | .text :

81 | {

82 | . = ALIGN(4);

83 | *(.text) /* .text sections (code) */

84 | *(.text*) /* .text* sections (code) */

85 | *(.glue_7) /* glue arm to thumb code */

86 | *(.glue_7t) /* glue thumb to arm code */

87 | *(.eh_frame)

88 |

89 | KEEP (*(.init))

90 | KEEP (*(.fini))

91 |

92 | . = ALIGN(4);

93 | _etext = .; /* define a global symbols at end of code */

94 | } >ROM

95 |

96 | /* Constant data into ROM memory*/

97 | .rodata :

98 | {

99 | . = ALIGN(4);

100 | *(.rodata) /* .rodata sections (constants, strings, etc.) */

101 | *(.rodata*) /* .rodata* sections (constants, strings, etc.) */

102 | . = ALIGN(4);

103 | } >ROM

104 |

105 | .ARM.extab : {

106 | . = ALIGN(4);

107 | *(.ARM.extab* .gnu.linkonce.armextab.*)

108 | . = ALIGN(4);

109 | } >ROM

110 |

111 | .ARM : {

112 | . = ALIGN(4);

113 | __exidx_start = .;

114 | *(.ARM.exidx*)

115 | __exidx_end = .;

116 | . = ALIGN(4);

117 | } >ROM

118 |

119 | .preinit_array :

120 | {

121 | . = ALIGN(4);

122 | PROVIDE_HIDDEN (__preinit_array_start = .);

123 | KEEP (*(.preinit_array*))

124 | PROVIDE_HIDDEN (__preinit_array_end = .);

125 | . = ALIGN(4);

126 | } >ROM

127 |

128 | .init_array :

129 | {

130 | . = ALIGN(4);

131 | PROVIDE_HIDDEN (__init_array_start = .);

132 | KEEP (*(SORT(.init_array.*)))

133 | KEEP (*(.init_array*))

134 | PROVIDE_HIDDEN (__init_array_end = .);

135 | . = ALIGN(4);

136 | } >ROM

137 |

138 | .fini_array :

139 | {

140 | . = ALIGN(4);

141 | PROVIDE_HIDDEN (__fini_array_start = .);

142 | KEEP (*(SORT(.fini_array.*)))

143 | KEEP (*(.fini_array*))

144 | PROVIDE_HIDDEN (__fini_array_end = .);

145 | . = ALIGN(4);

146 | } >ROM

147 |

148 | /* Used by the startup to initialize data */

149 | _sidata = LOADADDR(.data);

150 |

151 | /* Initialized data sections into RAM memory */

152 | .data :

153 | {

154 | . = ALIGN(4);

155 | _sdata = .; /* create a global symbol at data start */

156 | *(.data) /* .data sections */

157 | *(.data*) /* .data* sections */

158 |

159 | . = ALIGN(4);

160 | _edata = .; /* define a global symbol at data end */

161 | } >RAM AT> ROM

162 |

163 |

164 | /* Uninitialized data section into RAM memory */

165 | . = ALIGN(4);

166 | .bss :

167 | {

168 | /* This is used by the startup in order to initialize the .bss secion */

169 | _sbss = .; /* define a global symbol at bss start */

170 | __bss_start__ = _sbss;

171 | *(.bss)

172 | *(.bss*)

173 | *(COMMON)

174 |

175 | . = ALIGN(4);

176 | _ebss = .; /* define a global symbol at bss end */

177 | __bss_end__ = _ebss;

178 | } >RAM

179 |

180 | /* User_heap_stack section, used to check that there is enough RAM left */

181 | ._user_heap_stack :

182 | {

183 | . = ALIGN(8);

184 | PROVIDE ( end = . );

185 | PROVIDE ( _end = . );

186 | . = . + _Min_Heap_Size;

187 | . = . + _Min_Stack_Size;

188 | . = ALIGN(8);

189 | } >RAM

190 |

191 |

192 |

193 | /* Remove information from the compiler libraries */

194 | /DISCARD/ :

195 | {

196 | libc.a ( * )

197 | libm.a ( * )

198 | libgcc.a ( * )

199 | }

200 |

201 | .ARM.attributes 0 : { *(.ARM.attributes) }

202 | }

203 |

--------------------------------------------------------------------------------

/README.md:

--------------------------------------------------------------------------------

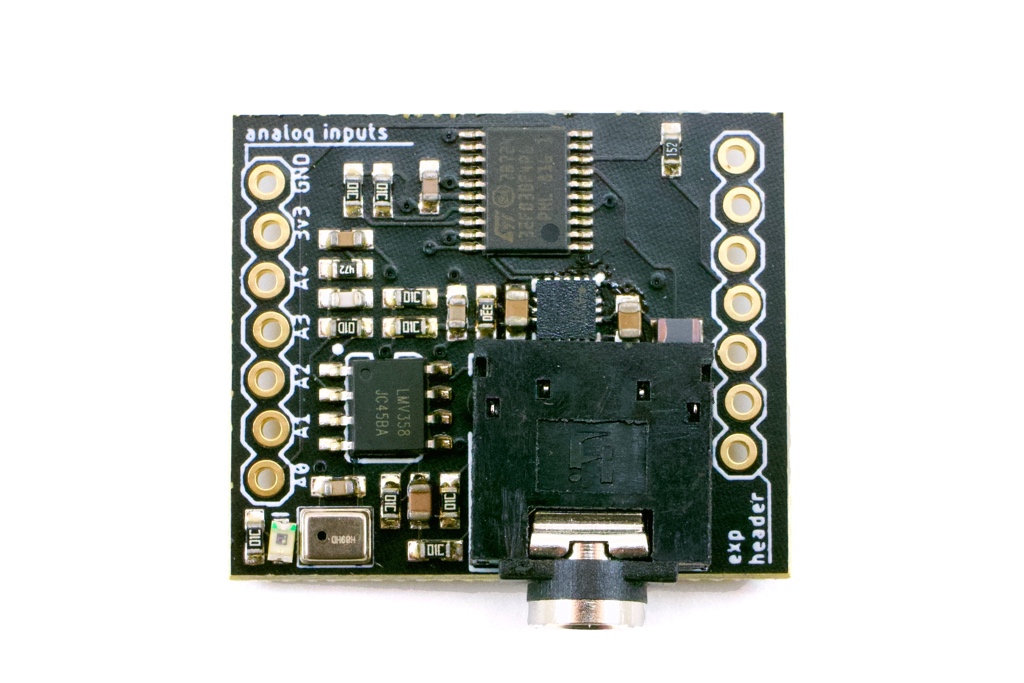

1 | Pixelblaze Sensor Expansion Board

2 | -------------------

3 |

4 |

5 |

6 | * A microphone and signal processing with frequency magnitude data ranging from 37Hz-10KHz designed to work in very loud environments

7 | * A 3-axis 16G accelerometer

8 | * An ambient light sensor

9 | * 5 analog inputs that can be used with potentiometers or other analog inputs

10 |

11 | [For sale on Tindie](https://www.tindie.com/products/12158/)! Pick up this board and/or a Pixelblaze! Make cool sound-reactive LED things, or get one and hack the firmware!

12 |

13 |

14 |

15 | I hope you find this useful or interesting. Maybe you hack your board? I'd be stoked to hear about it! Roll your own? Great! Turn it into a robot brain? Awesome!

16 |

17 | Shout out to Sparkfun, their boards were used in the initial prototype, and their Eagle files were really helpful!

18 |

19 | Shout out to [https://github.com/pyrohaz/STM32F0-PCD8544GraphicAnalyzer](https://github.com/pyrohaz/STM32F0-PCD8544GraphicAnalyzer) which does similar FFT stuff with a similar processor, even shares the fixed point FFT code in common!

20 |

21 | Non-Pixelblaze Usage

22 | -------------------

23 | Looking to use this with an Arduino or Teensy or something? You just need a free serial port at 115200 baud.

24 |

25 | The protocol is fairly simple:

26 |

27 | 1. Each frame starts with "SB1.0" including a null character (6 bytes).

28 | 2. The frequency information follows, as 32 x 16-bit unsigned integers.

29 | 3. Then is the audio energy average, max frequency magnitiude, max frequency Hz, all 3 as 16-bit unsigned ints.

30 | 4. Next the accelerometer information as 3 x 16-bit signed integers.

31 | 5. The data from the Light sensor is next, as a single 16-bit unsigned integer.

32 | 6. Followed by the 5 x 16-bit analog inputs (12-bit resolution, shifted up to 16 bits)

33 | 7. Finally "END" including a null character (4 bytes).

34 |

35 |

36 | License Information

37 | -------------------

38 | The hardware files are released under [Creative Commons ShareAlike 4.0 International](https://creativecommons.org/licenses/by-sa/4.0/) since the PCB is largely based off of Sparkfun boards with this license requirement.

39 |

40 | Distributed as-is; no warranty is given.

41 |

42 | The ElectroMage logo and wizard character is excluded from this license.

43 |

44 | The software is released under The MIT License.

45 |

46 | The MIT License

47 |

48 | Copyright (c) 2018 Ben Hencke

49 |

50 | Permission is hereby granted, free of charge, to any person obtaining a copy

51 | of this software and associated documentation files (the "Software"), to deal

52 | in the Software without restriction, including without limitation the rights

53 | to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

54 | copies of the Software, and to permit persons to whom the Software is

55 | furnished to do so, subject to the following conditions:

56 |

57 | The above copyright notice and this permission notice shall be included in

58 | all copies or substantial portions of the Software.

59 |

60 | THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

61 | IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

62 | FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

63 | AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

64 | LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

65 | OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN

66 | THE SOFTWARE.

67 |

--------------------------------------------------------------------------------

/StdPeriph_Driver/Release_Notes.html:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/simap/pixelblaze_sensor_board/15b3d271e0d6535965a68b15f057bac58a3154d7/StdPeriph_Driver/Release_Notes.html

--------------------------------------------------------------------------------

/StdPeriph_Driver/inc/stm32f0xx_cec.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file stm32f0xx_cec.h

4 | * @author MCD Application Team

5 | * @version V1.5.0

6 | * @date 05-December-2014

7 | * @brief This file contains all the functions prototypes for the CEC firmware

8 | * library, applicable only for STM32F051, STM32F042 and STM32F072 devices.

9 | ******************************************************************************

10 | * @attention

11 | *

12 | * © COPYRIGHT 2014 STMicroelectronics

13 | *

14 | * Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

15 | * You may not use this file except in compliance with the License.

16 | * You may obtain a copy of the License at:

17 | *

18 | * http://www.st.com/software_license_agreement_liberty_v2

19 | *

20 | * Unless required by applicable law or agreed to in writing, software

21 | * distributed under the License is distributed on an "AS IS" BASIS,

22 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

23 | * See the License for the specific language governing permissions and

24 | * limitations under the License.

25 | *

26 | ******************************************************************************

27 | */

28 |

29 | /* Define to prevent recursive inclusion -------------------------------------*/

30 | #ifndef __STM32F0XX_CEC_H

31 | #define __STM32F0XX_CEC_H

32 |

33 | #ifdef __cplusplus

34 | extern "C" {

35 | #endif

36 |

37 | /* Includes ------------------------------------------------------------------*/

38 | #include "stm32f0xx.h"

39 |

40 | /** @addtogroup STM32F0xx_StdPeriph_Driver

41 | * @{

42 | */

43 |

44 | /** @addtogroup CEC

45 | * @{

46 | */

47 | /* Exported types ------------------------------------------------------------*/

48 |

49 | /**

50 | * @brief CEC Init structure definition

51 | */

52 | typedef struct

53 | {

54 | uint32_t CEC_SignalFreeTime; /*!< Specifies the CEC Signal Free Time configuration.

55 | This parameter can be a value of @ref CEC_Signal_Free_Time */

56 | uint32_t CEC_RxTolerance; /*!< Specifies the CEC Reception Tolerance.

57 | This parameter can be a value of @ref CEC_RxTolerance */

58 | uint32_t CEC_StopReception; /*!< Specifies the CEC Stop Reception.

59 | This parameter can be a value of @ref CEC_Stop_Reception */

60 | uint32_t CEC_BitRisingError; /*!< Specifies the CEC Bit Rising Error generation.

61 | This parameter can be a value of @ref CEC_Bit_Rising_Error_Generation */

62 | uint32_t CEC_LongBitPeriodError; /*!< Specifies the CEC Long Bit Error generation.

63 | This parameter can be a value of @ref CEC_Long_Bit_Error_Generation */

64 | uint32_t CEC_BRDNoGen; /*!< Specifies the CEC Broadcast Error generation.

65 | This parameter can be a value of @ref CEC_BDR_No_Gen */

66 | uint32_t CEC_SFTOption; /*!< Specifies the CEC Signal Free Time option.

67 | This parameter can be a value of @ref CEC_SFT_Option */

68 |

69 | }CEC_InitTypeDef;

70 |

71 | /* Exported constants --------------------------------------------------------*/

72 |

73 | /** @defgroup CEC_Exported_Constants

74 | * @{

75 | */

76 |

77 | /** @defgroup CEC_Signal_Free_Time

78 | * @{

79 | */

80 | #define CEC_SignalFreeTime_Standard ((uint32_t)0x00000000) /*!< CEC Signal Free Time Standard */

81 | #define CEC_SignalFreeTime_1T ((uint32_t)0x00000001) /*!< CEC 1.5 nominal data bit periods */

82 | #define CEC_SignalFreeTime_2T ((uint32_t)0x00000002) /*!< CEC 2.5 nominal data bit periods */

83 | #define CEC_SignalFreeTime_3T ((uint32_t)0x00000003) /*!< CEC 3.5 nominal data bit periods */

84 | #define CEC_SignalFreeTime_4T ((uint32_t)0x00000004) /*!< CEC 4.5 nominal data bit periods */

85 | #define CEC_SignalFreeTime_5T ((uint32_t)0x00000005) /*!< CEC 5.5 nominal data bit periods */

86 | #define CEC_SignalFreeTime_6T ((uint32_t)0x00000006) /*!< CEC 6.5 nominal data bit periods */

87 | #define CEC_SignalFreeTime_7T ((uint32_t)0x00000007) /*!< CEC 7.5 nominal data bit periods */

88 |

89 | #define IS_CEC_SIGNAL_FREE_TIME(TIME) (((TIME) == CEC_SignalFreeTime_Standard) || \

90 | ((TIME) == CEC_SignalFreeTime_1T)|| \

91 | ((TIME) == CEC_SignalFreeTime_2T)|| \

92 | ((TIME) == CEC_SignalFreeTime_3T)|| \

93 | ((TIME) == CEC_SignalFreeTime_4T)|| \

94 | ((TIME) == CEC_SignalFreeTime_5T)|| \

95 | ((TIME) == CEC_SignalFreeTime_6T)|| \

96 | ((TIME) == CEC_SignalFreeTime_7T))

97 | /**

98 | * @}

99 | */

100 |

101 | /** @defgroup CEC_RxTolerance

102 | * @{

103 | */

104 | #define CEC_RxTolerance_Standard ((uint32_t)0x00000000) /*!< Standard Tolerance Margin */

105 | #define CEC_RxTolerance_Extended CEC_CFGR_RXTOL /*!< Extended Tolerance Margin */

106 |

107 | #define IS_CEC_RX_TOLERANCE(TOLERANCE) (((TOLERANCE) == CEC_RxTolerance_Standard) || \

108 | ((TOLERANCE) == CEC_RxTolerance_Extended))

109 | /**

110 | * @}

111 | */

112 |

113 | /** @defgroup CEC_Stop_Reception

114 | * @{

115 | */

116 | #define CEC_StopReception_Off ((uint32_t)0x00000000) /*!< No RX Stop on bit Rising Error (BRE) */

117 | #define CEC_StopReception_On CEC_CFGR_BRESTP /*!< RX Stop on bit Rising Error (BRE) */

118 |

119 | #define IS_CEC_STOP_RECEPTION(RECEPTION) (((RECEPTION) == CEC_StopReception_On) || \

120 | ((RECEPTION) == CEC_StopReception_Off))

121 | /**

122 | * @}

123 | */

124 |

125 | /** @defgroup CEC_Bit_Rising_Error_Generation

126 | * @{

127 | */

128 | #define CEC_BitRisingError_Off ((uint32_t)0x00000000) /*!< Bit Rising Error generation turned Off */

129 | #define CEC_BitRisingError_On CEC_CFGR_BREGEN /*!< Bit Rising Error generation turned On */

130 |

131 | #define IS_CEC_BIT_RISING_ERROR(ERROR) (((ERROR) == CEC_BitRisingError_Off) || \

132 | ((ERROR) == CEC_BitRisingError_On))

133 | /**

134 | * @}

135 | */

136 |

137 | /** @defgroup CEC_Long_Bit_Error_Generation

138 | * @{

139 | */

140 | #define CEC_LongBitPeriodError_Off ((uint32_t)0x00000000) /*!< Long Bit Period Error generation turned Off */

141 | #define CEC_LongBitPeriodError_On CEC_CFGR_LREGEN /*!< Long Bit Period Error generation turned On */

142 |

143 | #define IS_CEC_LONG_BIT_PERIOD_ERROR(ERROR) (((ERROR) == CEC_LongBitPeriodError_Off) || \

144 | ((ERROR) == CEC_LongBitPeriodError_On))

145 | /**

146 | * @}

147 | */

148 |

149 | /** @defgroup CEC_BDR_No_Gen

150 | * @{

151 | */

152 |

153 | #define CEC_BRDNoGen_Off ((uint32_t)0x00000000) /*!< Broadcast Bit Rising Error generation turned Off */

154 | #define CEC_BRDNoGen_On CEC_CFGR_BRDNOGEN /*!< Broadcast Bit Rising Error generation turned On */

155 |

156 | #define IS_CEC_BDR_NO_GEN_ERROR(ERROR) (((ERROR) == CEC_BRDNoGen_Off) || \

157 | ((ERROR) == CEC_BRDNoGen_On))

158 | /**

159 | * @}

160 | */

161 |

162 | /** @defgroup CEC_SFT_Option

163 | * @{

164 | */

165 | #define CEC_SFTOption_Off ((uint32_t)0x00000000) /*!< SFT option turned Off */

166 | #define CEC_SFTOption_On CEC_CFGR_SFTOPT /*!< SFT option turned On */

167 |

168 | #define IS_CEC_SFT_OPTION(OPTION) (((OPTION) == CEC_SFTOption_Off) || \

169 | ((OPTION) == CEC_SFTOption_On))

170 | /**

171 | * @}

172 | */

173 |

174 | /** @defgroup CEC_Own_Address

175 | * @{

176 | */

177 | #define IS_CEC_ADDRESS(ADDRESS) ((ADDRESS) < 0x10)

178 |

179 | /**

180 | * @}

181 | */

182 |

183 | /** @defgroup CEC_Interrupt_Configuration_definition

184 | * @{

185 | */

186 | #define CEC_IT_TXACKE CEC_IER_TXACKEIE

187 | #define CEC_IT_TXERR CEC_IER_TXERRIE

188 | #define CEC_IT_TXUDR CEC_IER_TXUDRIE

189 | #define CEC_IT_TXEND CEC_IER_TXENDIE

190 | #define CEC_IT_TXBR CEC_IER_TXBRIE

191 | #define CEC_IT_ARBLST CEC_IER_ARBLSTIE

192 | #define CEC_IT_RXACKE CEC_IER_RXACKEIE

193 | #define CEC_IT_LBPE CEC_IER_LBPEIE

194 | #define CEC_IT_SBPE CEC_IER_SBPEIE

195 | #define CEC_IT_BRE CEC_IER_BREIEIE

196 | #define CEC_IT_RXOVR CEC_IER_RXOVRIE

197 | #define CEC_IT_RXEND CEC_IER_RXENDIE

198 | #define CEC_IT_RXBR CEC_IER_RXBRIE

199 |

200 | #define IS_CEC_IT(IT) ((((IT) & (uint32_t)0xFFFFE000) == 0x00) && ((IT) != 0x00))

201 |

202 | #define IS_CEC_GET_IT(IT) (((IT) == CEC_IT_TXACKE) || \

203 | ((IT) == CEC_IT_TXERR)|| \

204 | ((IT) == CEC_IT_TXUDR)|| \

205 | ((IT) == CEC_IT_TXEND)|| \

206 | ((IT) == CEC_IT_TXBR)|| \

207 | ((IT) == CEC_IT_ARBLST)|| \

208 | ((IT) == CEC_IT_RXACKE)|| \

209 | ((IT) == CEC_IT_LBPE)|| \

210 | ((IT) == CEC_IT_SBPE)|| \

211 | ((IT) == CEC_IT_BRE)|| \

212 | ((IT) == CEC_IT_RXOVR)|| \

213 | ((IT) == CEC_IT_RXEND)|| \

214 | ((IT) == CEC_IT_RXBR))

215 | /**

216 | * @}

217 | */

218 |

219 | /** @defgroup CEC_ISR_register_flags_definition

220 | * @{

221 | */

222 | #define CEC_FLAG_TXACKE CEC_ISR_TXACKE

223 | #define CEC_FLAG_TXERR CEC_ISR_TXERR

224 | #define CEC_FLAG_TXUDR CEC_ISR_TXUDR

225 | #define CEC_FLAG_TXEND CEC_ISR_TXEND

226 | #define CEC_FLAG_TXBR CEC_ISR_TXBR

227 | #define CEC_FLAG_ARBLST CEC_ISR_ARBLST

228 | #define CEC_FLAG_RXACKE CEC_ISR_RXACKE

229 | #define CEC_FLAG_LBPE CEC_ISR_LBPE

230 | #define CEC_FLAG_SBPE CEC_ISR_SBPE

231 | #define CEC_FLAG_BRE CEC_ISR_BRE

232 | #define CEC_FLAG_RXOVR CEC_ISR_RXOVR

233 | #define CEC_FLAG_RXEND CEC_ISR_RXEND

234 | #define CEC_FLAG_RXBR CEC_ISR_RXBR

235 |

236 | #define IS_CEC_CLEAR_FLAG(FLAG) ((((FLAG) & (uint32_t)0xFFFFE000) == 0x00) && ((FLAG) != 0x00))

237 |

238 | #define IS_CEC_GET_FLAG(FLAG) (((FLAG) == CEC_FLAG_TXACKE) || \

239 | ((FLAG) == CEC_FLAG_TXERR)|| \

240 | ((FLAG) == CEC_FLAG_TXUDR)|| \

241 | ((FLAG) == CEC_FLAG_TXEND)|| \

242 | ((FLAG) == CEC_FLAG_TXBR)|| \

243 | ((FLAG) == CEC_FLAG_ARBLST)|| \

244 | ((FLAG) == CEC_FLAG_RXACKE)|| \

245 | ((FLAG) == CEC_FLAG_LBPE)|| \

246 | ((FLAG) == CEC_FLAG_SBPE)|| \

247 | ((FLAG) == CEC_FLAG_BRE)|| \

248 | ((FLAG) == CEC_FLAG_RXOVR)|| \

249 | ((FLAG) == CEC_FLAG_RXEND)|| \

250 | ((FLAG) == CEC_FLAG_RXBR))

251 | /**

252 | * @}

253 | */

254 |

255 | /**

256 | * @}

257 | */

258 |

259 | /* Exported macro ------------------------------------------------------------*/

260 | /* Exported functions ------------------------------------------------------- */

261 |

262 | /* Function used to set the CEC configuration to the default reset state *****/

263 | void CEC_DeInit(void);

264 |

265 | /* CEC_Initialization and Configuration functions *****************************/

266 | void CEC_Init(CEC_InitTypeDef* CEC_InitStruct);

267 | void CEC_StructInit(CEC_InitTypeDef* CEC_InitStruct);

268 | void CEC_Cmd(FunctionalState NewState);

269 | void CEC_ListenModeCmd(FunctionalState NewState);

270 | void CEC_OwnAddressConfig(uint8_t CEC_OwnAddress);

271 | void CEC_OwnAddressClear(void);

272 |

273 | /* CEC_Data transfers functions ***********************************************/

274 | void CEC_SendData(uint8_t Data);

275 | uint8_t CEC_ReceiveData(void);

276 | void CEC_StartOfMessage(void);

277 | void CEC_EndOfMessage(void);

278 |

279 | /* CEC_Interrupts and flags management functions ******************************/

280 | void CEC_ITConfig(uint16_t CEC_IT, FunctionalState NewState);

281 | FlagStatus CEC_GetFlagStatus(uint16_t CEC_FLAG);

282 | void CEC_ClearFlag(uint32_t CEC_FLAG);

283 | ITStatus CEC_GetITStatus(uint16_t CEC_IT);

284 | void CEC_ClearITPendingBit(uint16_t CEC_IT);

285 |

286 | #ifdef __cplusplus

287 | }

288 | #endif

289 |

290 | #endif /* __STM32F0XX_CEC_H */

291 |

292 | /**

293 | * @}

294 | */

295 |

296 | /**

297 | * @}

298 | */

299 |

300 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

301 |

--------------------------------------------------------------------------------

/StdPeriph_Driver/inc/stm32f0xx_comp.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file stm32f0xx_comp.h

4 | * @author MCD Application Team

5 | * @version V1.5.0

6 | * @date 05-December-2014

7 | * @brief This file contains all the functions prototypes for the COMP firmware

8 | * library, applicable only for STM32F051 and STM32F072 devices.

9 | ******************************************************************************

10 | * @attention

11 | *

12 | * © COPYRIGHT 2014 STMicroelectronics

13 | *

14 | * Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

15 | * You may not use this file except in compliance with the License.

16 | * You may obtain a copy of the License at:

17 | *

18 | * http://www.st.com/software_license_agreement_liberty_v2

19 | *

20 | * Unless required by applicable law or agreed to in writing, software

21 | * distributed under the License is distributed on an "AS IS" BASIS,

22 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

23 | * See the License for the specific language governing permissions and

24 | * limitations under the License.

25 | *

26 | ******************************************************************************

27 | */

28 |

29 | /* Define to prevent recursive inclusion -------------------------------------*/

30 | #ifndef __STM32F0XX_COMP_H

31 | #define __STM32F0XX_COMP_H

32 |

33 | #ifdef __cplusplus

34 | extern "C" {

35 | #endif

36 |

37 | /* Includes ------------------------------------------------------------------*/

38 | #include "stm32f0xx.h"

39 |

40 | /** @addtogroup STM32F0xx_StdPeriph_Driver

41 | * @{

42 | */

43 |

44 | /** @addtogroup COMP

45 | * @{

46 | */

47 |

48 | /* Exported types ------------------------------------------------------------*/

49 |

50 | /**

51 | * @brief COMP Init structure definition

52 | */

53 |

54 | typedef struct

55 | {

56 |

57 | uint32_t COMP_InvertingInput; /*!< Selects the inverting input of the comparator.

58 | This parameter can be a value of @ref COMP_InvertingInput */

59 |

60 | uint32_t COMP_Output; /*!< Selects the output redirection of the comparator.

61 | This parameter can be a value of @ref COMP_Output */

62 |

63 | uint32_t COMP_OutputPol; /*!< Selects the output polarity of the comparator.

64 | This parameter can be a value of @ref COMP_OutputPolarity */

65 |

66 | uint32_t COMP_Hysteresis; /*!< Selects the hysteresis voltage of the comparator.

67 | This parameter can be a value of @ref COMP_Hysteresis */

68 |

69 | uint32_t COMP_Mode; /*!< Selects the operating mode of the comparator

70 | and allows to adjust the speed/consumption.

71 | This parameter can be a value of @ref COMP_Mode */

72 |

73 | }COMP_InitTypeDef;

74 |

75 | /* Exported constants --------------------------------------------------------*/

76 |

77 | /** @defgroup COMP_Exported_Constants

78 | * @{

79 | */

80 |

81 | /** @defgroup COMP_Selection

82 | * @{

83 | */

84 |

85 | #define COMP_Selection_COMP1 ((uint32_t)0x00000000) /*!< COMP1 Selection */

86 | #define COMP_Selection_COMP2 ((uint32_t)0x00000010) /*!< COMP2 Selection */

87 |

88 | #define IS_COMP_ALL_PERIPH(PERIPH) (((PERIPH) == COMP_Selection_COMP1) || \

89 | ((PERIPH) == COMP_Selection_COMP2))

90 |

91 | /**

92 | * @}

93 | */

94 |

95 | /** @defgroup COMP_InvertingInput

96 | * @{

97 | */

98 |

99 | #define COMP_InvertingInput_1_4VREFINT ((uint32_t)0x00000000) /*!< 1/4 VREFINT connected to comparator inverting input */

100 | #define COMP_InvertingInput_1_2VREFINT COMP_CSR_COMP1INSEL_0 /*!< 1/2 VREFINT connected to comparator inverting input */

101 | #define COMP_InvertingInput_3_4VREFINT COMP_CSR_COMP1INSEL_1 /*!< 3/4 VREFINT connected to comparator inverting input */

102 | #define COMP_InvertingInput_VREFINT ((uint32_t)0x00000030) /*!< VREFINT connected to comparator inverting input */

103 | #define COMP_InvertingInput_DAC1 COMP_CSR_COMP1INSEL_2 /*!< DAC1_OUT (PA4) connected to comparator inverting input */

104 | #define COMP_InvertingInput_DAC2 ((uint32_t)0x00000050) /*!< DAC2_OUT (PA5) connected to comparator inverting input, applicable only for STM32F072 devices */

105 | #define COMP_InvertingInput_IO ((uint32_t)0x00000060) /*!< I/O (PA0 for COMP1 and PA2 for COMP2) connected to comparator inverting input */

106 |

107 | #define IS_COMP_INVERTING_INPUT(INPUT) (((INPUT) == COMP_InvertingInput_1_4VREFINT) || \

108 | ((INPUT) == COMP_InvertingInput_1_2VREFINT) || \

109 | ((INPUT) == COMP_InvertingInput_3_4VREFINT) || \

110 | ((INPUT) == COMP_InvertingInput_VREFINT) || \

111 | ((INPUT) == COMP_InvertingInput_DAC1) || \

112 | ((INPUT) == COMP_InvertingInput_DAC2) || \

113 | ((INPUT) == COMP_InvertingInput_1_4VREFINT) || \

114 | ((INPUT) == COMP_InvertingInput_IO))

115 | /**

116 | * @}

117 | */

118 |

119 | /** @defgroup COMP_Output

120 | * @{

121 | */

122 |

123 | #define COMP_Output_None ((uint32_t)0x00000000) /*!< COMP output isn't connected to other peripherals */

124 | #define COMP_Output_TIM1BKIN COMP_CSR_COMP1OUTSEL_0 /*!< COMP output connected to TIM1 Break Input (BKIN) */

125 | #define COMP_Output_TIM1IC1 COMP_CSR_COMP1OUTSEL_1 /*!< COMP output connected to TIM1 Input Capture 1 */

126 | #define COMP_Output_TIM1OCREFCLR ((uint32_t)0x00000300) /*!< COMP output connected to TIM1 OCREF Clear */

127 | #define COMP_Output_TIM2IC4 COMP_CSR_COMP1OUTSEL_2 /*!< COMP output connected to TIM2 Input Capture 4 */

128 | #define COMP_Output_TIM2OCREFCLR ((uint32_t)0x00000500) /*!< COMP output connected to TIM2 OCREF Clear */

129 | #define COMP_Output_TIM3IC1 ((uint32_t)0x00000600) /*!< COMP output connected to TIM3 Input Capture 1 */

130 | #define COMP_Output_TIM3OCREFCLR COMP_CSR_COMP1OUTSEL /*!< COMP output connected to TIM3 OCREF Clear */

131 |

132 |

133 | #define IS_COMP_OUTPUT(OUTPUT) (((OUTPUT) == COMP_Output_None) || \

134 | ((OUTPUT) == COMP_Output_TIM1BKIN) || \

135 | ((OUTPUT) == COMP_Output_TIM1IC1) || \

136 | ((OUTPUT) == COMP_Output_TIM1OCREFCLR) || \

137 | ((OUTPUT) == COMP_Output_TIM2IC4) || \

138 | ((OUTPUT) == COMP_Output_TIM2OCREFCLR) || \

139 | ((OUTPUT) == COMP_Output_TIM3IC1) || \

140 | ((OUTPUT) == COMP_Output_TIM3OCREFCLR))

141 | /**

142 | * @}

143 | */

144 |

145 | /** @defgroup COMP_OutputPolarity

146 | * @{

147 | */

148 | #define COMP_OutputPol_NonInverted ((uint32_t)0x00000000) /*!< COMP output on GPIO isn't inverted */

149 | #define COMP_OutputPol_Inverted COMP_CSR_COMP1POL /*!< COMP output on GPIO is inverted */

150 |

151 | #define IS_COMP_OUTPUT_POL(POL) (((POL) == COMP_OutputPol_NonInverted) || \

152 | ((POL) == COMP_OutputPol_Inverted))

153 |

154 | /**

155 | * @}

156 | */

157 |

158 | /** @defgroup COMP_Hysteresis

159 | * @{

160 | */

161 | /* Please refer to the electrical characteristics in the device datasheet for

162 | the hysteresis level */

163 | #define COMP_Hysteresis_No 0x00000000 /*!< No hysteresis */

164 | #define COMP_Hysteresis_Low COMP_CSR_COMP1HYST_0 /*!< Hysteresis level low */

165 | #define COMP_Hysteresis_Medium COMP_CSR_COMP1HYST_1 /*!< Hysteresis level medium */

166 | #define COMP_Hysteresis_High COMP_CSR_COMP1HYST /*!< Hysteresis level high */

167 |

168 | #define IS_COMP_HYSTERESIS(HYSTERESIS) (((HYSTERESIS) == COMP_Hysteresis_No) || \

169 | ((HYSTERESIS) == COMP_Hysteresis_Low) || \

170 | ((HYSTERESIS) == COMP_Hysteresis_Medium) || \

171 | ((HYSTERESIS) == COMP_Hysteresis_High))

172 | /**

173 | * @}

174 | */

175 |

176 | /** @defgroup COMP_Mode

177 | * @{

178 | */

179 | /* Please refer to the electrical characteristics in the device datasheet for

180 | the power consumption values */

181 | #define COMP_Mode_HighSpeed 0x00000000 /*!< High Speed */

182 | #define COMP_Mode_MediumSpeed COMP_CSR_COMP1MODE_0 /*!< Medium Speed */

183 | #define COMP_Mode_LowPower COMP_CSR_COMP1MODE_1 /*!< Low power mode */

184 | #define COMP_Mode_UltraLowPower COMP_CSR_COMP1MODE /*!< Ultra-low power mode */

185 |

186 | #define IS_COMP_MODE(MODE) (((MODE) == COMP_Mode_UltraLowPower) || \

187 | ((MODE) == COMP_Mode_LowPower) || \

188 | ((MODE) == COMP_Mode_MediumSpeed) || \

189 | ((MODE) == COMP_Mode_HighSpeed))

190 | /**

191 | * @}

192 | */

193 |

194 | /** @defgroup COMP_OutputLevel

195 | * @{

196 | */

197 | /* When output polarity is not inverted, comparator output is high when

198 | the non-inverting input is at a higher voltage than the inverting input */

199 | #define COMP_OutputLevel_High COMP_CSR_COMP1OUT

200 | /* When output polarity is not inverted, comparator output is low when

201 | the non-inverting input is at a lower voltage than the inverting input*/

202 | #define COMP_OutputLevel_Low ((uint32_t)0x00000000)

203 |

204 | /**

205 | * @}

206 | */

207 |

208 | /**

209 | * @}

210 | */

211 |

212 | /* Exported macro ------------------------------------------------------------*/

213 | /* Exported functions ------------------------------------------------------- */

214 |

215 | /* Function used to set the COMP configuration to the default reset state ****/

216 | void COMP_DeInit(void);

217 |

218 | /* Initialization and Configuration functions *********************************/

219 | void COMP_Init(uint32_t COMP_Selection, COMP_InitTypeDef* COMP_InitStruct);

220 | void COMP_StructInit(COMP_InitTypeDef* COMP_InitStruct);

221 | void COMP_Cmd(uint32_t COMP_Selection, FunctionalState NewState);

222 | void COMP_SwitchCmd(FunctionalState NewState);

223 | uint32_t COMP_GetOutputLevel(uint32_t COMP_Selection);

224 |

225 | /* Window mode control function ***********************************************/

226 | void COMP_WindowCmd(FunctionalState NewState);

227 |

228 | /* COMP configuration locking function ****************************************/

229 | void COMP_LockConfig(uint32_t COMP_Selection);

230 |

231 | #ifdef __cplusplus

232 | }

233 | #endif

234 |

235 | #endif /*__STM32F0XX_COMP_H */

236 |

237 | /**

238 | * @}

239 | */

240 |

241 | /**

242 | * @}

243 | */

244 |

245 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

246 |

--------------------------------------------------------------------------------

/StdPeriph_Driver/inc/stm32f0xx_conf.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file Project/STM32F0xx_StdPeriph_Templates/stm32f0xx_conf.h

4 | * @author MCD Application Team

5 | * @version V1.5.0

6 | * @date 05-December-2014

7 | * @brief Library configuration file.

8 | ******************************************************************************

9 | * @attention

10 | *

11 | * © COPYRIGHT 2014 STMicroelectronics

12 | *

13 | * Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

14 | * You may not use this file except in compliance with the License.

15 | * You may obtain a copy of the License at:

16 | *

17 | * http://www.st.com/software_license_agreement_liberty_v2

18 | *

19 | * Unless required by applicable law or agreed to in writing, software

20 | * distributed under the License is distributed on an "AS IS" BASIS,

21 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

22 | * See the License for the specific language governing permissions and

23 | * limitations under the License.

24 | *

25 | ******************************************************************************

26 | */

27 |

28 | /* Define to prevent recursive inclusion -------------------------------------*/

29 | #ifndef __STM32F0XX_CONF_H

30 | #define __STM32F0XX_CONF_H

31 |

32 | /* Includes ------------------------------------------------------------------*/

33 | /* Comment the line below to disable peripheral header file inclusion */

34 | #include "stm32f0xx_adc.h"

35 | #include "stm32f0xx_can.h"

36 | #include "stm32f0xx_cec.h"

37 | #include "stm32f0xx_crc.h"

38 | #include "stm32f0xx_crs.h"

39 | #include "stm32f0xx_comp.h"

40 | #include "stm32f0xx_dac.h"

41 | #include "stm32f0xx_dbgmcu.h"

42 | #include "stm32f0xx_dma.h"

43 | #include "stm32f0xx_exti.h"

44 | #include "stm32f0xx_flash.h"

45 | #include "stm32f0xx_gpio.h"

46 | #include "stm32f0xx_syscfg.h"

47 | #include "stm32f0xx_i2c.h"

48 | #include "stm32f0xx_iwdg.h"

49 | #include "stm32f0xx_pwr.h"

50 | #include "stm32f0xx_rcc.h"

51 | #include "stm32f0xx_rtc.h"

52 | #include "stm32f0xx_spi.h"

53 | #include "stm32f0xx_tim.h"

54 | #include "stm32f0xx_usart.h"

55 | #include "stm32f0xx_wwdg.h"

56 | #include "stm32f0xx_misc.h" /* High level functions for NVIC and SysTick (add-on to CMSIS functions) */

57 |

58 | /* Exported types ------------------------------------------------------------*/

59 | /* Exported constants --------------------------------------------------------*/

60 | /* Uncomment the line below to expanse the "assert_param" macro in the

61 | Standard Peripheral Library drivers code */

62 | /* #define USE_FULL_ASSERT 1 */

63 |

64 | /* Exported macro ------------------------------------------------------------*/

65 | #ifdef USE_FULL_ASSERT

66 |

67 | /**

68 | * @brief The assert_param macro is used for function's parameters check.

69 | * @param expr: If expr is false, it calls assert_failed function which reports

70 | * the name of the source file and the source line number of the call

71 | * that failed. If expr is true, it returns no value.

72 | * @retval None

73 | */

74 | #define assert_param(expr) ((expr) ? (void)0 : assert_failed((uint8_t *)__FILE__, __LINE__))

75 | /* Exported functions ------------------------------------------------------- */

76 | void assert_failed(uint8_t* file, uint32_t line);

77 | #else

78 | #define assert_param(expr) ((void)0)

79 | #endif /* USE_FULL_ASSERT */

80 |

81 | #endif /* __STM32F0XX_CONF_H */

82 |

83 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

84 |

--------------------------------------------------------------------------------

/StdPeriph_Driver/inc/stm32f0xx_crc.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file stm32f0xx_crc.h

4 | * @author MCD Application Team

5 | * @version V1.5.0

6 | * @date 05-December-2014

7 | * @brief This file contains all the functions prototypes for the CRC firmware

8 | * library.

9 | ******************************************************************************

10 | * @attention

11 | *

12 | * © COPYRIGHT 2014 STMicroelectronics

13 | *

14 | * Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

15 | * You may not use this file except in compliance with the License.

16 | * You may obtain a copy of the License at:

17 | *

18 | * http://www.st.com/software_license_agreement_liberty_v2

19 | *

20 | * Unless required by applicable law or agreed to in writing, software

21 | * distributed under the License is distributed on an "AS IS" BASIS,

22 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

23 | * See the License for the specific language governing permissions and

24 | * limitations under the License.

25 | *

26 | ******************************************************************************

27 | */

28 |

29 | /* Define to prevent recursive inclusion -------------------------------------*/

30 | #ifndef __STM32F0XX_CRC_H

31 | #define __STM32F0XX_CRC_H

32 |

33 | #ifdef __cplusplus

34 | extern "C" {

35 | #endif

36 |

37 | /*!< Includes ----------------------------------------------------------------*/

38 | #include "stm32f0xx.h"

39 |

40 | /** @addtogroup STM32F0xx_StdPeriph_Driver

41 | * @{

42 | */

43 |

44 | /** @addtogroup CRC

45 | * @{

46 | */

47 |

48 | /* Exported types ------------------------------------------------------------*/

49 | /* Exported constants --------------------------------------------------------*/

50 |

51 | /** @defgroup CRC_ReverseInputData

52 | * @{

53 | */

54 | #define CRC_ReverseInputData_No ((uint32_t)0x00000000) /*!< No reverse operation of Input Data */

55 | #define CRC_ReverseInputData_8bits CRC_CR_REV_IN_0 /*!< Reverse operation of Input Data on 8 bits */

56 | #define CRC_ReverseInputData_16bits CRC_CR_REV_IN_1 /*!< Reverse operation of Input Data on 16 bits */

57 | #define CRC_ReverseInputData_32bits CRC_CR_REV_IN /*!< Reverse operation of Input Data on 32 bits */

58 |

59 | #define IS_CRC_REVERSE_INPUT_DATA(DATA) (((DATA) == CRC_ReverseInputData_No) || \

60 | ((DATA) == CRC_ReverseInputData_8bits) || \

61 | ((DATA) == CRC_ReverseInputData_16bits) || \

62 | ((DATA) == CRC_ReverseInputData_32bits))

63 |

64 | /**

65 | * @}

66 | */

67 |

68 | /** @defgroup CRC_PolynomialSize

69 | * @brief Only applicable for STM32F042 and STM32F072 devices

70 | * @{

71 | */

72 | #define CRC_PolSize_7 CRC_CR_POLSIZE /*!< 7-bit polynomial for CRC calculation */

73 | #define CRC_PolSize_8 CRC_CR_POLSIZE_1 /*!< 8-bit polynomial for CRC calculation */

74 | #define CRC_PolSize_16 CRC_CR_POLSIZE_0 /*!< 16-bit polynomial for CRC calculation */

75 | #define CRC_PolSize_32 ((uint32_t)0x00000000)/*!< 32-bit polynomial for CRC calculation */

76 |

77 | #define IS_CRC_POL_SIZE(SIZE) (((SIZE) == CRC_PolSize_7) || \

78 | ((SIZE) == CRC_PolSize_8) || \

79 | ((SIZE) == CRC_PolSize_16) || \

80 | ((SIZE) == CRC_PolSize_32))

81 |

82 | /**

83 | * @}

84 | */

85 |

86 | /* Exported macro ------------------------------------------------------------*/

87 | /* Exported functions ------------------------------------------------------- */

88 | /* Configuration of the CRC computation unit **********************************/

89 | void CRC_DeInit(void);

90 | void CRC_ResetDR(void);

91 | void CRC_PolynomialSizeSelect(uint32_t CRC_PolSize); /*!< Only applicable for STM32F042 and STM32F072 devices */

92 | void CRC_ReverseInputDataSelect(uint32_t CRC_ReverseInputData);

93 | void CRC_ReverseOutputDataCmd(FunctionalState NewState);

94 | void CRC_SetInitRegister(uint32_t CRC_InitValue);

95 | void CRC_SetPolynomial(uint32_t CRC_Pol); /*!< Only applicable for STM32F042 and STM32F072 devices */

96 |

97 | /* CRC computation ************************************************************/

98 | uint32_t CRC_CalcCRC(uint32_t CRC_Data);

99 | uint32_t CRC_CalcCRC16bits(uint16_t CRC_Data); /*!< Only applicable for STM32F042 and STM32F072 devices */

100 | uint32_t CRC_CalcCRC8bits(uint8_t CRC_Data); /*!< Only applicable for STM32F042 and STM32F072 devices */

101 | uint32_t CRC_CalcBlockCRC(uint32_t pBuffer[], uint32_t BufferLength);

102 | uint32_t CRC_GetCRC(void);

103 |

104 | /* Independent register (IDR) access (write/read) *****************************/

105 | void CRC_SetIDRegister(uint8_t CRC_IDValue);

106 | uint8_t CRC_GetIDRegister(void);

107 |

108 | #ifdef __cplusplus

109 | }

110 | #endif

111 |

112 | #endif /* __STM32F0XX_CRC_H */

113 |

114 | /**

115 | * @}

116 | */

117 |

118 | /**

119 | * @}

120 | */

121 |

122 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

123 |

--------------------------------------------------------------------------------

/StdPeriph_Driver/inc/stm32f0xx_crs.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file stm32f0xx_crs.h

4 | * @author MCD Application Team

5 | * @version V1.5.0

6 | * @date 05-December-2014

7 | * @brief This file contains all the functions prototypes for the CRS firmware

8 | * library, applicable only for STM32F042 and STM32F072 devices.

9 | ******************************************************************************

10 | * @attention

11 | *

12 | * © COPYRIGHT 2014 STMicroelectronics

13 | *

14 | * Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

15 | * You may not use this file except in compliance with the License.

16 | * You may obtain a copy of the License at:

17 | *

18 | * http://www.st.com/software_license_agreement_liberty_v2

19 | *

20 | * Unless required by applicable law or agreed to in writing, software

21 | * distributed under the License is distributed on an "AS IS" BASIS,

22 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

23 | * See the License for the specific language governing permissions and

24 | * limitations under the License.

25 | *

26 | ******************************************************************************

27 | */

28 |

29 | /* Define to prevent recursive inclusion -------------------------------------*/

30 | #ifndef __STM32F0XX_CRS_H

31 | #define __STM32F0XX_CRS_H

32 |

33 | #ifdef __cplusplus

34 | extern "C" {

35 | #endif

36 |

37 | /*!< Includes ----------------------------------------------------------------*/

38 | #include "stm32f0xx.h"

39 |

40 | /** @addtogroup STM32F0xx_StdPeriph_Driver

41 | * @{

42 | */

43 |

44 | /** @addtogroup CRS

45 | * @{

46 | */

47 |

48 | /* Exported types ------------------------------------------------------------*/

49 | /* Exported constants --------------------------------------------------------*/

50 |

51 | /** @defgroup CRS_Interrupt_Sources

52 | * @{

53 | */

54 | #define CRS_IT_SYNCOK CRS_ISR_SYNCOKF /*!< SYNC event OK */

55 | #define CRS_IT_SYNCWARN CRS_ISR_SYNCWARNF /*!< SYNC warning */

56 | #define CRS_IT_ERR CRS_ISR_ERRF /*!< error */

57 | #define CRS_IT_ESYNC CRS_ISR_ESYNCF /*!< Expected SYNC */

58 | #define CRS_IT_TRIMOVF CRS_ISR_TRIMOVF /*!< Trimming overflow or underflow */

59 | #define CRS_IT_SYNCERR CRS_ISR_SYNCERR /*!< SYNC error */

60 | #define CRS_IT_SYNCMISS CRS_ISR_SYNCMISS /*!< SYNC missed*/

61 |

62 | #define IS_CRS_IT(IT) (((IT) == CRS_IT_SYNCOK) || ((IT) == CRS_IT_SYNCWARN) || \

63 | ((IT) == CRS_IT_ERR) || ((IT) == CRS_IT_ESYNC))

64 |

65 | #define IS_CRS_GET_IT(IT) (((IT) == CRS_IT_SYNCOK) || ((IT) == CRS_IT_SYNCWARN) || \

66 | ((IT) == CRS_IT_ERR) || ((IT) == CRS_IT_ESYNC) || \

67 | ((IT) == CRS_IT_TRIMOVF) || ((IT) == CRS_IT_SYNCERR) || \

68 | ((IT) == CRS_IT_SYNCMISS))

69 |

70 | #define IS_CRS_CLEAR_IT(IT) ((IT) != 0x00)

71 |

72 | /**

73 | * @}

74 | */

75 |

76 | /** @defgroup CRS_Flags

77 | * @{

78 | */

79 | #define CRS_FLAG_SYNCOK CRS_ISR_SYNCOKF /*!< SYNC event OK */

80 | #define CRS_FLAG_SYNCWARN CRS_ISR_SYNCWARNF /*!< SYNC warning */

81 | #define CRS_FLAG_ERR CRS_ISR_ERRF /*!< error */

82 | #define CRS_FLAG_ESYNC CRS_ISR_ESYNCF /*!< Expected SYNC */

83 | #define CRS_FLAG_TRIMOVF CRS_ISR_TRIMOVF /*!< Trimming overflow or underflow */

84 | #define CRS_FLAG_SYNCERR CRS_ISR_SYNCERR /*!< SYNC error */

85 | #define CRS_FLAG_SYNCMISS CRS_ISR_SYNCMISS /*!< SYNC missed*/

86 |

87 | #define IS_CRS_FLAG(FLAG) (((FLAG) == CRS_FLAG_SYNCOK) || ((FLAG) == CRS_FLAG_SYNCWARN) || \

88 | ((FLAG) == CRS_FLAG_ERR) || ((FLAG) == CRS_FLAG_ESYNC) || \

89 | ((FLAG) == CRS_FLAG_TRIMOVF) || ((FLAG) == CRS_FLAG_SYNCERR) || \

90 | ((FLAG) == CRS_FLAG_SYNCMISS))

91 |

92 | /**

93 | * @}

94 | */

95 |

96 | /** @defgroup CRS_Synchro_Source

97 | * @{

98 | */

99 | #define CRS_SYNCSource_GPIO ((uint32_t)0x00) /*!< Synchro Signal soucre GPIO */

100 | #define CRS_SYNCSource_LSE CRS_CFGR_SYNCSRC_0 /*!< Synchro Signal source LSE */

101 | #define CRS_SYNCSource_USB CRS_CFGR_SYNCSRC_1 /*!< Synchro Signal source USB SOF */

102 |

103 | #define IS_CRS_SYNC_SOURCE(SOURCE) (((SOURCE) == CRS_SYNCSource_GPIO) || \

104 | ((SOURCE) == CRS_SYNCSource_LSE) ||\

105 | ((SOURCE) == CRS_SYNCSource_USB))

106 | /**

107 | * @}

108 | */

109 |

110 | /** @defgroup CRS_SynchroDivider

111 | * @{

112 | */

113 | #define CRS_SYNC_Div1 ((uint32_t)0x00) /*!< Synchro Signal not divided */

114 | #define CRS_SYNC_Div2 CRS_CFGR_SYNCDIV_0 /*!< Synchro Signal divided by 2 */

115 | #define CRS_SYNC_Div4 CRS_CFGR_SYNCDIV_1 /*!< Synchro Signal divided by 4 */

116 | #define CRS_SYNC_Div8 (CRS_CFGR_SYNCDIV_1 | CRS_CFGR_SYNCDIV_0) /*!< Synchro Signal divided by 8 */

117 | #define CRS_SYNC_Div16 CRS_CFGR_SYNCDIV_2 /*!< Synchro Signal divided by 16 */

118 | #define CRS_SYNC_Div32 (CRS_CFGR_SYNCDIV_2 | CRS_CFGR_SYNCDIV_0) /*!< Synchro Signal divided by 32 */

119 | #define CRS_SYNC_Div64 (CRS_CFGR_SYNCDIV_2 | CRS_CFGR_SYNCDIV_1) /*!< Synchro Signal divided by 64 */

120 | #define CRS_SYNC_Div128 CRS_CFGR_SYNCDIV /*!< Synchro Signal divided by 128 */

121 |

122 | #define IS_CRS_SYNC_DIV(DIV) (((DIV) == CRS_SYNC_Div1) || ((DIV) == CRS_SYNC_Div2) ||\

123 | ((DIV) == CRS_SYNC_Div4) || ((DIV) == CRS_SYNC_Div8) || \

124 | ((DIV) == CRS_SYNC_Div16) || ((DIV) == CRS_SYNC_Div32) || \

125 | ((DIV) == CRS_SYNC_Div64) || ((DIV) == CRS_SYNC_Div128))

126 | /**

127 | * @}

128 | */

129 |

130 | /** @defgroup CRS_SynchroPolarity

131 | * @{

132 | */

133 | #define CRS_SYNCPolarity_Rising ((uint32_t)0x00) /*!< Synchro Active on rising edge */

134 | #define CRS_SYNCPolarity_Falling CRS_CFGR_SYNCPOL /*!< Synchro Active on falling edge */

135 |

136 | #define IS_CRS_SYNC_POLARITY(POLARITY) (((POLARITY) == CRS_SYNCPolarity_Rising) || \

137 | ((POLARITY) == CRS_SYNCPolarity_Falling))

138 | /**

139 | * @}

140 | */

141 |

142 |

143 |

144 | /* Exported macro ------------------------------------------------------------*/

145 | /* Exported functions ------------------------------------------------------- */

146 | /* Configuration of the CRS **********************************/

147 | void CRS_DeInit(void);

148 | void CRS_AdjustHSI48CalibrationValue(uint8_t CRS_HSI48CalibrationValue);

149 | void CRS_FrequencyErrorCounterCmd(FunctionalState NewState);

150 | void CRS_AutomaticCalibrationCmd(FunctionalState NewState);

151 | void CRS_SoftwareSynchronizationGenerate(void);

152 | void CRS_FrequencyErrorCounterReload(uint32_t CRS_ReloadValue);

153 | void CRS_FrequencyErrorLimitConfig(uint8_t CRS_ErrorLimitValue);

154 | void CRS_SynchronizationPrescalerConfig(uint32_t CRS_Prescaler);

155 | void CRS_SynchronizationSourceConfig(uint32_t CRS_Source);

156 | void CRS_SynchronizationPolarityConfig(uint32_t CRS_Polarity);

157 | uint32_t CRS_GetReloadValue(void);

158 | uint32_t CRS_GetHSI48CalibrationValue(void);

159 | uint32_t CRS_GetFrequencyErrorValue(void);

160 | uint32_t CRS_GetFrequencyErrorDirection(void);

161 |

162 | /* Interrupts and flags management functions **********************************/

163 | void CRS_ITConfig(uint32_t CRS_IT, FunctionalState NewState);

164 | FlagStatus CRS_GetFlagStatus(uint32_t CRS_FLAG);

165 | void CRS_ClearFlag(uint32_t CRS_FLAG);

166 | ITStatus CRS_GetITStatus(uint32_t CRS_IT);

167 | void CRS_ClearITPendingBit(uint32_t CRS_IT);

168 |

169 | #ifdef __cplusplus

170 | }

171 | #endif

172 |

173 | #endif /* __STM32F0XX_CRS_H */

174 |

175 | /**

176 | * @}

177 | */

178 |

179 | /**

180 | * @}

181 | */

182 |

183 | /************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

184 |

--------------------------------------------------------------------------------

/StdPeriph_Driver/inc/stm32f0xx_dbgmcu.h:

--------------------------------------------------------------------------------

1 | /**

2 | ******************************************************************************

3 | * @file stm32f0xx_dbgmcu.h

4 | * @author MCD Application Team

5 | * @version V1.5.0

6 | * @date 05-December-2014

7 | * @brief This file contains all the functions prototypes for the DBGMCU firmware

8 | * library.

9 | ******************************************************************************

10 | * @attention

11 | *

12 | * © COPYRIGHT 2014 STMicroelectronics

13 | *

14 | * Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

15 | * You may not use this file except in compliance with the License.

16 | * You may obtain a copy of the License at:

17 | *

18 | * http://www.st.com/software_license_agreement_liberty_v2

19 | *

20 | * Unless required by applicable law or agreed to in writing, software

21 | * distributed under the License is distributed on an "AS IS" BASIS,

22 | * WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

23 | * See the License for the specific language governing permissions and

24 | * limitations under the License.

25 | *

26 | ******************************************************************************

27 | */

28 |

29 | /* Define to prevent recursive inclusion -------------------------------------*/

30 | #ifndef __STM32F0XX_DBGMCU_H

31 | #define __STM32F0XX_DBGMCU_H

32 |

33 | #ifdef __cplusplus

34 | extern "C" {

35 | #endif

36 |

37 | /* Includes ------------------------------------------------------------------*/

38 | #include "stm32f0xx.h"

39 |

40 | /** @addtogroup STM32F0xx_StdPeriph_Driver

41 | * @{

42 | */

43 |

44 | /** @addtogroup DBGMCU

45 | * @{

46 | */

47 | /* Exported types ------------------------------------------------------------*/

48 | /* Exported constants --------------------------------------------------------*/

49 |

50 |

51 | /** @defgroup DBGMCU_Exported_Constants

52 | * @{

53 | */

54 |

55 | #define DBGMCU_STOP DBGMCU_CR_DBG_STOP

56 | #define DBGMCU_STANDBY DBGMCU_CR_DBG_STANDBY

57 | #define IS_DBGMCU_PERIPH(PERIPH) ((((PERIPH) & 0xFFFFFFF9) == 0x00) && ((PERIPH) != 0x00))

58 |

59 | #define DBGMCU_TIM2_STOP DBGMCU_APB1_FZ_DBG_TIM2_STOP /*!< Not applicable for STM32F030 devices */

60 | #define DBGMCU_TIM3_STOP DBGMCU_APB1_FZ_DBG_TIM3_STOP

61 | #define DBGMCU_TIM6_STOP DBGMCU_APB1_FZ_DBG_TIM6_STOP

62 | #define DBGMCU_TIM7_STOP DBGMCU_APB1_FZ_DBG_TIM7_STOP /*!< Only applicable for STM32F072 devices */

63 | #define DBGMCU_TIM14_STOP DBGMCU_APB1_FZ_DBG_TIM14_STOP

64 | #define DBGMCU_RTC_STOP DBGMCU_APB1_FZ_DBG_RTC_STOP

65 | #define DBGMCU_WWDG_STOP DBGMCU_APB1_FZ_DBG_WWDG_STOP

66 | #define DBGMCU_IWDG_STOP DBGMCU_APB1_FZ_DBG_IWDG_STOP

67 | #define DBGMCU_I2C1_SMBUS_TIMEOUT DBGMCU_APB1_FZ_DBG_I2C1_SMBUS_TIMEOUT

68 | #define DBGMCU_CAN1_STOP DBGMCU_APB1_FZ_DBG_CAN1_STOP /*!< Only applicable for STM32F042 and STM32F072 devices */

69 | #define IS_DBGMCU_APB1PERIPH(PERIPH) ((((PERIPH) & 0xFDDFE2CC) == 0x00) && ((PERIPH) != 0x00))

70 |

71 | #define DBGMCU_TIM1_STOP DBGMCU_APB2_FZ_DBG_TIM1_STOP

72 | #define DBGMCU_TIM15_STOP DBGMCU_APB2_FZ_DBG_TIM15_STOP

73 | #define DBGMCU_TIM16_STOP DBGMCU_APB2_FZ_DBG_TIM16_STOP

74 | #define DBGMCU_TIM17_STOP DBGMCU_APB2_FZ_DBG_TIM17_STOP

75 | #define IS_DBGMCU_APB2PERIPH(PERIPH) ((((PERIPH) & 0xFFF8F7FF) == 0x00) && ((PERIPH) != 0x00))

76 |

77 | /**

78 | * @}

79 | */

80 |

81 | /* Exported macro ------------------------------------------------------------*/

82 | /* Exported functions ------------------------------------------------------- */

83 |

84 | /* Device and Revision ID management functions ********************************/

85 | uint32_t DBGMCU_GetREVID(void);

86 | uint32_t DBGMCU_GetDEVID(void);

87 |