├── .gitignore

├── LICENSE

├── README.md

├── single-cycle-cpu.srcs

├── constrs_1

│ └── new

│ │ └── constraints.xdc

├── sim_1

│ └── new

│ │ └── testbench.v

└── sources_1

│ ├── ip

│ ├── data_memory_ip

│ │ ├── data_memory_ip.dcp

│ │ ├── data_memory_ip.mif

│ │ ├── data_memory_ip.veo

│ │ ├── data_memory_ip.vho

│ │ ├── data_memory_ip.xci

│ │ ├── data_memory_ip.xml

│ │ ├── data_memory_ip_ooc.xdc

│ │ ├── data_memory_ip_sim_netlist.v

│ │ ├── data_memory_ip_sim_netlist.vhdl

│ │ ├── data_memory_ip_stub.v

│ │ ├── data_memory_ip_stub.vhdl

│ │ ├── doc

│ │ │ └── dist_mem_gen_v8_0_changelog.txt

│ │ ├── hdl

│ │ │ └── dist_mem_gen_v8_0_vhsyn_rfs.vhd

│ │ ├── sim

│ │ │ └── data_memory_ip.v

│ │ ├── simulation

│ │ │ └── dist_mem_gen_v8_0.v

│ │ └── synth

│ │ │ └── data_memory_ip.vhd

│ └── instruction_memory_ip

│ │ ├── doc

│ │ └── dist_mem_gen_v8_0_changelog.txt

│ │ ├── hdl

│ │ └── dist_mem_gen_v8_0_vhsyn_rfs.vhd

│ │ ├── instruction_memory_ip.dcp

│ │ ├── instruction_memory_ip.mif

│ │ ├── instruction_memory_ip.veo

│ │ ├── instruction_memory_ip.vho

│ │ ├── instruction_memory_ip.xci

│ │ ├── instruction_memory_ip.xml

│ │ ├── instruction_memory_ip_ooc.xdc

│ │ ├── instruction_memory_ip_sim_netlist.v

│ │ ├── instruction_memory_ip_sim_netlist.vhdl

│ │ ├── instruction_memory_ip_stub.v

│ │ ├── instruction_memory_ip_stub.vhdl

│ │ ├── sim

│ │ └── instruction_memory_ip.v

│ │ ├── simulation

│ │ └── dist_mem_gen_v8_0.v

│ │ └── synth

│ │ └── instruction_memory_ip.vhd

│ └── new

│ ├── alu.v

│ ├── control_unit.v

│ ├── data_memory.v

│ ├── extend.v

│ ├── instruction_head.v

│ ├── instruction_memory.v

│ ├── mux.v

│ ├── npc.v

│ ├── pc.v

│ ├── register_file.v

│ └── top.v

├── single-cycle-cpu.xpr

└── tests

├── data_memory.txt

├── data_memory_tests.coe

├── instruction_tests.coe

├── instructions.txt

├── register.txt

└── tests.asm

/.gitignore:

--------------------------------------------------------------------------------

1 | single-cycle-cpu.cache

2 | single-cycle-cpu.hw

3 | single-cycle-cpu.ip_user_files

4 | single-cycle-cpu.sim

5 | single-cycle-cpu.runs

6 |

7 | # intermediate build files

8 | *.bgn

9 | *.bit

10 | *.bld

11 | *.cmd_log

12 | *.drc

13 | *.ll

14 | *.lso

15 | *.msd

16 | *.msk

17 | *.ncd

18 | *.ngc

19 | *.ngd

20 | *.ngr

21 | *.pad

22 | *.par

23 | *.pcf

24 | *.prj

25 | *.ptwx

26 | *.rbb

27 | *.rbd

28 | *.stx

29 | *.syr

30 | *.twr

31 | *.twx

32 | *.unroutes

33 | *.ut

34 | *.xpi

35 | *.xst

36 | *_bitgen.xwbt

37 | *_envsettings.html

38 | *_map.map

39 | *_map.mrp

40 | *_map.ngm

41 | *_map.xrpt

42 | *_ngdbuild.xrpt

43 | *_pad.csv

44 | *_pad.txt

45 | *_par.xrpt

46 | *_summary.html

47 | *_summary.xml

48 | *_usage.xml

49 | *_xst.xrpt

50 |

51 | # iMPACT generated files

52 | _impactbatch.log

53 | impact.xsl

54 | impact_impact.xwbt

55 | ise_impact.cmd

56 | webtalk_impact.xml

57 |

58 | # Core Generator generated files

59 | xaw2verilog.log

60 |

61 | # project-wide generated files

62 | *.gise

63 | par_usage_statistics.html

64 | usage_statistics_webtalk.html

65 | webtalk.log

66 | webtalk_pn.xml

67 |

68 | # generated folders

69 | iseconfig/

70 | xlnx_auto_0_xdb/

71 | xst/

72 | _ngo/

73 | _xmsgs/

74 |

--------------------------------------------------------------------------------

/LICENSE:

--------------------------------------------------------------------------------

1 | MIT License

2 |

3 | Copyright (c) 2019 Spencer Woo

4 |

5 | Permission is hereby granted, free of charge, to any person obtaining a copy

6 | of this software and associated documentation files (the "Software"), to deal

7 | in the Software without restriction, including without limitation the rights

8 | to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

9 | copies of the Software, and to permit persons to whom the Software is

10 | furnished to do so, subject to the following conditions:

11 |

12 | The above copyright notice and this permission notice shall be included in all

13 | copies or substantial portions of the Software.

14 |

15 | THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

16 | IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

17 | FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

18 | AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

19 | LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

20 | OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE

21 | SOFTWARE.

22 |

--------------------------------------------------------------------------------

/README.md:

--------------------------------------------------------------------------------

1 |  2 |

3 | # 🎲 Single Cycle CPU

4 |

5 | > 辛苦三星期,造台计算机!

6 |

7 | BIT Personal project: a simple single cycle CPU. Initial steps of designing [the ZanPU](https://github.com/zan-pu).

8 |

9 | ## Source Code

10 |

11 | All source codes are available at [single-cycle-cpu.srcs](./single-cycle-cpu.srcs).

12 |

13 | - [Design Sources](./single-cycle-cpu.srcs/sources_1/new)

14 | - [Simulation Sources](./single-cycle-cpu.srcs/sim_1/new)

15 |

16 | Instruction, data memory and register files are initialized at [tests](./tests).

17 |

18 | ## Modules / Data Path

19 |

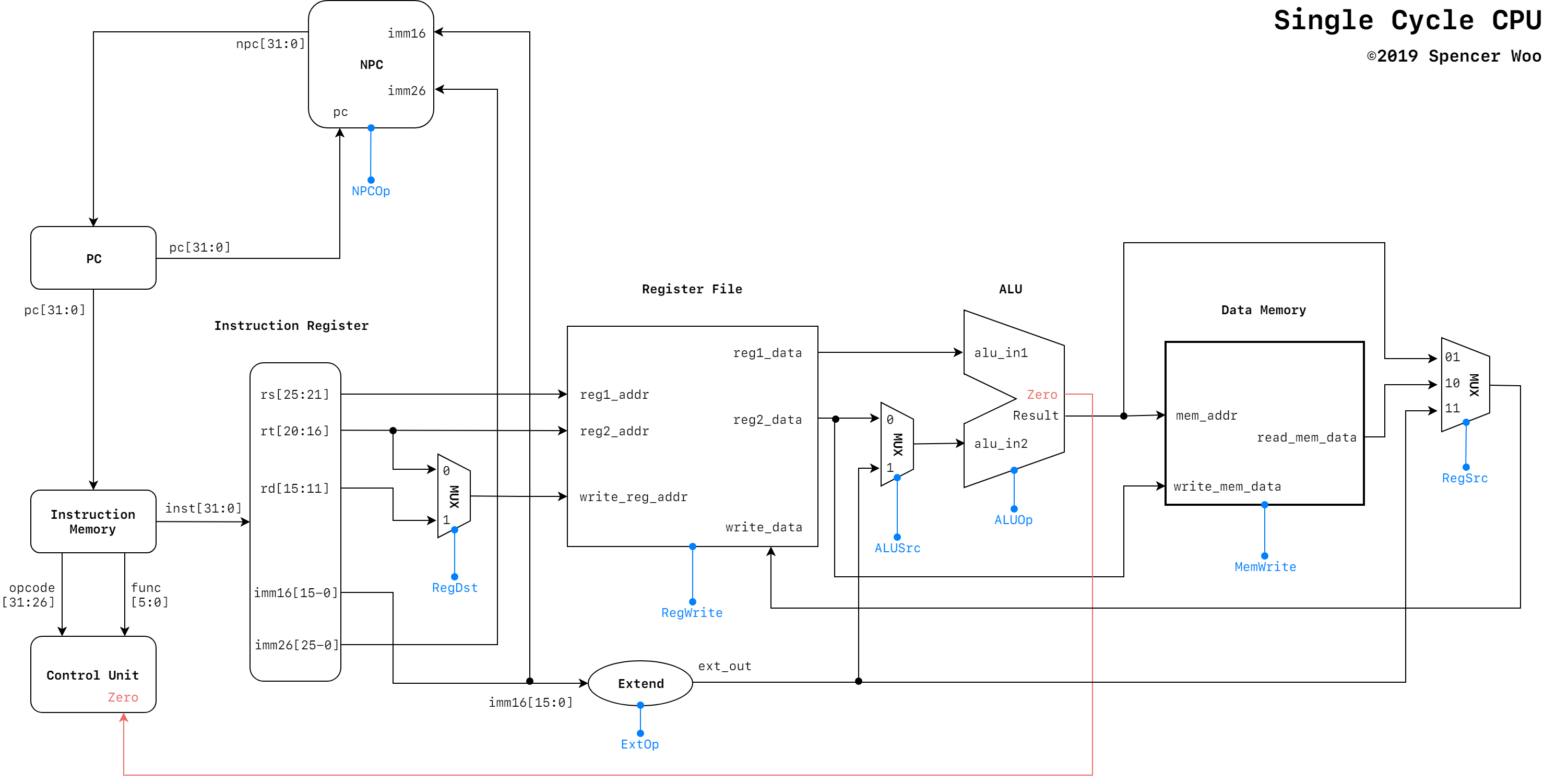

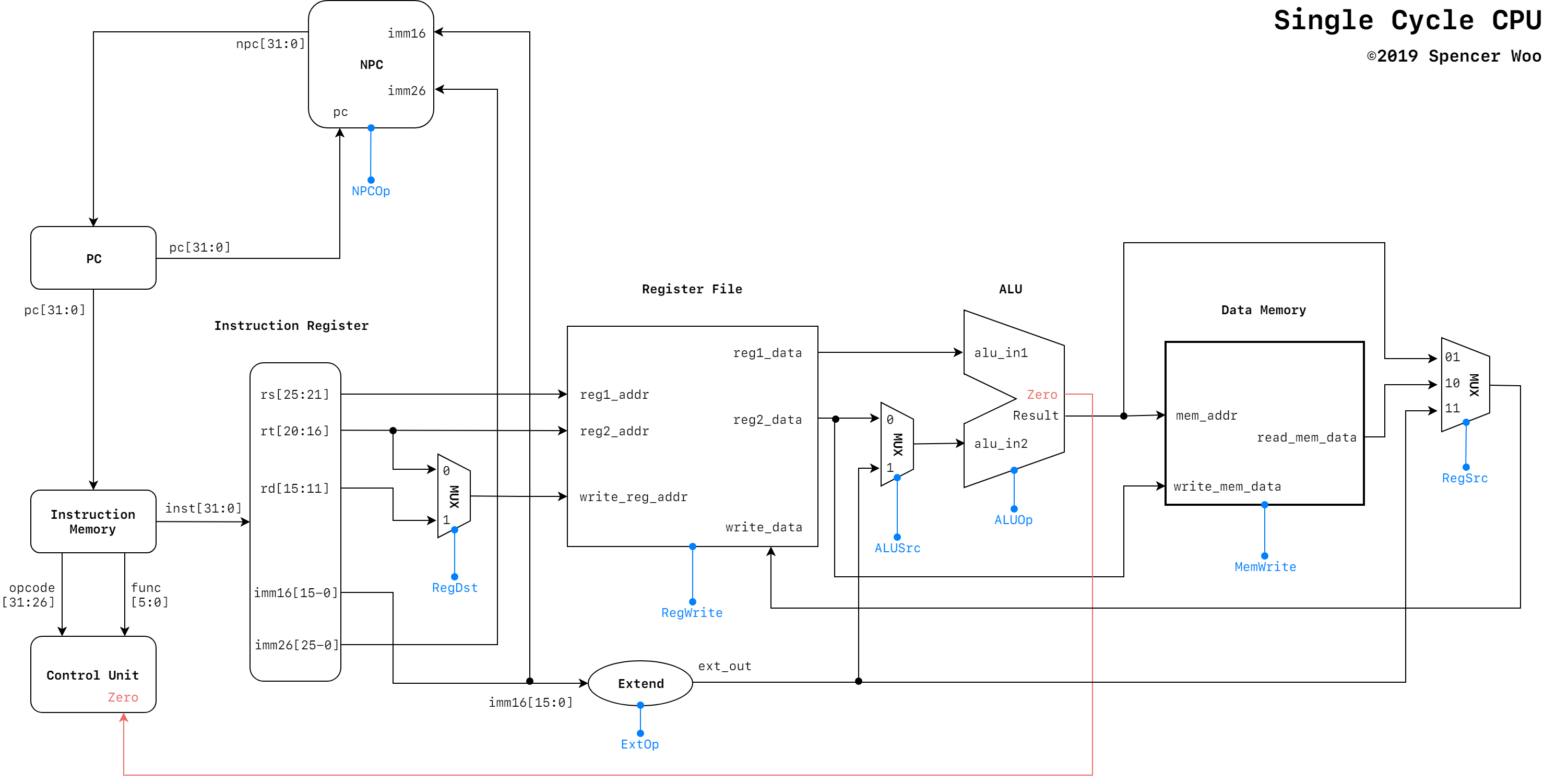

20 |

21 |

22 | Detailed documentation at: [🚡 Build Your PC - 个人项目 - 单周期 CPU](https://zanpu.spencerwoo.com/2_SingleCycle/2-1_Basic.html).

23 |

24 | ## Tests

25 |

26 | Complete simulated tests for the following instructions.

27 |

28 | ### LUI

29 |

30 | Test instructions:

31 |

32 | ```MIPS

33 | lui $1, 1

34 | lui $2, 2

35 | ```

36 |

37 | ```

38 |

39 | 0x3c010001

40 | 0x3c020002

41 | ```

42 |

43 | Expected:

44 |

45 | ```

46 |

47 | gpr[2] 00020000

48 | gpr[1] 00010000

49 | gpr[0] 00000000

50 | ```

51 |

52 | Results:

53 |

54 |

55 |

56 | ### ADDIU

57 |

58 | Test instructions:

59 |

60 | ```MIPS

61 | lui $1, 1

62 | addiu $2, $1, 1024

63 | ```

64 |

65 | ```

66 |

67 | 0x3c010001

68 | 0x24220400

69 | ```

70 |

71 | Expected:

72 |

73 | ```

74 |

75 | gpr[2] 00010400

76 | gpr[1] 00010000

77 | gpr[0] 00000000

78 | ```

79 |

80 | Results:

81 |

82 |

83 |

84 | ### ADD、SUBU

85 |

86 | Test instructions:

87 |

88 | ```MIPS

89 | lui $1, 1

90 | lui $2, 2

91 | add $3, $1, $2

92 | subu $4, $2, $1

93 | ```

94 |

95 | ```

96 |

97 | 0x3c010001

98 | 0x3c020002

99 | 0x00221820

100 | 0x00412023

101 | ```

102 |

103 | Expected:

104 |

105 | ```

106 |

107 | gpr[4] 00010000

108 | gpr[3] 00030000

109 | gpr[2] 00020000

110 | gpr[1] 00010000

111 | gpr[0] 00000000

112 | ```

113 |

114 | Results:

115 |

116 |

117 |

118 | ### LW

119 |

120 | Test instructions:

121 |

122 | ```MIPS

123 | lw $1, 0

124 | lw $2, 4

125 | ```

126 |

127 | ```

128 |

129 | 0x8c010000

130 | 0x8c020004

131 | ```

132 |

133 | Initialize data memory with:

134 |

135 | ```

136 |

137 | 0x00000001

138 | 0x0000000f

139 | ```

140 |

141 | Expected:

142 |

143 | ```

144 |

145 | gpr[2] 0000000f

146 | gpr[1] 00000001

147 | gpr[0] 00000000

148 | ```

149 |

150 | Results:

151 |

152 |

153 |

154 | ### SW

155 |

156 | Test instructions:

157 |

158 | ```MIPS

159 | addiu $1, $0, 0x0009

160 | sw $1, 8

161 | ```

162 |

163 | ```

164 |

165 | 0x24010009

166 | 0xac010008

167 | ```

168 |

169 | Expected:

170 |

171 | ```

172 |

173 | dm[2] 00000009

174 | dm[1] 0000000f

175 | dm[0] 00000001

176 | ```

177 |

178 | Results:

179 |

180 |

181 |

182 | ### BEQ

183 |

184 | Test instructions:

185 |

186 | ```MIPS

187 | addiu $11, $0, 0x0009

188 | addiu $10, $0, 0x0009

189 | beq $11, $10, target

190 | lui $1, 1

191 | lui $2, 2

192 | target: lui $3, 3

193 | lui $4, 4

194 | ```

195 |

196 | ```

197 |

198 | 0x240b0009

199 | 0x240a0009

200 | 0x116a0002

201 | 0x3c010001

202 | 0x3c020002

203 | 0x3c030003

204 | 0x3c040004

205 | ```

206 |

207 | Expected:

208 |

209 | ```

210 |

211 | gpr[11] 00000009

212 | gpr[10] 00000009

213 | ...

214 | gpr[4] 00040000

215 | gpr[3] 00030000

216 | gpr[2] 00000000

217 | gpr[1] 00000000

218 | gpr[0] 00000000

219 | ```

220 |

221 | Results:

222 |

223 |

224 |

225 | ### J

226 |

227 | Test instructions:

228 |

229 | ```MIPS

230 | j target

231 | lui $1, 1

232 | lui $2, 2

233 | target: lui $3, 3

234 | lui $4, 4

235 | ```

236 |

237 | ```

238 |

239 | 0x08100003

240 | 0x3c010001

241 | 0x3c020002

242 | 0x3c030003

243 | 0x3c040004

244 | ```

245 |

246 | Expected:

247 |

248 | ```

249 |

250 | gpr[4] 00040000

251 | gpr[3] 00030000

252 | gpr[2] 00000000

253 | gpr[1] 00000000

254 | gpr[0] 00000000

255 | ```

256 |

257 | Results:

258 |

259 |

260 |

261 | ---

262 |

263 | 🎲 **Single Cycle CPU** ©Spencer Woo. Released under the [MIT License](./LICENSE).

264 |

265 | Authored and maintained by Spencer Woo.

266 |

267 | [@Portfolio](https://spencerwoo.com) · [@GitHub](https://github.com/spencerwooo) · [@BIT](http://www.bit.edu.cn/)

268 |

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/constrs_1/new/constraints.xdc:

--------------------------------------------------------------------------------

1 | set_property IOSTANDARD LVCMOS33 [get_ports {debug_reg_single[7]}]

2 | set_property IOSTANDARD LVCMOS33 [get_ports {debug_reg_single[6]}]

3 | set_property IOSTANDARD LVCMOS33 [get_ports {debug_reg_single[5]}]

4 | set_property IOSTANDARD LVCMOS33 [get_ports {debug_reg_single[4]}]

5 | set_property IOSTANDARD LVCMOS33 [get_ports {debug_reg_single[3]}]

6 | set_property IOSTANDARD LVCMOS33 [get_ports {debug_reg_single[2]}]

7 | set_property IOSTANDARD LVCMOS33 [get_ports {debug_reg_single[1]}]

8 | set_property IOSTANDARD LVCMOS33 [get_ports {debug_reg_single[0]}]

9 | set_property IOSTANDARD LVCMOS33 [get_ports clk]

10 | set_property IOSTANDARD LVCMOS33 [get_ports rst]

11 | set_property PACKAGE_PIN T5 [get_ports clk]

12 | set_property PACKAGE_PIN P15 [get_ports rst]

13 | set_property PACKAGE_PIN K2 [get_ports {debug_reg_single[0]}]

14 | set_property PACKAGE_PIN J2 [get_ports {debug_reg_single[1]}]

15 | set_property PACKAGE_PIN J3 [get_ports {debug_reg_single[2]}]

16 | set_property PACKAGE_PIN H4 [get_ports {debug_reg_single[3]}]

17 | set_property PACKAGE_PIN J4 [get_ports {debug_reg_single[4]}]

18 | set_property PACKAGE_PIN G3 [get_ports {debug_reg_single[5]}]

19 | set_property PACKAGE_PIN G4 [get_ports {debug_reg_single[6]}]

20 | set_property PACKAGE_PIN F6 [get_ports {debug_reg_single[7]}]

21 |

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/sim_1/new/testbench.v:

--------------------------------------------------------------------------------

1 | `timescale 1ns / 1ps

2 |

3 | /*

4 | * Testbench

5 | */

6 |

7 | module testbench();

8 | reg clk;

9 | reg rst;

10 | top ZAN_TOP(clk, rst);

11 |

12 | initial begin

13 | // // Load instructions

14 | // $readmemh("../../../tests/instructions.txt", ZAN_TOP.ZAN_INSTR_MEM.im);

15 | // // Load register initial values

16 | // $readmemh("../../../tests/register.txt", ZAN_TOP.ZAN_REG_FILE.gpr);

17 | // // Load memory data initial values

18 | // $readmemh("../../../tests/data_memory.txt", ZAN_TOP.ZAN_DATA_MEM.dm);

19 |

20 | rst = 1;

21 | clk = 0;

22 |

23 | #30 rst = 0;

24 | // #80 $display("$10 value: %h", ZAN_TOP.ZAN_REG_FILE.gpr[10]);

25 | #500 $stop;

26 | end

27 |

28 | always

29 | #20 clk = ~clk;

30 | endmodule

31 |

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/sources_1/ip/data_memory_ip/data_memory_ip.dcp:

--------------------------------------------------------------------------------

https://raw.githubusercontent.com/spencerwooo/single-cycle-processor/63187f355459f5d1482f4a53c7116b2c8a4080d1/single-cycle-cpu.srcs/sources_1/ip/data_memory_ip/data_memory_ip.dcp

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/sources_1/ip/data_memory_ip/data_memory_ip.mif:

--------------------------------------------------------------------------------

1 | 00000000000000000000000000000000

2 | 00000000000000000000000000000000

3 | 00000000000000000000000000000000

4 |

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/sources_1/ip/data_memory_ip/data_memory_ip.veo:

--------------------------------------------------------------------------------

1 | // (c) Copyright 1995-2019 Xilinx, Inc. All rights reserved.

2 | //

3 | // This file contains confidential and proprietary information

4 | // of Xilinx, Inc. and is protected under U.S. and

5 | // international copyright and other intellectual property

6 | // laws.

7 | //

8 | // DISCLAIMER

9 | // This disclaimer is not a license and does not grant any

10 | // rights to the materials distributed herewith. Except as

11 | // otherwise provided in a valid license issued to you by

12 | // Xilinx, and to the maximum extent permitted by applicable

13 | // law: (1) THESE MATERIALS ARE MADE AVAILABLE "AS IS" AND

14 | // WITH ALL FAULTS, AND XILINX HEREBY DISCLAIMS ALL WARRANTIES

15 | // AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING

16 | // BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-

17 | // INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and

18 | // (2) Xilinx shall not be liable (whether in contract or tort,

19 | // including negligence, or under any other theory of

20 | // liability) for any loss or damage of any kind or nature

21 | // related to, arising under or in connection with these

22 | // materials, including for any direct, or any indirect,

23 | // special, incidental, or consequential loss or damage

24 | // (including loss of data, profits, goodwill, or any type of

25 | // loss or damage suffered as a result of any action brought

26 | // by a third party) even if such damage or loss was

27 | // reasonably foreseeable or Xilinx had been advised of the

28 | // possibility of the same.

29 | //

30 | // CRITICAL APPLICATIONS

31 | // Xilinx products are not designed or intended to be fail-

32 | // safe, or for use in any application requiring fail-safe

33 | // performance, such as life-support or safety devices or

34 | // systems, Class III medical devices, nuclear facilities,

35 | // applications related to the deployment of airbags, or any

36 | // other applications that could lead to death, personal

37 | // injury, or severe property or environmental damage

38 | // (individually and collectively, "Critical

39 | // Applications"). Customer assumes the sole risk and

40 | // liability of any use of Xilinx products in Critical

41 | // Applications, subject only to applicable laws and

42 | // regulations governing limitations on product liability.

43 | //

44 | // THIS COPYRIGHT NOTICE AND DISCLAIMER MUST BE RETAINED AS

45 | // PART OF THIS FILE AT ALL TIMES.

46 | //

47 | // DO NOT MODIFY THIS FILE.

48 |

49 | // IP VLNV: xilinx.com:ip:dist_mem_gen:8.0

50 | // IP Revision: 11

51 |

52 | // The following must be inserted into your Verilog file for this

53 | // core to be instantiated. Change the instance name and port connections

54 | // (in parentheses) to your own signal names.

55 |

56 | //----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

57 | data_memory_ip your_instance_name (

58 | .a(a), // input wire [9 : 0] a

59 | .d(d), // input wire [31 : 0] d

60 | .clk(clk), // input wire clk

61 | .we(we), // input wire we

62 | .spo(spo) // output wire [31 : 0] spo

63 | );

64 | // INST_TAG_END ------ End INSTANTIATION Template ---------

65 |

66 | // You must compile the wrapper file data_memory_ip.v when simulating

67 | // the core, data_memory_ip. When compiling the wrapper file, be sure to

68 | // reference the Verilog simulation library.

69 |

70 |

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/sources_1/ip/data_memory_ip/data_memory_ip.vho:

--------------------------------------------------------------------------------

1 | -- (c) Copyright 1995-2019 Xilinx, Inc. All rights reserved.

2 | --

3 | -- This file contains confidential and proprietary information

4 | -- of Xilinx, Inc. and is protected under U.S. and

5 | -- international copyright and other intellectual property

6 | -- laws.

7 | --

8 | -- DISCLAIMER

9 | -- This disclaimer is not a license and does not grant any

10 | -- rights to the materials distributed herewith. Except as

11 | -- otherwise provided in a valid license issued to you by

12 | -- Xilinx, and to the maximum extent permitted by applicable

13 | -- law: (1) THESE MATERIALS ARE MADE AVAILABLE "AS IS" AND

14 | -- WITH ALL FAULTS, AND XILINX HEREBY DISCLAIMS ALL WARRANTIES

15 | -- AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING

16 | -- BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-

17 | -- INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and

18 | -- (2) Xilinx shall not be liable (whether in contract or tort,

19 | -- including negligence, or under any other theory of

20 | -- liability) for any loss or damage of any kind or nature

21 | -- related to, arising under or in connection with these

22 | -- materials, including for any direct, or any indirect,

23 | -- special, incidental, or consequential loss or damage

24 | -- (including loss of data, profits, goodwill, or any type of

25 | -- loss or damage suffered as a result of any action brought

26 | -- by a third party) even if such damage or loss was

27 | -- reasonably foreseeable or Xilinx had been advised of the

28 | -- possibility of the same.

29 | --

30 | -- CRITICAL APPLICATIONS

31 | -- Xilinx products are not designed or intended to be fail-

32 | -- safe, or for use in any application requiring fail-safe

33 | -- performance, such as life-support or safety devices or

34 | -- systems, Class III medical devices, nuclear facilities,

35 | -- applications related to the deployment of airbags, or any

36 | -- other applications that could lead to death, personal

37 | -- injury, or severe property or environmental damage

38 | -- (individually and collectively, "Critical

39 | -- Applications"). Customer assumes the sole risk and

40 | -- liability of any use of Xilinx products in Critical

41 | -- Applications, subject only to applicable laws and

42 | -- regulations governing limitations on product liability.

43 | --

44 | -- THIS COPYRIGHT NOTICE AND DISCLAIMER MUST BE RETAINED AS

45 | -- PART OF THIS FILE AT ALL TIMES.

46 | --

47 | -- DO NOT MODIFY THIS FILE.

48 |

49 | -- IP VLNV: xilinx.com:ip:dist_mem_gen:8.0

50 | -- IP Revision: 11

51 |

52 | -- The following code must appear in the VHDL architecture header.

53 |

54 | ------------- Begin Cut here for COMPONENT Declaration ------ COMP_TAG

55 | COMPONENT data_memory_ip

56 | PORT (

57 | a : IN STD_LOGIC_VECTOR(9 DOWNTO 0);

58 | d : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

59 | clk : IN STD_LOGIC;

60 | we : IN STD_LOGIC;

61 | spo : OUT STD_LOGIC_VECTOR(31 DOWNTO 0)

62 | );

63 | END COMPONENT;

64 | -- COMP_TAG_END ------ End COMPONENT Declaration ------------

65 |

66 | -- The following code must appear in the VHDL architecture

67 | -- body. Substitute your own instance name and net names.

68 |

69 | ------------- Begin Cut here for INSTANTIATION Template ----- INST_TAG

70 | your_instance_name : data_memory_ip

71 | PORT MAP (

72 | a => a,

73 | d => d,

74 | clk => clk,

75 | we => we,

76 | spo => spo

77 | );

78 | -- INST_TAG_END ------ End INSTANTIATION Template ---------

79 |

80 | -- You must compile the wrapper file data_memory_ip.vhd when simulating

81 | -- the core, data_memory_ip. When compiling the wrapper file, be sure to

82 | -- reference the VHDL simulation library.

83 |

84 |

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/sources_1/ip/data_memory_ip/data_memory_ip.xci:

--------------------------------------------------------------------------------

1 |

2 |

3 | xilinx.com

4 | xci

5 | unknown

6 | 1.0

7 |

8 |

9 | data_memory_ip

10 |

11 |

12 | 10

13 | 0

14 | 1024

15 | ./

16 | artix7

17 | 1

18 | 1

19 | 0

20 | 0

21 | 0

22 | 0

23 | 0

24 | 0

25 | 0

26 | 0

27 | 0

28 | 0

29 | 0

30 | 0

31 | 1

32 | 1

33 | data_memory_ip.mif

34 | 1

35 | 1

36 | 0

37 | 0

38 | 0

39 | 1

40 | 0

41 | 0

42 | 1

43 | 32

44 | data_memory_ip

45 | 0

46 | ce_overrides_sync_controls

47 | ../../../../tests/data_memory_tests.coe

48 | false

49 | false

50 | 32

51 | 0

52 | 16

53 | 1024

54 | non_registered

55 | false

56 | false

57 | non_registered

58 | single_port_ram

59 | non_registered

60 | false

61 | false

62 | false

63 | false

64 | non_registered

65 | false

66 | false

67 | false

68 | false

69 | false

70 | artix7

71 |

72 | xc7a35t

73 | csg324

74 | VERILOG

75 |

76 | MIXED

77 | -1

78 |

79 | TRUE

80 | TRUE

81 | IP_Flow

82 | 11

83 | TRUE

84 | .

85 |

86 | .

87 | 2017.2

88 | OUT_OF_CONTEXT

89 |

90 |

91 |

92 |

93 |

94 |

95 |

96 |

97 |

98 |

99 |

100 |

101 |

102 |

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/sources_1/ip/data_memory_ip/data_memory_ip_ooc.xdc:

--------------------------------------------------------------------------------

1 | ################################################################################

2 | #

3 | # (c) Copyright 2009 - 2014 Xilinx, Inc. All rights reserved.

4 | #

5 | # This file contains confidential and proprietary information

6 | # of Xilinx, Inc. and is protected under U.S. and

7 | # international copyright and other intellectual property

8 | # laws.

9 | #

10 | # DISCLAIMER

11 | # This disclaimer is not a license and does not grant any

12 | # rights to the materials distributed herewith. Except as

13 | # otherwise provided in a valid license issued to you by

14 | # Xilinx, and to the maximum extent permitted by applicable

15 | # law: (1) THESE MATERIALS ARE MADE AVAILABLE "AS IS" AND

16 | # WITH ALL FAULTS, AND XILINX HEREBY DISCLAIMS ALL WARRANTIES

17 | # AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING

18 | # BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-

19 | # INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and

20 | # (2) Xilinx shall not be liable (whether in contract or tort,

21 | # including negligence, or under any other theory of

22 | # liability) for any loss or damage of any kind or nature

23 | # related to, arising under or in connection with these

24 | # materials, including for any direct, or any indirect,

25 | # special, incidental, or consequential loss or damage

26 | # (including loss of data, profits, goodwill, or any type of

27 | # loss or damage suffered as a result of any action brought

28 | # by a third party) even if such damage or loss was

29 | # reasonably foreseeable or Xilinx had been advised of the

30 | # possibility of the same.

31 | #

32 | # CRITICAL APPLICATIONS

33 | # Xilinx products are not designed or intended to be fail-

34 | # safe, or for use in any application requiring fail-safe

35 | # performance, such as life-support or safety devices or

36 | # systems, Class III medical devices, nuclear facilities,

37 | # applications related to the deployment of airbags, or any

38 | # other applications that could lead to death, personal

39 | # injury, or severe property or environmental damage

40 | # (individually and collectively, "Critical

41 | # Applications"). Customer assumes the sole risk and

42 | # liability of any use of Xilinx products in Critical

43 | # Applications, subject only to applicable laws and

44 | # regulations governing limitations on product liability.

45 | #

46 | # THIS COPYRIGHT NOTICE AND DISCLAIMER MUST BE RETAINED AS

47 | # PART OF THIS FILE AT ALL TIMES.

48 | #

49 | ################################################################################

50 |

51 | # Tx Core Period Constraint. This constraint can be modified, and is

52 | # valid as long as it is met after place and route.

53 | create_clock -name "TS_CLK" -period 20.0 [ get_ports clk ]

54 |

55 |

56 | ################################################################################

57 |

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/sources_1/ip/data_memory_ip/data_memory_ip_stub.v:

--------------------------------------------------------------------------------

1 | // Copyright 1986-2017 Xilinx, Inc. All Rights Reserved.

2 | // --------------------------------------------------------------------------------

3 | // Tool Version: Vivado v.2017.2 (win64) Build 1909853 Thu Jun 15 18:39:09 MDT 2017

4 | // Date : Sun Sep 15 15:45:21 2019

5 | // Host : DESKTOP-IT0A8CI running 64-bit major release (build 9200)

6 | // Command : write_verilog -force -mode synth_stub -rename_top data_memory_ip -prefix

7 | // data_memory_ip_ data_memory_ip_stub.v

8 | // Design : data_memory_ip

9 | // Purpose : Stub declaration of top-level module interface

10 | // Device : xc7a35tcsg324-1

11 | // --------------------------------------------------------------------------------

12 |

13 | // This empty module with port declaration file causes synthesis tools to infer a black box for IP.

14 | // The synthesis directives are for Synopsys Synplify support to prevent IO buffer insertion.

15 | // Please paste the declaration into a Verilog source file or add the file as an additional source.

16 | (* x_core_info = "dist_mem_gen_v8_0_11,Vivado 2017.2" *)

17 | module data_memory_ip(a, d, clk, we, spo)

18 | /* synthesis syn_black_box black_box_pad_pin="a[9:0],d[31:0],clk,we,spo[31:0]" */;

19 | input [9:0]a;

20 | input [31:0]d;

21 | input clk;

22 | input we;

23 | output [31:0]spo;

24 | endmodule

25 |

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/sources_1/ip/data_memory_ip/data_memory_ip_stub.vhdl:

--------------------------------------------------------------------------------

1 | -- Copyright 1986-2017 Xilinx, Inc. All Rights Reserved.

2 | -- --------------------------------------------------------------------------------

3 | -- Tool Version: Vivado v.2017.2 (win64) Build 1909853 Thu Jun 15 18:39:09 MDT 2017

4 | -- Date : Sun Sep 15 15:45:21 2019

5 | -- Host : DESKTOP-IT0A8CI running 64-bit major release (build 9200)

6 | -- Command : write_vhdl -force -mode synth_stub -rename_top data_memory_ip -prefix

7 | -- data_memory_ip_ data_memory_ip_stub.vhdl

8 | -- Design : data_memory_ip

9 | -- Purpose : Stub declaration of top-level module interface

10 | -- Device : xc7a35tcsg324-1

11 | -- --------------------------------------------------------------------------------

12 | library IEEE;

13 | use IEEE.STD_LOGIC_1164.ALL;

14 |

15 | entity data_memory_ip is

16 | Port (

17 | a : in STD_LOGIC_VECTOR ( 9 downto 0 );

18 | d : in STD_LOGIC_VECTOR ( 31 downto 0 );

19 | clk : in STD_LOGIC;

20 | we : in STD_LOGIC;

21 | spo : out STD_LOGIC_VECTOR ( 31 downto 0 )

22 | );

23 |

24 | end data_memory_ip;

25 |

26 | architecture stub of data_memory_ip is

27 | attribute syn_black_box : boolean;

28 | attribute black_box_pad_pin : string;

29 | attribute syn_black_box of stub : architecture is true;

30 | attribute black_box_pad_pin of stub : architecture is "a[9:0],d[31:0],clk,we,spo[31:0]";

31 | attribute x_core_info : string;

32 | attribute x_core_info of stub : architecture is "dist_mem_gen_v8_0_11,Vivado 2017.2";

33 | begin

34 | end;

35 |

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/sources_1/ip/data_memory_ip/doc/dist_mem_gen_v8_0_changelog.txt:

--------------------------------------------------------------------------------

1 | 2017.2:

2 | * Version 8.0 (Rev. 11)

3 | * No changes

4 |

5 | 2017.1:

6 | * Version 8.0 (Rev. 11)

7 | * No changes

8 |

9 | 2016.4:

10 | * Version 8.0 (Rev. 11)

11 | * No changes

12 |

13 | 2016.3:

14 | * Version 8.0 (Rev. 11)

15 | * General: Enable support for future devices

16 |

17 | 2016.2:

18 | * Version 8.0 (Rev. 10)

19 | * No changes

20 |

21 | 2016.1:

22 | * Version 8.0 (Rev. 10)

23 | * Delivering only verilog simulation model, Stopped delivery of vhdl simulation model.

24 |

25 | 2015.4.2:

26 | * Version 8.0 (Rev. 9)

27 | * No changes

28 |

29 | 2015.4.1:

30 | * Version 8.0 (Rev. 9)

31 | * No changes

32 |

33 | 2015.4:

34 | * Version 8.0 (Rev. 9)

35 | * No changes

36 |

37 | 2015.3:

38 | * Version 8.0 (Rev. 9)

39 | * Delivering only vhdl simulation model, Stopped delivery of verilog simulation model.

40 | * IP revision number added to HDL module, library, and include file names, to support designs with both locked and upgraded IP instances

41 |

42 | 2015.2.1:

43 | * Version 8.0 (Rev. 8)

44 | * No changes

45 |

46 | 2015.2:

47 | * Version 8.0 (Rev. 8)

48 | * No changes

49 |

50 | 2015.1:

51 | * Version 8.0 (Rev. 8)

52 | * Delivering unencrypted simulation files.

53 | * Supported devices and production status are now determined automatically, to simplify support for future devices

54 |

55 | 2014.4.1:

56 | * Version 8.0 (Rev. 7)

57 | * No changes

58 |

59 | 2014.4:

60 | * Version 8.0 (Rev. 7)

61 | * Encrypted source files are concatenated together to reduce the number of files and to reduce simulator compile time

62 | * Internal device family change, no functional changes

63 |

64 | 2014.3:

65 | * Version 8.0 (Rev. 6)

66 | * Reduced warnings in synthesis, no functional changes

67 |

68 | 2014.2:

69 | * Version 8.0 (Rev. 5)

70 | * Repackaged to improve internal automation, no functional changes.

71 |

72 | 2014.1:

73 | * Version 8.0 (Rev. 4)

74 | * Internal device family name change, no functional changes

75 |

76 | 2013.4:

77 | * Version 8.0 (Rev. 3)

78 | * Added support for Ultrascale devices

79 |

80 | 2013.3:

81 | * Version 8.0 (Rev. 2)

82 | * Enhanced support for IP Integrator

83 | * Reduced warnings in synthesis and simulation

84 | * Added support for Cadence IES and Synopsys VCS simulators

85 |

86 | 2013.2:

87 | * Version 8.0 (Rev. 1)

88 | * Repackaged to enable internal version management, no functional changes.

89 |

90 | 2013.1:

91 | * Version 8.0

92 | * Native Vivado Release

93 | * Unused port SPRA and its associated parameters removed.

94 |

95 | (c) Copyright 2002 - 2017 Xilinx, Inc. All rights reserved.

96 |

97 | This file contains confidential and proprietary information

98 | of Xilinx, Inc. and is protected under U.S. and

99 | international copyright and other intellectual property

100 | laws.

101 |

102 | DISCLAIMER

103 | This disclaimer is not a license and does not grant any

104 | rights to the materials distributed herewith. Except as

105 | otherwise provided in a valid license issued to you by

106 | Xilinx, and to the maximum extent permitted by applicable

107 | law: (1) THESE MATERIALS ARE MADE AVAILABLE "AS IS" AND

108 | WITH ALL FAULTS, AND XILINX HEREBY DISCLAIMS ALL WARRANTIES

109 | AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING

110 | BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-

111 | INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and

112 | (2) Xilinx shall not be liable (whether in contract or tort,

113 | including negligence, or under any other theory of

114 | liability) for any loss or damage of any kind or nature

115 | related to, arising under or in connection with these

116 | materials, including for any direct, or any indirect,

117 | special, incidental, or consequential loss or damage

118 | (including loss of data, profits, goodwill, or any type of

119 | loss or damage suffered as a result of any action brought

120 | by a third party) even if such damage or loss was

121 | reasonably foreseeable or Xilinx had been advised of the

122 | possibility of the same.

123 |

124 | CRITICAL APPLICATIONS

125 | Xilinx products are not designed or intended to be fail-

126 | safe, or for use in any application requiring fail-safe

127 | performance, such as life-support or safety devices or

128 | systems, Class III medical devices, nuclear facilities,

129 | applications related to the deployment of airbags, or any

130 | other applications that could lead to death, personal

131 | injury, or severe property or environmental damage

132 | (individually and collectively, "Critical

133 | Applications"). Customer assumes the sole risk and

134 | liability of any use of Xilinx products in Critical

135 | Applications, subject only to applicable laws and

136 | regulations governing limitations on product liability.

137 |

138 | THIS COPYRIGHT NOTICE AND DISCLAIMER MUST BE RETAINED AS

139 | PART OF THIS FILE AT ALL TIMES.

140 |

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/sources_1/ip/data_memory_ip/sim/data_memory_ip.v:

--------------------------------------------------------------------------------

1 | // (c) Copyright 1995-2019 Xilinx, Inc. All rights reserved.

2 | //

3 | // This file contains confidential and proprietary information

4 | // of Xilinx, Inc. and is protected under U.S. and

5 | // international copyright and other intellectual property

6 | // laws.

7 | //

8 | // DISCLAIMER

9 | // This disclaimer is not a license and does not grant any

10 | // rights to the materials distributed herewith. Except as

11 | // otherwise provided in a valid license issued to you by

12 | // Xilinx, and to the maximum extent permitted by applicable

13 | // law: (1) THESE MATERIALS ARE MADE AVAILABLE "AS IS" AND

14 | // WITH ALL FAULTS, AND XILINX HEREBY DISCLAIMS ALL WARRANTIES

15 | // AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING

16 | // BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-

17 | // INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and

18 | // (2) Xilinx shall not be liable (whether in contract or tort,

19 | // including negligence, or under any other theory of

20 | // liability) for any loss or damage of any kind or nature

21 | // related to, arising under or in connection with these

22 | // materials, including for any direct, or any indirect,

23 | // special, incidental, or consequential loss or damage

24 | // (including loss of data, profits, goodwill, or any type of

25 | // loss or damage suffered as a result of any action brought

26 | // by a third party) even if such damage or loss was

27 | // reasonably foreseeable or Xilinx had been advised of the

28 | // possibility of the same.

29 | //

30 | // CRITICAL APPLICATIONS

31 | // Xilinx products are not designed or intended to be fail-

32 | // safe, or for use in any application requiring fail-safe

33 | // performance, such as life-support or safety devices or

34 | // systems, Class III medical devices, nuclear facilities,

35 | // applications related to the deployment of airbags, or any

36 | // other applications that could lead to death, personal

37 | // injury, or severe property or environmental damage

38 | // (individually and collectively, "Critical

39 | // Applications"). Customer assumes the sole risk and

40 | // liability of any use of Xilinx products in Critical

41 | // Applications, subject only to applicable laws and

42 | // regulations governing limitations on product liability.

43 | //

44 | // THIS COPYRIGHT NOTICE AND DISCLAIMER MUST BE RETAINED AS

45 | // PART OF THIS FILE AT ALL TIMES.

46 | //

47 | // DO NOT MODIFY THIS FILE.

48 |

49 |

50 | // IP VLNV: xilinx.com:ip:dist_mem_gen:8.0

51 | // IP Revision: 11

52 |

53 | `timescale 1ns/1ps

54 |

55 | (* DowngradeIPIdentifiedWarnings = "yes" *)

56 | module data_memory_ip (

57 | a,

58 | d,

59 | clk,

60 | we,

61 | spo

62 | );

63 |

64 | input wire [9 : 0] a;

65 | input wire [31 : 0] d;

66 | input wire clk;

67 | input wire we;

68 | output wire [31 : 0] spo;

69 |

70 | dist_mem_gen_v8_0_11 #(

71 | .C_FAMILY("artix7"),

72 | .C_ADDR_WIDTH(10),

73 | .C_DEFAULT_DATA("0"),

74 | .C_DEPTH(1024),

75 | .C_HAS_CLK(1),

76 | .C_HAS_D(1),

77 | .C_HAS_DPO(0),

78 | .C_HAS_DPRA(0),

79 | .C_HAS_I_CE(0),

80 | .C_HAS_QDPO(0),

81 | .C_HAS_QDPO_CE(0),

82 | .C_HAS_QDPO_CLK(0),

83 | .C_HAS_QDPO_RST(0),

84 | .C_HAS_QDPO_SRST(0),

85 | .C_HAS_QSPO(0),

86 | .C_HAS_QSPO_CE(0),

87 | .C_HAS_QSPO_RST(0),

88 | .C_HAS_QSPO_SRST(0),

89 | .C_HAS_SPO(1),

90 | .C_HAS_WE(1),

91 | .C_MEM_INIT_FILE("data_memory_ip.mif"),

92 | .C_ELABORATION_DIR("./"),

93 | .C_MEM_TYPE(1),

94 | .C_PIPELINE_STAGES(0),

95 | .C_QCE_JOINED(0),

96 | .C_QUALIFY_WE(0),

97 | .C_READ_MIF(1),

98 | .C_REG_A_D_INPUTS(0),

99 | .C_REG_DPRA_INPUT(0),

100 | .C_SYNC_ENABLE(1),

101 | .C_WIDTH(32),

102 | .C_PARSER_TYPE(1)

103 | ) inst (

104 | .a(a),

105 | .d(d),

106 | .dpra(10'B0),

107 | .clk(clk),

108 | .we(we),

109 | .i_ce(1'D1),

110 | .qspo_ce(1'D1),

111 | .qdpo_ce(1'D1),

112 | .qdpo_clk(1'D0),

113 | .qspo_rst(1'D0),

114 | .qdpo_rst(1'D0),

115 | .qspo_srst(1'D0),

116 | .qdpo_srst(1'D0),

117 | .spo(spo),

118 | .dpo(),

119 | .qspo(),

120 | .qdpo()

121 | );

122 | endmodule

123 |

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/sources_1/ip/data_memory_ip/simulation/dist_mem_gen_v8_0.v:

--------------------------------------------------------------------------------

1 | /*

2 | *******************************************************************************

3 | *

4 | * Distributed Memory Generator - Verilog Behavioral Model

5 | *

6 | *******************************************************************************

7 | *

8 | * (c) Copyright 1995 - 2009 Xilinx, Inc. All rights reserved.

9 | *

10 | * This file contains confidential and proprietary information

11 | * of Xilinx, Inc. and is protected under U.S. and

12 | * international copyright and other intellectual property

13 | * laws.

14 | *

15 | * DISCLAIMER

16 | * This disclaimer is not a license and does not grant any

17 | * rights to the materials distributed herewith. Except as

18 | * otherwise provided in a valid license issued to you by

19 | * Xilinx, and to the maximum extent permitted by applicable

20 | * law: (1) THESE MATERIALS ARE MADE AVAILABLE "AS IS" AND

21 | * WITH ALL FAULTS, AND XILINX HEREBY DISCLAIMS ALL WARRANTIES

22 | * AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING

23 | * BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-

24 | * INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and

25 | * (2) Xilinx shall not be liable (whether in contract or tort,

26 | * including negligence, or under any other theory of

27 | * liability) for any loss or damage of any kind or nature

28 | * related to, arising under or in connection with these

29 | * materials, including for any direct, or any indirect,

30 | * special, incidental, or consequential loss or damage

31 | * (including loss of data, profits, goodwill, or any type of

32 | * loss or damage suffered as a result of any action brought

33 | * by a third party) even if such damage or loss was

34 | * reasonably foreseeable or Xilinx had been advised of the

35 | * possibility of the same.

36 | *

37 | * CRITICAL APPLICATIONS

38 | * Xilinx products are not designed or intended to be fail-

39 | * safe, or for use in any application requiring fail-safe

40 | * performance, such as life-support or safety devices or

41 | * systems, Class III medical devices, nuclear facilities,

42 | * applications related to the deployment of airbags, or any

43 | * other applications that could lead to death, personal

44 | * injury, or severe property or environmental damage

45 | * (individually and collectively, "Critical

46 | * Applications"). Customer assumes the sole risk and

47 | * liability of any use of Xilinx products in Critical

48 | * Applications, subject only to applicable laws and

49 | * regulations governing limitations on product liability.

50 | *

51 | * THIS COPYRIGHT NOTICE AND DISCLAIMER MUST BE RETAINED AS

52 | * PART OF THIS FILE AT ALL TIMES.

53 | *

54 | *******************************************************************************

55 | *******************************************************************************

56 | *

57 | * Filename : dist_mem_gen_v8_0_11.v

58 | *

59 | * Author : Xilinx

60 | *

61 | * Description : Distributed Memory Simulation Model

62 | *

63 | *******************************************************************************

64 | */

65 |

66 | `timescale 1ps/1ps

67 | `ifndef TCQ

68 | `define TCQ 100

69 | `endif

70 |

71 | `define all0s {C_WIDTH{1'b0}}

72 | `define allXs {C_WIDTH{1'bx}}

73 | `define c_rom 0

74 | `define c_sp_ram 1

75 | `define c_dp_ram 2

76 | `define c_sdp_ram 4

77 |

78 | module dist_mem_gen_v8_0_11 (a, d, dpra, clk, we, i_ce, qspo_ce, qdpo_ce, qdpo_clk, qspo_rst, qdpo_rst, qspo_srst, qdpo_srst, spo, dpo, qspo, qdpo);

79 |

80 | parameter C_FAMILY = "virtex5";

81 | parameter C_ADDR_WIDTH = 6;

82 | parameter C_DEFAULT_DATA = "0";

83 | parameter C_ELABORATION_DIR = "./";

84 | parameter C_DEPTH = 64;

85 | parameter C_HAS_CLK = 1;

86 | parameter C_HAS_D = 1;

87 | parameter C_HAS_DPO = 0;

88 | parameter C_HAS_DPRA = 0;

89 | parameter C_HAS_I_CE = 0;

90 | parameter C_HAS_QDPO = 0;

91 | parameter C_HAS_QDPO_CE = 0;

92 | parameter C_HAS_QDPO_CLK = 0;

93 | parameter C_HAS_QDPO_RST = 0;

94 | parameter C_HAS_QDPO_SRST = 0;

95 | parameter C_HAS_QSPO = 0;

96 | parameter C_HAS_QSPO_CE = 0;

97 | parameter C_HAS_QSPO_RST = 0;

98 | parameter C_HAS_QSPO_SRST = 0;

99 | parameter C_HAS_SPO = 1;

100 | parameter C_HAS_WE = 1;

101 | parameter C_MEM_INIT_FILE = "null.mif";

102 | parameter C_MEM_TYPE = 1;

103 | parameter C_PIPELINE_STAGES = 0;

104 | parameter C_QCE_JOINED = 0;

105 | parameter C_QUALIFY_WE = 0;

106 | parameter C_READ_MIF = 0;

107 | parameter C_REG_A_D_INPUTS = 0;

108 | parameter C_REG_DPRA_INPUT = 0;

109 | parameter C_SYNC_ENABLE = 0;

110 | parameter C_WIDTH = 16;

111 | parameter C_PARSER_TYPE = 1;

112 |

113 | input [C_ADDR_WIDTH-1:0] a;

114 | input [C_WIDTH-1 : 0] d;

115 | input [C_ADDR_WIDTH-1 : 0] dpra;

116 | input clk;

117 | input we;

118 | input i_ce;

119 | input qspo_ce;

120 | input qdpo_ce;

121 | input qdpo_clk;

122 | input qspo_rst;

123 | input qdpo_rst;

124 | input qspo_srst;

125 | input qdpo_srst;

126 | output [C_WIDTH-1 : 0] spo;

127 | output [C_WIDTH-1 : 0] qspo;

128 | output [C_WIDTH-1 : 0] dpo;

129 | output [C_WIDTH-1 : 0] qdpo;

130 |

131 | // Address signal connected to memory

132 | wire [C_ADDR_WIDTH - 1 : 0] a_int;

133 |

134 | // Input data signal connected to memory

135 | wire [C_WIDTH - 1 : 0] d_int;

136 |

137 | // Internal Write Enable

138 | wire we_int;

139 |

140 | // Internal QSPO Clock Enable

141 | wire qspo_ce_int;

142 |

143 | // Internal QDPO Clock

144 | wire qdpo_clk_int;

145 |

146 | // Internal Dual Port Read Address connected to memory

147 | wire [C_ADDR_WIDTH - 1 : 0] dpra_int;

148 |

149 | // Internal QDPO Clock Enable

150 | wire qdpo_ce_int;

151 |

152 | // Registered Write Enable

153 | reg we_reg;

154 |

155 | // Registered Address connected to memory

156 | reg [C_ADDR_WIDTH - 1 : 0] a_reg;

157 |

158 | // Registered data signal connected to memory

159 | reg [C_WIDTH-1 : 0] d_reg;

160 |

161 | // Registered QSPO Clock Enable

162 | reg qspo_ce_reg;

163 |

164 | // Registered Dual Port Read Address connected to memory

165 | reg [C_ADDR_WIDTH - 1 : 0] dpra_reg;

166 |

167 | // Registered QDPO Clock Enable

168 | reg qdpo_ce_reg;

169 |

170 | // Internal Single Port RAM output signal

171 | wire [C_WIDTH - 1 : 0] spo_int;

172 |

173 | // Internal Dual Port RAM output signal

174 | wire [C_WIDTH - 1 : 0] dpo_int;

175 |

176 | // Internal ROM/Single Port RAM

177 | // registered output

178 | reg [C_WIDTH - 1 : 0] qspo_int;

179 |

180 | // Pipeline registers

181 | reg [C_WIDTH - 1 : 0] qspo_pipe;

182 |

183 | // Internal Dual Port RAM registered output

184 | reg [C_WIDTH - 1 : 0] qdpo_int;

185 |

186 | // Pipeline registers

187 | reg [C_WIDTH - 1 : 0] qdpo_pipe;

188 |

189 | reg [C_WIDTH-1 : 0] ram_data [(2**C_ADDR_WIDTH)-1 : 0];

190 | reg [C_WIDTH-1 : 0] ram_data_tmp[C_DEPTH-1 : 0];

191 |

192 |

193 | reg [C_WIDTH-1 : 0] default_data;

194 |

195 | wire [C_WIDTH-1 : 0] data_sp;

196 | wire [C_WIDTH-1 : 0] data_dp;

197 |

198 | wire [C_WIDTH-1 : 0] data_sp_over;

199 | wire [C_WIDTH-1 : 0] data_dp_over;

200 |

201 | wire [C_ADDR_WIDTH - 1 : 0] a_over;

202 | wire [C_ADDR_WIDTH - 1 : 0] dpra_over;

203 |

204 | wire a_is_over;

205 | wire dpra_is_over;

206 |

207 | reg [C_ADDR_WIDTH-1 : 0] max_address;

208 |

209 | integer i;

210 | integer j;

211 |

212 |

213 | // Initial block - initialise the memory,

214 | // and when appropriate write content into the given address.

215 | initial

216 | begin

217 | $display("WARNING: This core is supplied with a behavioral model. To model cycle-accurate behavior you must run timing simulation.");

218 |

219 |

220 | default_data = 'b0;

221 | default_data = binstr_conv(C_DEFAULT_DATA);

222 |

223 | // Assign that C_DEFAULT_DATA to each address in the memory.

224 | for (i = 0; i < C_DEPTH; i = i + 1)

225 | begin

226 | ram_data[i] = default_data;

227 | ram_data_tmp[i] = default_data;

228 | end

229 |

230 | //Read the MIF file, and use it to initialise the content of ram_data

231 | //if that is required.

232 | if (C_READ_MIF)

233 | begin

234 | $readmemb(C_MEM_INIT_FILE, ram_data_tmp, 0, C_DEPTH-1);

235 |

236 | for (i = 0; i < C_DEPTH; i = i + 1)

237 | ram_data[i] = ram_data_tmp[i];

238 |

239 | end

240 |

241 | if (C_DEPTH != (2**C_ADDR_WIDTH))

242 | begin

243 | for (i = C_DEPTH; i < (2**C_ADDR_WIDTH); i = i + 1)

244 | ram_data[i] = 'b0;

245 | end

246 |

247 | a_reg = 'b0;

248 | we_reg = 1'b0;

249 | d_reg = 'b0;

250 | qspo_ce_reg = 1'b0;

251 | dpra_reg = 'b0;

252 | qdpo_ce_reg = 1'b0;

253 |

254 | qspo_int = default_data;

255 | qspo_pipe = 'b0;

256 | qdpo_int = default_data;

257 | qdpo_pipe = 'b0;

258 |

259 | max_address = C_DEPTH-1;

260 |

261 |

262 | end // initial begin

263 |

264 | // Now look for writes to the memory (note that this means the

265 | // memory is not a ROM and that the Write Enable WE is active.

266 | always@(posedge clk)

267 | begin

268 | if (C_MEM_TYPE != `c_rom && we_int)

269 | begin

270 | if (a_is_over)

271 | begin

272 | $display("WARNING in %m at time %d ns", $time);

273 | $write("Writing to out of range address. ");

274 | $display("Max address in %m is %d", C_DEPTH-1);

275 | $display("Write will be ignored.");

276 | end

277 | else

278 | ram_data[a_int] <= #`TCQ d_int;

279 | end // if (C_MEM_TYPE != `c_rom && we_int)

280 | end // always@ (posedge CLK)

281 |

282 | // Model optional input registers, which operate in the CLK clock domain.

283 | always @(posedge clk)

284 | begin

285 | if (C_MEM_TYPE == 0) begin // ROM

286 | if (C_HAS_QSPO_CE == 1) begin

287 | if (qspo_ce == 1)

288 | a_reg <= #`TCQ a;

289 | end else

290 | a_reg <= #`TCQ a;

291 | end else if (!C_HAS_I_CE)

292 | begin

293 | we_reg <= #`TCQ we;

294 | a_reg <= #`TCQ a;

295 | d_reg <= #`TCQ d;

296 | end

297 | else if (!C_QUALIFY_WE)

298 | begin

299 | we_reg <= #`TCQ we;

300 | if (i_ce)

301 | begin

302 | a_reg <= #`TCQ a;

303 | d_reg <= #`TCQ d;

304 | end

305 | end

306 | else if (C_QUALIFY_WE)

307 | if (i_ce)

308 | begin

309 | we_reg <= #`TCQ we;

310 | a_reg <= #`TCQ a;

311 | d_reg <= #`TCQ d;

312 | end

313 |

314 | qspo_ce_reg <= #`TCQ qspo_ce;

315 | end // always @ (posedge CLK)

316 |

317 |

318 | assign we_int = (C_HAS_WE ? (C_REG_A_D_INPUTS ? we_reg : we) : 1'b0);

319 | assign d_int = (C_MEM_TYPE > 0 ? (C_REG_A_D_INPUTS ? d_reg : d) : 'b0);

320 | assign a_int = (C_REG_A_D_INPUTS ? a_reg : a);

321 |

322 | assign qspo_ce_int = (C_HAS_QSPO_CE ? (C_REG_A_D_INPUTS ? qspo_ce_reg : qspo_ce) : 1'b0);

323 |

324 | assign qdpo_clk_int = (((C_MEM_TYPE == `c_dp_ram) || (C_MEM_TYPE == `c_sdp_ram)) ?

325 | (C_HAS_QDPO_CLK == 1 ? qdpo_clk : clk) : 1'b0);

326 |

327 | always@(posedge qdpo_clk_int)

328 | begin

329 | if (C_QCE_JOINED)

330 | begin

331 | if (!C_HAS_QSPO_CE)

332 | dpra_reg <= #`TCQ dpra;

333 | else if (qspo_ce)

334 | dpra_reg <= #`TCQ dpra;

335 | end

336 | else

337 | begin

338 | if (!C_HAS_QDPO_CE)

339 | dpra_reg <= #`TCQ dpra;

340 | else if (qdpo_ce)

341 | dpra_reg <= #`TCQ dpra;

342 | end // else: !if(C_QCE_JOINED)

343 |

344 | qdpo_ce_reg <= #`TCQ qdpo_ce;

345 |

346 | end // always@ (posedge qdpo_clk_int)

347 |

348 | assign dpra_int = (((C_MEM_TYPE == `c_dp_ram) || (C_MEM_TYPE == `c_sdp_ram)) ?

349 | (C_REG_DPRA_INPUT == 1 ? dpra_reg : dpra) : 1'b0);

350 |

351 | assign qdpo_ce_int = (((C_MEM_TYPE == `c_dp_ram) || (C_MEM_TYPE == `c_sdp_ram)) ?

352 | (C_HAS_QDPO_CE ? (C_REG_DPRA_INPUT ? qdpo_ce_reg : qdpo_ce) : 1'b0) : 1'b0);

353 |

354 | always@(posedge a_is_over)

355 | begin

356 | $display("WARNING in %m at time %d ns: ", $time);

357 | $write("Reading from out-of-range address. ");

358 | $display("Max address in %m is %d", C_DEPTH-1);

359 | end // always@ (a_int or posedge CLK)

360 |

361 | assign spo = (C_HAS_SPO ? spo_int : `allXs);

362 |

363 | always@(posedge dpra_is_over)

364 | begin

365 | if ((C_MEM_TYPE == `c_dp_ram) || (C_MEM_TYPE == `c_sdp_ram))

366 | begin

367 | $display("WARNING in %m at time %d ns: ", $time);

368 | $write("Reading from out-of-range address. ");

369 | $display("Max address in %m is %d", C_DEPTH-1);

370 | end // if (C_MEM_TYPE == `c_dp_ram)

371 | end // always@ (dpra_int)

372 |

373 | assign spo_int = (a_is_over ? data_sp_over : data_sp);

374 |

375 | assign dpo_int = (((C_MEM_TYPE == `c_dp_ram) || (C_MEM_TYPE == `c_sdp_ram)) ? (dpra_is_over ? data_dp_over : data_dp) : `allXs);

376 |

377 | assign data_sp = ram_data[a_int];

378 | assign data_dp = ram_data[dpra_int];

379 |

380 | assign a_is_over = (a_int > max_address ? 1'b1 : 1'b0);

381 | assign dpra_is_over = (dpra_int > max_address ? 1'b1 : 1'b0);

382 |

383 | assign a_over = a_int & max_address;

384 | assign dpra_over = dpra_int & max_address;

385 |

386 | assign data_sp_over = 'bx;

387 | assign data_dp_over = 'bx;

388 |

389 | assign dpo = (C_HAS_DPO ? dpo_int : `allXs);

390 |

391 | always@(posedge clk or posedge qspo_rst)

392 | begin

393 | if (C_HAS_QSPO_RST && qspo_rst)

394 | begin

395 | qspo_pipe <= 'b0;

396 | qspo_int <= 'b0;

397 | end

398 | else if (C_HAS_QSPO_SRST && qspo_srst)

399 | begin

400 | if (!C_HAS_QSPO_CE)

401 | begin

402 | qspo_pipe <= #`TCQ 'b0;

403 | qspo_int <= #`TCQ 'b0;

404 | end

405 | else if (!C_SYNC_ENABLE)

406 | begin

407 | qspo_pipe <= #`TCQ 'b0;

408 | qspo_int <= #`TCQ 'b0;

409 | end

410 | else if (C_HAS_QSPO_CE && qspo_ce_int)

411 | begin

412 | qspo_pipe <= #`TCQ 'b0;

413 | qspo_int <= #`TCQ 'b0;

414 | end

415 | end // if (C_HAS_QSPO_SRST && QSPO_SRST)

416 |

417 | else if (C_HAS_QSPO_CE && qspo_ce_int)

418 | begin

419 | if (C_PIPELINE_STAGES == 1)

420 | begin

421 | qspo_int <= #`TCQ qspo_pipe;

422 | end

423 | else

424 | begin

425 | qspo_int <= #`TCQ spo_int;

426 | end

427 | qspo_pipe <= #`TCQ spo_int;

428 | end

429 | else if (!C_HAS_QSPO_CE)

430 | begin

431 | if (C_PIPELINE_STAGES == 1)

432 | begin

433 | qspo_int <= #`TCQ qspo_pipe;

434 | end

435 | else

436 | begin

437 | qspo_int <= #`TCQ spo_int;

438 | end

439 | qspo_pipe <= #`TCQ spo_int;

440 | end // if (!C_HAS_QSPO_CE)

441 | end // always@ (posedge CLK or QSPO_RST)

442 |

443 | assign qspo = (C_HAS_QSPO == 1 ? qspo_int : `allXs);

444 |

445 | always@(posedge qdpo_clk_int or posedge qdpo_rst)

446 | begin

447 | if (C_HAS_QDPO_RST && qdpo_rst)

448 | begin

449 | qdpo_pipe <= 'b0;

450 | qdpo_int <= 'b0;

451 | end

452 | else if (C_HAS_QDPO_SRST && qdpo_srst)

453 | begin

454 | if (!C_SYNC_ENABLE)

455 | begin

456 | qdpo_pipe <= #`TCQ 'b0;

457 | qdpo_int <= #`TCQ 'b0;

458 | end

459 | else if (!C_QCE_JOINED)

460 | begin

461 | if (!C_HAS_QDPO_CE)

462 | begin

463 | qdpo_pipe <= #`TCQ 'b0;

464 | qdpo_int <= #`TCQ 'b0;

465 | end

466 | else if (C_HAS_QDPO_CE && qdpo_ce_int)

467 | begin

468 | qdpo_pipe <= #`TCQ 'b0;

469 | qdpo_int <= #`TCQ 'b0;

470 | end

471 | end

472 | else

473 | begin

474 | if (!C_HAS_QSPO_CE)

475 | begin

476 | qdpo_pipe <= #`TCQ 'b0;

477 | qdpo_int <= #`TCQ 'b0;

478 | end

479 | else if (C_HAS_QSPO_CE && qspo_ce_int)

480 | begin

481 | qdpo_pipe <= #`TCQ 'b0;

482 | qdpo_int <= #`TCQ 'b0;

483 | end

484 | end

485 | end // if (C_HAS_QDPO_SRST && QDPO_SRST)

486 |

487 | else if (!C_QCE_JOINED)

488 | begin

489 | if (!C_HAS_QDPO_CE)

490 | begin

491 | qdpo_pipe <= #`TCQ dpo_int;

492 | if (C_PIPELINE_STAGES == 1)

493 | begin

494 | qdpo_int <= #`TCQ qdpo_pipe;

495 | end

496 | else

497 | begin

498 | qdpo_int <= #`TCQ dpo_int;

499 | end

500 | end // if (!C_HAS_QDPO_CE)

501 | else if (C_HAS_QDPO_CE && qdpo_ce_int)

502 | begin

503 | qdpo_pipe <= #`TCQ dpo_int;

504 | if (C_PIPELINE_STAGES == 1)

505 | begin

506 | qdpo_int <= #`TCQ qdpo_pipe;

507 | end

508 | else

509 | begin

510 | qdpo_int <= #`TCQ dpo_int;

511 | end

512 | end // if (C_HAS_QDPO_CE && qdpo_ce_int)

513 | end // if (!C_QCE_JOINED)

514 | else if (C_QCE_JOINED)

515 | begin

516 | if (C_HAS_QSPO_CE && qspo_ce_int)

517 | begin

518 | qdpo_pipe <= #`TCQ dpo_int;

519 | if (C_PIPELINE_STAGES == 1)

520 | begin

521 | qdpo_int <= #`TCQ qdpo_pipe;

522 | end

523 | else

524 | begin

525 | qdpo_int <= #`TCQ dpo_int;

526 | end

527 | end // if (C_HAS_QSPO_CE && qspo_ce_int)

528 | else if (!C_HAS_QSPO_CE)

529 | begin

530 | qdpo_pipe <= #`TCQ dpo_int;

531 | if (C_PIPELINE_STAGES == 1)

532 | begin

533 | qdpo_int <= #`TCQ qdpo_pipe;

534 | end

535 | else

536 | begin

537 | qdpo_int <= #`TCQ dpo_int;

538 | end

539 | end // if (!C_HAS_QSPO_CE)

540 | end // if (C_QCE_JOINED)

541 | end // always@ (posedge qdpo_clk_int or posedge QDPO_RST)

542 |

543 | assign qdpo = (C_HAS_QDPO == 1 ? qdpo_int : `allXs);

544 |

545 | function [C_WIDTH - 1 : 0] binstr_conv;

546 | input [(C_WIDTH * 8) - 1 : 0] def_data;

547 | integer index,i;

548 | begin

549 | index = 0;

550 | binstr_conv = 'b0;

551 |

552 | for (i=C_WIDTH-1; i>=0; i=i-1)

553 | begin

554 | case (def_data[7:0])

555 | 8'b00000000 : i = -1;

556 | 8'b00110000 : binstr_conv[index] = 1'b0;

557 | 8'b00110001 : binstr_conv[index] = 1'b1;

558 | default :

559 | begin

560 | $display("ERROR in %m at time %d ns: NOT A BINARY CHARACTER", $time);

561 | binstr_conv[index] = 1'bx;

562 | end

563 | endcase // case(def_data[7:0])

564 |

565 | index = index + 1;

566 | def_data = def_data >> 8;

567 | end // for (i=C_WIDTH-1; i>=0; i=i-1)

568 |

569 | end

570 | endfunction // binstr_conv

571 |

572 | endmodule // dist_mem_gen_v8_0_11

573 |

574 | `undef all0s

575 | `undef allXs

576 | `undef c_rom

577 | `undef c_sp_ram

578 | `undef c_dp_ram

579 | `undef c_sdp_ram

580 |

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/sources_1/ip/data_memory_ip/synth/data_memory_ip.vhd:

--------------------------------------------------------------------------------

1 | -- (c) Copyright 1995-2019 Xilinx, Inc. All rights reserved.

2 | --

3 | -- This file contains confidential and proprietary information

4 | -- of Xilinx, Inc. and is protected under U.S. and

5 | -- international copyright and other intellectual property

6 | -- laws.

7 | --

8 | -- DISCLAIMER

9 | -- This disclaimer is not a license and does not grant any

10 | -- rights to the materials distributed herewith. Except as

11 | -- otherwise provided in a valid license issued to you by

12 | -- Xilinx, and to the maximum extent permitted by applicable

13 | -- law: (1) THESE MATERIALS ARE MADE AVAILABLE "AS IS" AND

14 | -- WITH ALL FAULTS, AND XILINX HEREBY DISCLAIMS ALL WARRANTIES

15 | -- AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING

16 | -- BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-

17 | -- INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and

18 | -- (2) Xilinx shall not be liable (whether in contract or tort,

19 | -- including negligence, or under any other theory of

20 | -- liability) for any loss or damage of any kind or nature

21 | -- related to, arising under or in connection with these

22 | -- materials, including for any direct, or any indirect,

23 | -- special, incidental, or consequential loss or damage

24 | -- (including loss of data, profits, goodwill, or any type of

25 | -- loss or damage suffered as a result of any action brought

26 | -- by a third party) even if such damage or loss was

27 | -- reasonably foreseeable or Xilinx had been advised of the

28 | -- possibility of the same.

29 | --

30 | -- CRITICAL APPLICATIONS

31 | -- Xilinx products are not designed or intended to be fail-

32 | -- safe, or for use in any application requiring fail-safe

33 | -- performance, such as life-support or safety devices or

34 | -- systems, Class III medical devices, nuclear facilities,

35 | -- applications related to the deployment of airbags, or any

36 | -- other applications that could lead to death, personal

37 | -- injury, or severe property or environmental damage

38 | -- (individually and collectively, "Critical

39 | -- Applications"). Customer assumes the sole risk and

40 | -- liability of any use of Xilinx products in Critical

41 | -- Applications, subject only to applicable laws and

42 | -- regulations governing limitations on product liability.

43 | --

44 | -- THIS COPYRIGHT NOTICE AND DISCLAIMER MUST BE RETAINED AS

45 | -- PART OF THIS FILE AT ALL TIMES.

46 | --

47 | -- DO NOT MODIFY THIS FILE.

48 |

49 | -- IP VLNV: xilinx.com:ip:dist_mem_gen:8.0

50 | -- IP Revision: 11

51 |

52 | LIBRARY ieee;

53 | USE ieee.std_logic_1164.ALL;

54 | USE ieee.numeric_std.ALL;

55 |

56 | LIBRARY dist_mem_gen_v8_0_11;

57 | USE dist_mem_gen_v8_0_11.dist_mem_gen_v8_0_11;

58 |

59 | ENTITY data_memory_ip IS

60 | PORT (

61 | a : IN STD_LOGIC_VECTOR(9 DOWNTO 0);

62 | d : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

63 | clk : IN STD_LOGIC;

64 | we : IN STD_LOGIC;

65 | spo : OUT STD_LOGIC_VECTOR(31 DOWNTO 0)

66 | );

67 | END data_memory_ip;

68 |

69 | ARCHITECTURE data_memory_ip_arch OF data_memory_ip IS

70 | ATTRIBUTE DowngradeIPIdentifiedWarnings : STRING;

71 | ATTRIBUTE DowngradeIPIdentifiedWarnings OF data_memory_ip_arch: ARCHITECTURE IS "yes";

72 | COMPONENT dist_mem_gen_v8_0_11 IS

73 | GENERIC (

74 | C_FAMILY : STRING;

75 | C_ADDR_WIDTH : INTEGER;

76 | C_DEFAULT_DATA : STRING;

77 | C_DEPTH : INTEGER;

78 | C_HAS_CLK : INTEGER;

79 | C_HAS_D : INTEGER;

80 | C_HAS_DPO : INTEGER;

81 | C_HAS_DPRA : INTEGER;

82 | C_HAS_I_CE : INTEGER;

83 | C_HAS_QDPO : INTEGER;

84 | C_HAS_QDPO_CE : INTEGER;

85 | C_HAS_QDPO_CLK : INTEGER;

86 | C_HAS_QDPO_RST : INTEGER;

87 | C_HAS_QDPO_SRST : INTEGER;

88 | C_HAS_QSPO : INTEGER;

89 | C_HAS_QSPO_CE : INTEGER;

90 | C_HAS_QSPO_RST : INTEGER;

91 | C_HAS_QSPO_SRST : INTEGER;

92 | C_HAS_SPO : INTEGER;

93 | C_HAS_WE : INTEGER;

94 | C_MEM_INIT_FILE : STRING;

95 | C_ELABORATION_DIR : STRING;

96 | C_MEM_TYPE : INTEGER;

97 | C_PIPELINE_STAGES : INTEGER;

98 | C_QCE_JOINED : INTEGER;

99 | C_QUALIFY_WE : INTEGER;

100 | C_READ_MIF : INTEGER;

101 | C_REG_A_D_INPUTS : INTEGER;

102 | C_REG_DPRA_INPUT : INTEGER;

103 | C_SYNC_ENABLE : INTEGER;

104 | C_WIDTH : INTEGER;

105 | C_PARSER_TYPE : INTEGER

106 | );

107 | PORT (

108 | a : IN STD_LOGIC_VECTOR(9 DOWNTO 0);

109 | d : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

110 | dpra : IN STD_LOGIC_VECTOR(9 DOWNTO 0);

111 | clk : IN STD_LOGIC;

112 | we : IN STD_LOGIC;

113 | i_ce : IN STD_LOGIC;

114 | qspo_ce : IN STD_LOGIC;

115 | qdpo_ce : IN STD_LOGIC;

116 | qdpo_clk : IN STD_LOGIC;

117 | qspo_rst : IN STD_LOGIC;

118 | qdpo_rst : IN STD_LOGIC;

119 | qspo_srst : IN STD_LOGIC;

120 | qdpo_srst : IN STD_LOGIC;

121 | spo : OUT STD_LOGIC_VECTOR(31 DOWNTO 0);

122 | dpo : OUT STD_LOGIC_VECTOR(31 DOWNTO 0);

123 | qspo : OUT STD_LOGIC_VECTOR(31 DOWNTO 0);

124 | qdpo : OUT STD_LOGIC_VECTOR(31 DOWNTO 0)

125 | );

126 | END COMPONENT dist_mem_gen_v8_0_11;

127 | ATTRIBUTE X_CORE_INFO : STRING;

128 | ATTRIBUTE X_CORE_INFO OF data_memory_ip_arch: ARCHITECTURE IS "dist_mem_gen_v8_0_11,Vivado 2017.2";

129 | ATTRIBUTE CHECK_LICENSE_TYPE : STRING;

130 | ATTRIBUTE CHECK_LICENSE_TYPE OF data_memory_ip_arch : ARCHITECTURE IS "data_memory_ip,dist_mem_gen_v8_0_11,{}";

131 | ATTRIBUTE CORE_GENERATION_INFO : STRING;

132 | ATTRIBUTE CORE_GENERATION_INFO OF data_memory_ip_arch: ARCHITECTURE IS "data_memory_ip,dist_mem_gen_v8_0_11,{x_ipProduct=Vivado 2017.2,x_ipVendor=xilinx.com,x_ipLibrary=ip,x_ipName=dist_mem_gen,x_ipVersion=8.0,x_ipCoreRevision=11,x_ipLanguage=VERILOG,x_ipSimLanguage=MIXED,C_FAMILY=artix7,C_ADDR_WIDTH=10,C_DEFAULT_DATA=0,C_DEPTH=1024,C_HAS_CLK=1,C_HAS_D=1,C_HAS_DPO=0,C_HAS_DPRA=0,C_HAS_I_CE=0,C_HAS_QDPO=0,C_HAS_QDPO_CE=0,C_HAS_QDPO_CLK=0,C_HAS_QDPO_RST=0,C_HAS_QDPO_SRST=0,C_HAS_QSPO=0,C_HAS_QSPO_CE=0,C_HAS_QSPO_RST=0,C_HAS_QSPO_SRST=0,C_HAS_SPO=1,C_HAS_WE=1,C_MEM_INI" &

133 | "T_FILE=data_memory_ip.mif,C_ELABORATION_DIR=./,C_MEM_TYPE=1,C_PIPELINE_STAGES=0,C_QCE_JOINED=0,C_QUALIFY_WE=0,C_READ_MIF=1,C_REG_A_D_INPUTS=0,C_REG_DPRA_INPUT=0,C_SYNC_ENABLE=1,C_WIDTH=32,C_PARSER_TYPE=1}";

134 | BEGIN

135 | U0 : dist_mem_gen_v8_0_11

136 | GENERIC MAP (

137 | C_FAMILY => "artix7",

138 | C_ADDR_WIDTH => 10,

139 | C_DEFAULT_DATA => "0",

140 | C_DEPTH => 1024,

141 | C_HAS_CLK => 1,

142 | C_HAS_D => 1,

143 | C_HAS_DPO => 0,

144 | C_HAS_DPRA => 0,

145 | C_HAS_I_CE => 0,

146 | C_HAS_QDPO => 0,

147 | C_HAS_QDPO_CE => 0,

148 | C_HAS_QDPO_CLK => 0,

149 | C_HAS_QDPO_RST => 0,

150 | C_HAS_QDPO_SRST => 0,

151 | C_HAS_QSPO => 0,

152 | C_HAS_QSPO_CE => 0,

153 | C_HAS_QSPO_RST => 0,

154 | C_HAS_QSPO_SRST => 0,

155 | C_HAS_SPO => 1,

156 | C_HAS_WE => 1,

157 | C_MEM_INIT_FILE => "data_memory_ip.mif",

158 | C_ELABORATION_DIR => "./",

159 | C_MEM_TYPE => 1,

160 | C_PIPELINE_STAGES => 0,

161 | C_QCE_JOINED => 0,

162 | C_QUALIFY_WE => 0,

163 | C_READ_MIF => 1,

164 | C_REG_A_D_INPUTS => 0,

165 | C_REG_DPRA_INPUT => 0,

166 | C_SYNC_ENABLE => 1,

167 | C_WIDTH => 32,

168 | C_PARSER_TYPE => 1

169 | )

170 | PORT MAP (

171 | a => a,

172 | d => d,

173 | dpra => STD_LOGIC_VECTOR(TO_UNSIGNED(0, 10)),

174 | clk => clk,

175 | we => we,

176 | i_ce => '1',

177 | qspo_ce => '1',

178 | qdpo_ce => '1',

179 | qdpo_clk => '0',

180 | qspo_rst => '0',

181 | qdpo_rst => '0',

182 | qspo_srst => '0',

183 | qdpo_srst => '0',

184 | spo => spo

185 | );

186 | END data_memory_ip_arch;

187 |

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/sources_1/ip/instruction_memory_ip/doc/dist_mem_gen_v8_0_changelog.txt:

--------------------------------------------------------------------------------

1 | 2017.2:

2 | * Version 8.0 (Rev. 11)

3 | * No changes

4 |

5 | 2017.1:

6 | * Version 8.0 (Rev. 11)

7 | * No changes

8 |

9 | 2016.4:

10 | * Version 8.0 (Rev. 11)

11 | * No changes

12 |

13 | 2016.3:

14 | * Version 8.0 (Rev. 11)

15 | * General: Enable support for future devices

16 |

17 | 2016.2:

18 | * Version 8.0 (Rev. 10)

19 | * No changes

20 |

21 | 2016.1:

22 | * Version 8.0 (Rev. 10)

23 | * Delivering only verilog simulation model, Stopped delivery of vhdl simulation model.

24 |

25 | 2015.4.2:

26 | * Version 8.0 (Rev. 9)

27 | * No changes

28 |

29 | 2015.4.1:

30 | * Version 8.0 (Rev. 9)

31 | * No changes

32 |

33 | 2015.4:

34 | * Version 8.0 (Rev. 9)

35 | * No changes

36 |

37 | 2015.3:

38 | * Version 8.0 (Rev. 9)

39 | * Delivering only vhdl simulation model, Stopped delivery of verilog simulation model.

40 | * IP revision number added to HDL module, library, and include file names, to support designs with both locked and upgraded IP instances

41 |

42 | 2015.2.1:

43 | * Version 8.0 (Rev. 8)

44 | * No changes

45 |

46 | 2015.2:

47 | * Version 8.0 (Rev. 8)

48 | * No changes

49 |

50 | 2015.1:

51 | * Version 8.0 (Rev. 8)

52 | * Delivering unencrypted simulation files.

53 | * Supported devices and production status are now determined automatically, to simplify support for future devices

54 |

55 | 2014.4.1:

56 | * Version 8.0 (Rev. 7)

57 | * No changes

58 |

59 | 2014.4:

60 | * Version 8.0 (Rev. 7)

61 | * Encrypted source files are concatenated together to reduce the number of files and to reduce simulator compile time

62 | * Internal device family change, no functional changes

63 |

64 | 2014.3:

65 | * Version 8.0 (Rev. 6)

66 | * Reduced warnings in synthesis, no functional changes

67 |

68 | 2014.2:

69 | * Version 8.0 (Rev. 5)

70 | * Repackaged to improve internal automation, no functional changes.

71 |

72 | 2014.1:

73 | * Version 8.0 (Rev. 4)

74 | * Internal device family name change, no functional changes

75 |

76 | 2013.4:

77 | * Version 8.0 (Rev. 3)

78 | * Added support for Ultrascale devices

79 |

80 | 2013.3:

81 | * Version 8.0 (Rev. 2)

82 | * Enhanced support for IP Integrator

83 | * Reduced warnings in synthesis and simulation

84 | * Added support for Cadence IES and Synopsys VCS simulators

85 |

86 | 2013.2:

87 | * Version 8.0 (Rev. 1)

88 | * Repackaged to enable internal version management, no functional changes.

89 |

90 | 2013.1:

91 | * Version 8.0

92 | * Native Vivado Release

93 | * Unused port SPRA and its associated parameters removed.

94 |

95 | (c) Copyright 2002 - 2017 Xilinx, Inc. All rights reserved.

96 |

97 | This file contains confidential and proprietary information

98 | of Xilinx, Inc. and is protected under U.S. and

99 | international copyright and other intellectual property

100 | laws.

101 |

102 | DISCLAIMER

103 | This disclaimer is not a license and does not grant any

104 | rights to the materials distributed herewith. Except as

105 | otherwise provided in a valid license issued to you by

106 | Xilinx, and to the maximum extent permitted by applicable

107 | law: (1) THESE MATERIALS ARE MADE AVAILABLE "AS IS" AND

108 | WITH ALL FAULTS, AND XILINX HEREBY DISCLAIMS ALL WARRANTIES

109 | AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING

110 | BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-

111 | INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and

112 | (2) Xilinx shall not be liable (whether in contract or tort,

113 | including negligence, or under any other theory of

114 | liability) for any loss or damage of any kind or nature

115 | related to, arising under or in connection with these

116 | materials, including for any direct, or any indirect,

117 | special, incidental, or consequential loss or damage

118 | (including loss of data, profits, goodwill, or any type of

119 | loss or damage suffered as a result of any action brought

120 | by a third party) even if such damage or loss was

121 | reasonably foreseeable or Xilinx had been advised of the

122 | possibility of the same.

123 |

124 | CRITICAL APPLICATIONS

125 | Xilinx products are not designed or intended to be fail-

126 | safe, or for use in any application requiring fail-safe

127 | performance, such as life-support or safety devices or

128 | systems, Class III medical devices, nuclear facilities,

129 | applications related to the deployment of airbags, or any

130 | other applications that could lead to death, personal

131 | injury, or severe property or environmental damage

132 | (individually and collectively, "Critical

133 | Applications"). Customer assumes the sole risk and

134 | liability of any use of Xilinx products in Critical

135 | Applications, subject only to applicable laws and

136 | regulations governing limitations on product liability.

137 |

138 | THIS COPYRIGHT NOTICE AND DISCLAIMER MUST BE RETAINED AS

139 | PART OF THIS FILE AT ALL TIMES.

140 |

--------------------------------------------------------------------------------

/single-cycle-cpu.srcs/sources_1/ip/instruction_memory_ip/instruction_memory_ip.dcp:

--------------------------------------------------------------------------------